Устройство для пространственновременной коммутации асинхронных цифровых сигналов

Иллюстрации

Показать всеРеферат

Союз Советскмн

Соцмалистическин

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДИЕЛЬСТВУ (6l) Дополнительное к авт. свид-ву (22) 3аявлено 05.04.77(21} 2470819/18-0 с присоединением заявки № (23) Приоритет

Гоаударетвнннмй комитет

СССР оо делом нзобретеннй н аткрьинй

Опубликовано15.03.79,Бюллетень % 1

Дата опубликования описания 18.03.7 (У2) Авторы изобретения

В. П. Чуркин, А. A. Беличенко, В. J1 Гординов и 10. К. Яковлев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРОСТРАНСТВЕННО-ВРЕМЕННОЙ

КОММУТАБИИ АСИНХРОННЫХ БИФРОВЫХ СИГНАЛОВ

Изобретение относится к связи и мох жет быть использовано в системах для цифровой коммутации асинхройных сит налов телефонного (ТЛФ) и телеграфного (ТЛГ) типа.

Известно устройство пространственно» временной коммутации асинхронных цифровых сигналов, содержащее входные регистры, выходы которых подключены к входам блока первичной памяти, а также блок вторичной памяти, дешифратор, счет 1О чик тактов и блоки выдачи сигналов Щ .

Однако известное устройство при про странственно-временной коммутации асин-. хронных цифровых сигналов имеет низкую пропускную способность в связи с тем, что асинхронные цифровые сигналы непрерывно смещаются относительно Временных позипий магистралей.

Белью изобретения является повышение пропускной способности устройства.

26

Для sTopo s tpoAcTBo для простран ственно-временной коммутации асинхронных цифровых сигналов, содлржащее входные регистры, выходы которых подключены к входам блока первичной памяти, а также блок вторичной памяти, дешифратор, счетчик тактов,и блоки выдачи сигналов, введены последовательно соединенные формирователь кодов времени и блок срав-. нения, а также блок блокировки записи, при этом выход блока первичной памяти подюпочен к первому входу блока вторичной памяти, первый выход которого подключен к другому входу блока сравнения, второй выход подключен к первому входу дешифратора, а третий и четвертый выходы подключены к входам блоков sbiдачи сигналов, выходы которых через блок блокировки записи подключены к второму входу блока вторичной памяти, выход блока сравнения подключен и второму входу дешнфратора, выходы которого подключены к входам соответствующих блоков выдачи сигналов.

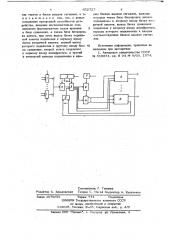

На чертеже приведена структурная электрическая схема устройства.

052727

Устройство для пространственно-временной коммутации асинхронных цифровых сигналов содержит входные регистры 1, выходы которых подключены к входам блока 2 первичной памяти, блок 3 вторич- 5 ной памяти, дешифратор 4, счетчик тактов 5, блоки 6, предназначенные для выдачи сигналов, последовательно соединенные формирователь 7 кодов време-. ни и блок сравнения 8, а также блок 9 10 блокировки запи и, при этом выход блока 2 подключен к первому входу блока

3, первый выход которого подключен к другому входу блока сравнения 8, второй выход подключен к первому входу

15 дешифратора 4, а третий и четвертый выходы подключены к входам блоков 6, выходы которых через блок 9 подключены к второму входу блока 3, выход блока сравнения 8 подключен к второму входу

20 дешифратора 4, выходы которого подключены к входам соответствующих блоков 6.

Устройство работает следующим об- разом.

По входным адресно-информационным магистралям (АИМ) параллельным кодом поступает информации в соцровождении адресов (номеров) исходящих линий связи, которым эта информация принадлежит. Информация представляет, собой коды фронтов коммутируемых сит г . налов и коц времени„опрецеляющнймомен I ты времени выдачи сигналов в исходящие линии связи. При этом кодом "1" кодируется передний фронт сигнала, а кодом О" - задний фронт.

Адресно-информационные слова зацисываются на входные регистры 1. Считывание этих слов из регистров 1 и зацись информации в блок 2 первичной памяти произвоцится поочередно с помощьтт тактовых импульсов Ь; (i = 1. 2, ..., m, где rn - количество АИМ). За каждый такт t обслуживается один входной регистр 1.

Блок 2 принимает слова и, используя адрес линий связи, записывает информацию в соответствующие ячейки. При этом . каждая линия связи имеет свою ячейку в блоках 2 и 3. Номера линий связи и ячеек совпадают.

Далее с помощью счетчика тактов

5 информация циклически считывается из ячеек блока 2 и выдается на вход блока 3. При этом из блока 9 блокировки записи на вход блока 3 поступает так же код состояния той исходящей линии .связи, для которой в данный момент времени поступает информация из блока 2.

В блоке 3 производится сравнение кода состоянття исходящей линии связи и кода фронта коммутируемого сигпйта. Если эти коды одинаковые, то производится блокировка записи поступающей информации в блок 3. Вместо операции записи производится считывание информации из той же ячейки, и которую должна была производиться. запись. Если же коды отлича ются один от другого, то операция записи не блокируется. Запись информации в ячейки памяти блока 3 производится с одновременной выдачей этой информации, а также адреса ячейки, в которую записывается информация, на выход блока 3.

Запись и считывание информации из блока 3 производится с помощью адреса, поступающего из счетчика тактов 5.

При каждой операции записи и считывания, производимой блоком 3, информация и адрес ячейки (исходящей линии связи) поступают также на выход блока 3. При этом код времени поступает на входы блока сравнения 8, коды фронтов коммутируемых сигналов — на входы блоков 6, а адрес исходящих линий связи - на входы дешифратора 4.

На входы блока сравнения 8 поступает такие двоичный код времени из формирователя 7.

При совпадении кодов времени, поступающих из блоков 3 и формирователя 7,. блок сравнения 8 выдает в дешифратор 4 сигнал, который разрешает выдачу сигналов с выходов его. Сигналы с выходов дешифратора 4 поступают на входы блоков 6. С помощью этих сигналов и кодов фронтов коммутируемых сигналов, поступающих из блока 3, блоки 6 переходят в соответствующее состояние.

Счетчик тактов 5 вырабатывает коды адресов ячеек для считывания информации из блока 2 и для записи и считывания информации из блока 3, а также вырабатывает тактовые импульсы tj синхронизирующие работу всех блоков устройства.

Формула изобретения

Устройство цля пространственно-временной коммутации асинхронных цифровых сигналов, содержащее входные регистры, выходы которых подключены к входам блока первичной памяти,а также блок вторичной памяти, дешифратор, счет652727

Составитель Г. Теплова

Редактор A. Зиньковский Техред С. Мигай Корректор А. Кравченко

Заказ 1079/55 Тираж 774 Подписное

UHHHHH Государственного комитета СССР по цепам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород. ул..Проектная, 4 чик тактов и блоки выдачи сигналов, о тл и ч а ю ш е е с я тем, что, с цепью повышения пропускной способности устройства, введены последовательно соединенные формирователь кодов времени 5 и блок сравнения, а также блок блокировки записи, при этом выход блока первичной памяти подключен к первому входу блока вторичной памяти, первый выход которого подключен к другому входу бло- fO ка сравнения, второй выход подключен: к первому входу дешифратора, а третий и четвертый выходы подключены к входам блоков выдачи сигналов, выходы которых через блок блокировки записи подключены к второму входу блока вторичной памяти, выход блока сравнения подключен к второму входу дешифратора, выходы которого подключены к входам соответствующих блоков выдачи сигналов.

Источники информации, принятые во внимание при экспертизе

1. Лвторское свидетельство СССР № 519874, кл. Н 04 М 9/00, 1974.