Устройство для строчной синхронизации

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АЮТОРСКОМУ СВИДИТИЛЬСТВУ

Своз Советских

Соцналмстицееюа

Реслублнк

< 1652731

Гкударетеанамй кавит

СССР а делан хзобрвтенхЯ н аткрютий (6!) Дополнительное к авт. свид-ву(22) ЗаявлЕно 29.11.76 (2! ) 2425728/18-09 с присоединением заявки Ph (23) Приоритет

2, (51) М. Кл.

Н 04N 5/04

Опубликовано15.03.79. Бюллетень № 10 (5З) УЙК 621.397 (088.8) Дата опубликования описания 18.03.79

Е. H. Дикарев и А. A. Чистяков (72) Авторы изобретения (7Ц Заявитель (54) УСТРОЙСТВО ДЛЯ СТРОЧНОЙ СИНХРОНИЗАБИИ

Изобретение относится к телевиэиой» ной технике и предназначено для исполь эования и телевизионных. устройствах синхронизации, в частности в телевиэнон. ных приемниках и синхрогенераторах.

Известно устройство для строчной синхронизации, содержащее задающий генератор, выход которого подключен к вхо;ду блока вычитания, счетчик, первый выход которого подключен к первому вхо-. ду фазового детектора Щ . В этом устройстве необходимо обеспечить высокую частоту переключения счетчика, примерно равную 120 МГц. Такую скорость переключенйя трудно обеспечить без применения сверхбыстродействующих интегральных схем, что является суйест венным недостатком. Кроме того, это устройство не зашишено.от импульсных помех, вызванных наличием врезок в

I 20 кадровых сннхроимпульсах и выбросов в телевизионном сигнале.

Белью. изобретения является упрошение устройства эа счет исклк>чения сверх« быстродействующих логических элементов путем чет ьтрехкратного уменьшения частоты переключения счетчика при одновременном сохранении свойства фиксации номинальной строчной частоты выходных импульсов во время пропадания входного сигнала и повышение помехоэашишенности от воздействия импульсных помех.

Для этого в устройство для строч ной синхронизации, содержашее задающий генератор, выход которого подключен к входу блока вычитания, счетчик, первый выход которого подключен к первому входу фазового детектора, введены Т-триггер и последовательно соединенные формирователь импульса, инвертор, RS -триггер и логический алемент 2И-2ИЛИ-НЕ. Причем к второму входу последнего подключен выход формирователя импульса, к третьему входувыход Т-триггера, установочный вход которого соединен с вторым выходом R8 триггера, а четвертый вход логического

652731 элемента 2И-2ИЛИ-HE подключен к счетному входу Т-триггера и к второму выходу счетчика, третий выход которого соединен с вторым входом R8 -триггера, выход логического элемента 2И2ИЛИ-HE подключен к второму входу фазового детектора, второй вход блока вычитания подключен к выходу фазового детектора, а выход блока вычитания« входу счетчика.

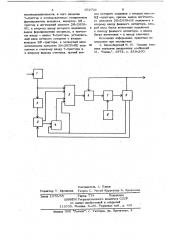

На чертеже изображена структурная электрическая схема устройства для строч ной синхронизации, которое содержит ,формирователь имцульса 1,инвертор 2, Щ -триггер 3, Ттpиrrеp 4,-логический элемент 2И-2ИЛИ-НЕ 5, фазовый детектор 6, блок вычитания 7. задающий генератор 8, счетчик 9.

Счетчик 9, фазовый детектор 6, задающий генератор 8 и блок вычитания

7 образуют двухпозиционную релейную . цифровую систему синхронизации. Мини.мальное время между моментами появления импульсов на входе счетчика в этой системе определяется соотношением

ЛЪ = Т ь . При заданном размахе колебаний временного положения импульсов ка выходе устройства строчной синхронизации М 2 30 кс, при этом максимальная частота переключения счетчика составляет приблизительно 30 МГц, т, е. вчетыре разаменьше, чем в известном устройстве синхронизации.

Для сохранения свойства фиксации номинальной частоты выходных импульсов во время пропадания входного сигнала, утрачиваемого при переходе к двухпозиционной цифровой системе синхронизации, и обеспечения защиты от импульсных помех ка вход логического элемента 2И-2ИЛИ-HE 5 и на вход инвертора 2 поступают укороченные импульсы, представляющие собой отметки временного положения передних фронтов импульсов положительной телевизионной синхросмесн. При этом наряду с истинными отметками временного положения строчных синхроимпульсов возможно появление ложных отметок, вызванных воздействием импульсных помех и кадровых врезок.

Уменьшение воздействия импульсных помех достигается ем, что логический элемент 2И«2ИЛИ-НЕ открыт для прохождения временных отметок входных импульсов только на коротком интервале времени, соответствующем наличию единичного уровня в стробируюшем сигнале, который вырабатывается RS-триггером 3. В такое единичное состояние

RS -триггер переводится импульсом с . опережающего выхода счетчика 9, а заЮ тем сбрасывается в нулевое состояние первым пришедшим на вход укороченным строчным синхроимпульсом. Благодаря существующей задержке интегральных схем этот укороченный синхронмпульс

Ю

1й успевает пройти ка выход логического элемента 2И-2ИЛИ-НЕ, в то время как на следующем за ним интервале времени, вплоть до прихода нового импульса с опережающего выхода счетчика, логи1 ческий элемент 2 И-2ИЛИ-Н Е закрыт для прохождения любых импульсов.

В случае пропадания входных синхроимпульсов на инверсном выходе gg -триггера 3 появляется нулевой сигнал до- статочной длительности и Т-триггер 4 начинает вырабатывать сигнал полустрочной частоты. Благодаря этому ка выходе логического элемента 2И-2 ИЛИ-HE 5, появляются инвертированные импульсы

2$ с запаздывающего выхода счетчика, дей- ствующие с полустрочной частотой, которые поступают на вход фазового детек тора 6, Так как прн появлении íà входе фазового детектора импульса с запаздывающего выхода счетчика 9 цифровая двухпозиционная система синхронизации вырабатывает выходные импульсы с максимальным периодом, а при отсутствии импульсов на входе фазового детектора

33

6 она вырабатывает импульсы с мини- мальным периодом, то появление импульсов полустрочной частоты с запаздывающего выхода счетчика приводит х комму

40 тации периода ймпульсов от строки к страхе на выходе устройства. При этом средний период выходного сигнала со счетчика 9 остается равен номинальному, т, е. сохраняется свойство фиксации

4$ номинальной частоты при пропадании входного сигнала.

Формула. изобретения

SO

Устройство для строчной синхронизации, содержащее задающий генератор, выход которого подключен к входу блока вычитания, счетчик, первый выход «оторого подключен к первому входу фазового детектора,о тлича ющеес я тем, что, с целью упрощения устройства за счет исключения сверхбыстродействующих логических элементов и повышения

5 652731 б помехозащишенности, в него введены ход которого соединен с вторым входом

Т-триггер и последовательно соединенные КЯ -триггера, причем выход логнческоформирователь импульса, инвертор, КВ - го элемента 2И-2ИЛИ-НЕ подключен к триггер и логический элемент 2И-2ИЛИ- второму входу фазового детектора, втоНЕ, к второму входу которого подключен 5 рой вход блока вычитания подключен выход формирователя импульса, к третье- к выходу фазового детектора, а выход му входу» выход T- òðêããåpà, установоч- блока вычитания — к входу счетчика. ный вход которого соединен с вторым Источники информации, принятые во выходом КЗ -триггера, а четвертый вход внимание при экспертизе логического элемента 2И-2ИЛИ-НЕ под- 10 1. Шляпоберский В. И. Основы техключен к счетному входу Т-триггера и ники передачи дискретных сообщений к второму выходу счетчика, третий вы- М.. Связь", 1973, с. 258-260, Составитель А. Панов

РедактоР Т. ЮРчикова Техред С. Мигай Корректор А. Кравченко

Заказ 1079/55 - Тираж 774 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35„Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4