Цифровой анализатор спектра

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<н653575 (6)) Дополнительное к авт. свид-ву— (22) 3аявлено OL1275 (21) 2193546/18-21 с присоединением заявки )6 (23) Приоритет— (51) М. Кл.

G 01 R 23/16

Государственный комитет ссср по делам изобретений н открытий (И) УДК 621,317.. .757 (088.8)1

Опубликовано 15.0379.Бюллетень ph 11

Дата опубликования опнсання250379 (72) Авторы

ИЗОбрЕТЕННЯ П.А.Бакулев, В.И.Литюк и Б.Л.Юфряков (71) Заявитель

Московский ордена Ленина авиационный институт им.Серго Орджоникидзе (5 4 ) ЦИФРОВОЙ АНАЛИЗАТОР СПЕКТРА

Изобретение относится к специализированным средствам цифровой техники, предназначенным для спектрального анализа случайных процессов.

Известно устройство для быстрого .. решения задач гармонического анализа, содержащее вычислитель., выполняющий операции над индексами, оперативное запоминающее устройство, постоянное запоминающее устройство и арифметическое устройство, оперирующее с комплексными числами (1).

Однако для вычисления алгоритма быстрого преобразования Фурье (БПФ) этим устройством требуется предварительная запись реализации в цифровой форме, после чего производятся операции умножения; пересйлки и суммиро-. вания. Кроме того, предварительная запись реализации не позволяет прово-® дить съем информации s любой момент времени.

Наиболее близким решением из известных является устройство, содержЪщее последовательно соединенные 25 .входной блок квадратурных составляющих, аналого-цифровой преобразова:тель, сумматор и оперативное запоми нающее устройство, постоянное запоми-. нающее устройство, связанное с ариф- 30 метическим блоком, блок квадраторов, подключенный к блоку извлечения корня квадратного через канальный сумматор, блок управления, ключи (2) .

Такое устройство при небольшом числе рассчитываемых коэффициентов

Фурье (порядка 100-300) позволяет получить более широкий однозначный диапазон анализируемых частот по сравнению с устройством, реализующим алгоритм БПФ.

Однако это устройство также имеет .ограничение по диапазону анализируемых частот, которое зависит от числа рассчитываемых .коэффициентов Фурье и от числа отсчетов случайного процесса, поскольку эа время Т при параллельном анализе должно производиться N комплексных сложений и умножений.

Время Т может быть выбрано иэ условия

>Tiat N, F макс где F с с - максимальная частота юйкС в спектре исследуемого сигнала; дС - время, необходимое на выполнение одной операции, комплексного умножения и сложения, определяемое разрядностью чисел„:, наи которыми производятся арифметические действия.

ПОскОльку максимальное числО цирку-" ляций М аграничквается числом рас-считываемых коэффициентов дискретного преобразования Фурье (ДНФ), то случай, когда И=М, и определяет быстро- Ь действие всего устройства, поскольку количество разрядов, определяющее быстродействие устройства„находится в случае работы с фиксированной запятой из условия 10

2 мб2

ГДе К.(числа Двоичных раэрЯДОВ АЦП)

К+К вЂ” число двоичных раэрядок для

4 обработки чисел в случае М циркуляций.

Увели 1ение скорости анализа можно получить, если Ограничить число циркуляций при прежней разрешающей способности, чта приведе" !; возможности оперирования с числами, имеющими меньшее число разрядов, к, как следстнке, к 20 снижению gt-.

Целью изобретения является расширение диапазона анализируемых частот.

Это достигается тем, что цифровой анализатор спектра, содержащий после-25 довательна соединенные входной блок квадратурных составляющих, аналогоцифровой преобразователь, сумматор и оперативное з апаминающее устройстно, постоянное запоминающее устройство, связанное с арифметическим блоком„ блок квадраторон, подключенный к блоку извлечения карня квадратного через канальный сумматор, блок управления и ключи,дополнительно снабжен сумма- 35 тором с округлением и вторым оперативным запоминающим устройствам,причем выход блока управления связан с первыми входамк всех ключей, выход первого ключа подсоединен ко второму входу сумматора, выходы второго и

40 третьего ключей снязаны со вторым входом арифметического блока, выходы которого подключены ко нторым входам первого и четвертого ключей, выходы четвертого и пятого кл1очей подключены 45 ко входам сумматора с округлением, выход которого соединен со входами квадратора и одновременна через второе оперативное запоминающее устройство — co вторым входом третьего клю- 50 ча, при этом выход первого оперативного э апамин ающе го устройств а подключен ко нторым входам второго и пятого ключей.

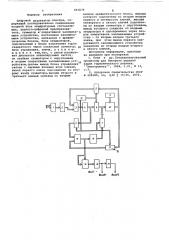

Па фиг.1 изображена структурная 55 схема устройства; н а фиг, 2 — оги бающие амплитуд н о-ч астот ных хар актеристик (ЛЧХ): а-первого каскада; б второго каскада; в — результирующая

АЧХ.

Цифровой анализатор спектра содержит последовательно соединенные входной блок 1 квадратурных составляющих, аналого-цифровой преобразователь (ЛЦП) 2, сумматор 3 и оперативное запоминающее устройство (ОЗУ) 4. бб

Оо вторым входом сумматора 3 соединен выход ключа 5, а ныход ОЗУ 4 соединен со входом ключа б, выход которого соединен с выходам ключа 7, который по одному входу соедкнен со входом ключей 8 и 9.

Выходы ключей б и 7 соединены с одним из входов арифметического блока (АБ) 10, со вторым входом которого соединено постоянное запоминающее устройстно (ПЗУ) 11, а выход блока

10 соединен со входами ключей 5 к 8.

Выход ключа 8 соединен со входом сумматора 12 с округлением, второй вход которого соединен с выходом ключа 9„а выход сумматора 12 с округлением через второе оперативное запоминающее устройство (вторае ОЗУ) 13со входом ключа 7 и со входом блока

14 квадраторов..

Блок 15 управления соединен по выходам с соответствующими входами ключей 5-9. Выход блоха 14 квадраторов подключен через канальный сумматор 16 к блоку 17 извлечения корня квадратного.

Устройство работает следующкм образом.

В начальный момент времени блок

15 управления замыкает ключи 5 и б и размы1 ает ключи 7-9. Пои этом образуется цифровой рециркулятор, состоящий соответственно из сумматора 3, ОЗУ 4, ключа б, ЛБ 10, ПЗУ 11 и ключа 5.

При поступлении на вход анализатора гармонического колебания частoтой Ы в блоке 1 образуются кнадрах турные составляющие, которые поступают на входы РЦП 2. Из выходных сигналов ЛЦП 2 в начале каждого интервала длительности Т берутся выборки, амплитуда которых преобразуется в двоичный код и затем запоминается на несь интервал длительности Т.

Выходные сигналы ЛЦП 2 в виде выборок н двоичном коде N раз в течение каждого интервала времени Т подаются на сумматор 3. C его выхода квадратурные составляющие в течение времени первой циркуляции 0-T последовательно N раз подаются на вход

ОЗУ 4, количество квадратурных ячеек каторога равно N (т,е. всего 2 нещественных ячеек), Это ОЗУ 4 предназначено для задержки чисел, поступающих с выхода сумматора 3 на время, равное Т. В течение перной циркуляции во все N ячеек ОЗУ 4 запишется одно и то же число.

В начале второй циркуляции происходит считывание двух чисел иэ первых ячеек ОЗУ 4, которые через ключ б поступают на вход AB 10. На второй вход 1Б 10 поступают числа, записанные в ПЗУ 11.

В ПЗУ 11 записано N чисел,соответствующих,выборкам cos 9 ."де 9 кэме5 6535

I яетcH от 0 до 2 g — — через Я= —, 27Г г,Г и М чисел, соответствующих выборкам

sine. Последовательное считывание всех значений созВи з1п 8 производится параллельно в течение каждого интервала длительностью Т, начиная со значения 6 =, Q и кончая значением 5

2 ŠN — - N

Числа, полученные на выходе АБ 10, поступают через ключ 5 на вход сумматора 3 и складываются с новой выбор- 0 кой, образованной в начале цикла на выходах ЛЦП 2, в результате чего последовательно получается N комплексных чисел, которые записываются в ячейки ОЗУ 4.

После L-1 циркуляций, т.е, на интервале времени t=(L-2)Т-,(L-1)Т, s ячейках ОЗУ 4 будут находиться числа, величины которых представляют отклик входного сигнала, прошедшего фильтр с йЧХ (см, фиг.2а) .

В конце интервала времени i. блок управления 1" размыкает ключи 5 и б и замыкает ключи 7-9. При этом ко входам РБ 10 через ключ 7 подключаетoë выход второго ОЗУ 13, а ко входам сумматора 12 с округлением через ключ 4 — выход АБ 10 и через ключ 5 выход ОЗУ 4. При этом образуется цифровой рециркулятор, состоящий из сумматора 12 с округлением, второго ОЗУ 30

13, ключа 7, ЛБ 10, ПЗУ 13 и ключа

Я

За время Т с момента t.-(L-1) Т до =ВТ N комплексных чисел последовательно з аписываются через сумматор 35

12 N комплексных ячеек второго ОЗУ 13. Поскольку перед началом работы во втором ОЗУ 13 были записаны нулевые числа, то F.B

10 в это r случае производит операции 40 с нулевыми числами„ Так как величина чисел при когерентном суммировании после L-1 циркуляции линейно возрастает в L-1 раз, то в сумматоре с округлением производится отбрасыва- 45 ние р= Pog (L-1) младших двоичных разрядов. Это позволяет Во втором каскаде оперировать с числами, имеющими то же число разрядов, как и в первом каскаде, В то же время, когда числа переписываются из ОЗУ 4 во второе ОЗУ 13, выборка сигнала с ЛЦР 2 одновременно записывается через сумматор 3 последовательно N раз в освободившиеся 55 ячейки ОЗУ 4. После окончания процесса перезаписи блок 15 управления размыкает ключи 7-9 и замыкает ключи

5 и б. При этом. образуется схема, описанная ранее, и начинается процесс накопления выборок в течение второй группы 1-1 циркуляций, в- результате чего в ячейках ОЗУ 4 в интервал времени с (2L-2.) Т по (2L-1) Т будут находиться числа, представляющие из себя реакцию фильтра с АЧХ, 65 изображенной на фиг. 2а, на воздействие следующего отрезка входного сигнала.

В момент времени t=(2L-1)Ò блок

15 управления разомкнет ключи 5 и 6.. и замкнет ключи 7-9. При этом числа, которые были записаны во втором ОЗУ

13 L-1 периодов назад, последовательно будут поступать на ЛБ 10 и над ними будут производиться операции, описанные ранее, за исключением того, что из ПЗУ 11 выбираются N чисел, соответствующих выборкам cos Щ где ?,9изменяется от 0 до 2.ILL

2 @

21Гь N через аЬ8= <, и N чисел, соответствующих выборкам sin L3. При этом второе ОЗУ 13 играет роль задержки каждого числа на L периодов.

После W-1 циркуляций во втором каскаде в течение времени Т на выходе второго ОЗУ 13 будут появляться числа, являющиеся откликом на . входное воздействие фильтра с АЧХ, изображенной на фиг.2в, которая представляет из себя произведение

АЧХ первого (фиг.2а) и второго (фиг.

2б) каскадов..

В течение последней циркуляции числа с выхода сумматора 12 с округлением подаются на входы блока 14 квадраторов и после операции перемножения-на канальный сумматор 16.

На выходе канального сумматора

16 в течение M=L W циркуляций получается N чисел в виде

2 М(6„.-UU T) м . z 8 --ммт э1п где А — амплитуда гармонического колебания ц;„, с, р 2 ГГ

Эти числа могут подаваться либо сразу на выход (в этом случае получаются числа, характеризующие энергетический спектр исследуемого процесса), либо через блок 17 извлечения корня квадратного (в этом случае получается амплитудный спектр) .

Полученные числа принимают максимальные значения при 9„ = и Т, которые соответственно равны ("„,)„=A М ) (Ч„т }м

Таким образом, первый каскад описываемого устройства определяет однозначность отсчетов в диапазоне частот О-Я., а второй каскад — разрешающую способность. При этом видно, что максимумы ЛЧХ второго каскада попадают в нули ЛЧХ первого каскада и полностью подавляются (фиг.2).

По окончании процесса накопления на временном интервале, равном периоду Т, с выхода устройства последовательно поступают отсчеты, временное положение и величина которых характеризуют спектр сигнала.

Формула изобретения

6535

ЦифРовой анализатор спектра, содержащий последовательно соединенные входной блок квадратурных составляющих,. аналого-цифровой преобразователь, сумматор и оперативное запомина- я ющее устройство., постоянное запоминающее устройство., связанное с арифметическим блоком, блок квадраторов, подключенный к блоку извлечения корня квадратного через канальный сумматор, 10 блок управления, ключи, о т Л и ч аю шийся тем,что, с целью расширения диапазона анализируемых частот, он снабжен сумматором с округлением и вторым оперативным запоминающим уст- ройством,причем выход блока управления связан с первыми входами всех ключей, выход первого ключа подсоединен ко второму входу сумматора, выходы второго и .третьего ключей связаны со вторым

75 8 входом арифметического блока, выходы которого подключены ко вторым входам первого и четвертого ключей, выходы четвертого и пятого ключей подключены ко входам сумматора с округлением> выход которого соединен со входами квадратора и одновременно через второе оперативное запоминающее устройство - co вторым входом третьего ключа, при этом выход первого оперативного запоминающего устройства подключен ко вторым входам второго и пятого ключей.

Источники информации, принятые во внимание при зкспертизе

1. Клан и др. Специализированный процессор для быстрого решения задач гармонического анализа. Электроника, 1968, т.41, 9 13, с.3.

2, Авторское свидетельство СССР

9 428389, кл, $06 f 15/36, 1972.

653575

Фиаg

Составитель А.Орлов

Техред И.Асталош Корректор С.Шекмар

Редактор Л.Народная

Тираж 696 Подписное

gHHHOH Государственного комитета СССР по. делам изобретений и открытий, 113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 1285/34

Филиал ППП Патент, r.Óæãîðîä, ул.Проектная, 4