Импульсно-фазовое следящее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l) Дополнительное к авт. свид-ву (22) ЗаЯвлено 11.04.77(21) 2474915/18-24 с присоед,инением заявки №(23) Приоритет—

Опубликовано 25.03.79 Бюллетень № 11

Дата опубликования описания 28.03.79

Союз Советских

Социалистимесних

Республик ()653596

Х (51) М. Кл.

Qr 05 В 1.1/ОО

Государственный квинтет

СССР оо делам нзабрвтвннй н отнрытнй (53) УДК 62:52 (088. 8) (72) Автор изобретения

Л. Л. Новак (71) Заявитель (54) ИМПУЛЬСНО-ФАЗОВОЕ СЛЕДЯЩЕЕ УСТРОЙСТВО

Предполагаемое изобретение относится к технике автоматического регулирования и может быть использовано в радиолокации и радионавигации.

Известны фазоследящие устройства, содержащие блок слежения за фазой и последовательно соединенные фазовращатель, фазосдвигатель на 90 и фазовый детектор, подключенный другим входом ко входу устройства, управляюший вход фазовращателя через фильтр нижних частот подключен к выходу чувствительного элемента блока слежения за фазой (1) .

Известны также фазоследящие устройства, содержащие аналогичный блок слежения за фазой и блок анализа, подключенный к выходу чувствительного элемента (ЧЭ) и управляющий ключом, который отключает выход ЧЭ от входа исполнительного устройства при наличии Синхронизма для уменьшения флюктуационньи погрешностей и снижения вероятности срыва сопровождения (2) .

Наиболее близким по техническому решению к предлагаемому является импульсно-фазовое следяшее устройство, содержащее блок слежения за фазой, первый вход которого совместно с первым входом первого счетчика времени подключен к выходу опорного генератора, а выход подключен к первому входу первого блока сравнения, входу синфазного детектора и входу делителя частоты, выход которого подключен ко второму входу первого счетчика времени и первому входу счетчика-интегратора, второй вход которого соединен с выходом синфазного детектора, а выход подключен к первому входу триггера (3).

Недостаток всех вышеупомянутых устройств заключается в том, что невозможно отличить состояние наличия синхронизма от состояния ложных тревог, так как в этих устройствах при срабатывании счетчика-интегратора от шумов (ложная тревога) отсчет будет разрешен и значение выходного сигнала блока слежения пройдет на выход схемы сравнения.

При использовании устройства в приемоиндикаторах импульсно-фазовых радионавигационных систем, например, типа Лоран-С, это приведет к неверному определению объектом его местоположения.

653596

Кроме того, скорость съема отсчета постоянна,определяется емкостью первого счетчика времени, задающего время анализа, и не зависит от достоверности отсчета.

Целью предлагаемого изобретения является повышение точности и быстродействия устройства.

Указанная цель достигается тем, что устройство содержит последовательно соединенные дискретизатор помех, вычислитель, второй блок сравнения, а также два элемента ИЛИ и второй счетчик времени, первый вход которого соединен с выходом делителя частоты, второй вход — с выходом первого элемента ИЛИ, третий вход — с выходом опорного генератора, а выход подключен к первому входу второго блока сравнения, второй вход которого соединен с выходом вычислителя, а выход подключен ко второму входу первого блока сравнения, третьему входу первого счетчика времени и первому входу второго элемента ИЛИ, выход которого соединен с третьим входом счетчика-интегратора, вторым входом триггера и первым входом первого элемента ИЛИ, второй вход которого соединен с выходом триггера, первый вход дискретизатора помех соединен с входом устройства, второй вход подключен к выходу делителя частоты, а выход соединен с входом вычислителя.

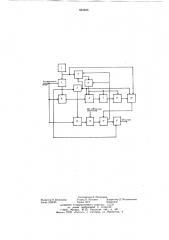

На чертеже приведена блок-схема устройства.

Устройство содержит опорный генератор

1, подключенный к опорному входу блока слежения за фазой 2 и счетному входу первого счетчика времени 3. Сигнальный вход блока слежения 2 совместно с сигнальным входом синфазного детектора 4 подключен ко входу устройства, а опорный вход синфазного детектора 4 совместно со входом делителя частоты 5 подключен к выходу блока слежения 2. Выход синфазного детектора 4 подключен к счетному входу счетчика-интегратора 6, вход запуска которого подключен к выходу делителя частоты 5. Вход запуска триггера 7 подключен к выходу счетчика-интегратора 6. Выход триггера 7 подключен к входу первого блока сравнения 8 через последовательно соединенный первый элемент ИЛИ 9, второй счетчик времени 10 и второй блок сравнения 11, вход которого подключен к входу устройства через последовательно соединенные дискретизатор помех 12 и вычислитель

13, вход дискретизатора 12 подключен к выходу делителя частоты 5, вход первого блока сравнения 8 подключен к выходу блока слежения 2, вход запуска второго счетчика времени 10 подключен к выходу делителя частоты 5, а счетный вход — к выходу опорного генератора 1.

Выход второго блока сравнения 11 через второй элемент ИЛИ 14 подключен к входам установки на нуль счетчика-интегратора 6, триггера 7 и к входу первого элемента ИЛИ 9, вход второго элемента ИЛИ 14 подключен к выходу первого счетчика времени 3.

Напряжение- опорного генератора 1 поступает на блок слежения 2, на сигнальный вход которого поступает смесь радиоимпульсов и помех. На выходе блока слежения 2 имеется последовательность импульсов, временное положение которых совпадает с нулями фазы высокочастотного заполнения сиг10 нального радиоимпульса и флюктуирует вследствие помех. С помощью делителя частоты 5 задается момент начала анализа состояния блока слежения 2. С помощью первого счетчика времени 3 задается момент

)s окончания анализа состояния блока слежения за фазой 2.

Первый импульс выхода делителя частоты 5 запускает первый счетчик времени 3 и счетчик-интегратор 6. Счетные импульсы с

20 выхода опорного генератора 1 начинают поступать на вход счетчика времени 3, а импульсы с выхода синфазного детектора 4— на счетчик-интегратор 6. Через время анализа, определяемое емкостью первого счетчика времени 3, принимается решение о том, 25 находится ли блок слежения за фазой 2 в состоянии синхронизма или нет, и осуществляется переход к новому циклу анализа путем сброса в нуль соответствующих блоков. При наличии синхронизма или ложных тревогах число импульсов на выходе синфазного детектора 4 максимально. Эти импульсы переполняют счетчик-интегратор 6 и его выходной импульс воздействует на триггер

7, изменяя его состояние. Выходной сигнал триггера 7 воздействует на второй счетчик з времени 10, останавливая его. Запуск второго счетчика времени 10 начинается одновременно с запуском первого счетчика времени 3, и его заполнение производится теми же счетными импульсами. Дискретизатор помехи 12 с помощью опорных импульсов формирует пробы шума, которые поступают в вычислитель 13, где по известным соотношениям вычисляется дисперсия помех 6 . На этот блок поступает также информация от внешних устройств о приблизительном местоположении объекта. В вычислителе 13 определяется априорное значение амплитуды сигнала А по известной зависимости

А = f (D), где D — дальность. В соответствии с - -, известной емкостью счетчикаинтегратора 6, вероятностями ложных тревог и правильного обнаружения находится априорное значение числа проб и, т. е. априорное значение Tanp— = h7cn, где Tcn— период следования сигнальных импульсов.

В втором блоке сравнения 11 величинаТ<, сравнивается со временем, зафиксированным вторым счетчиком времени 10 — 1д,. Если они примерно равны, на выходе второго блока сравнения 11 вырабатывается сигнал разрешения отсчета, который прекращается пе653596 ред новым циклом анализа путем сброса.

Если 1„„ ф Ъ, то это значит, что синхронизма нет, и срабатывание триггера 7 произошло из-за шумов. Тогда вычислителем

13 вырабатывается импульс, сбрасывающий соответствующие блоки, а с второго блока сравнения 11 на вход первого блока сравнения 8 импульс не поступает, т. е. отсчет запрешен. Затем выясняется, имеет ли место синхронизм, или срабатывание триггера 7 обусловлено шумами. Благодаря наличию связи блока второго сравнения ll с входом сброса первого счетчика времени 3, а через второй элемент ИЛИ 14 — с входами установки на нуль счетчика-интегратора 6, триггера 7 и второго счетчика времени 10 — новый цикл анализа может начаться сразу после того, как отсчет признан недостоверным из-за шумов.

Достоинством предполагаемого изобретения является повышение достоверности отсчета путем отбрасывания недостоверных отсчетов и следовательно, повышение надежности определения местоположения объекта.

Кроме того, благодаря возможности распознавания ситуаций ложных тревог и синхронизма, полученной вследствие введения новых блоков и связей, можно снизить время анализа, т. е. увеличить скорость отсчета без снижения надежности.

Увеличение скорости отсчета при использовании фазоследящего устройства совместно с автономными средствами при их корректировке позволяет снизить требования к скорости их ухода, следовательно, применять менее точные и более дешевые автономные средства.

Формула изобретения

Импульсно-фазовое следящее устройство, содержащее датчик фазы, первый вход которого и первый вход первого счетчика времени подключен к выходу опорного генератора, а выход подключен к первому входу первого блока сравнения, входу синфазного

Б детектора и входу делителя частоты, выход которого подключен ко второму входу первого счетчика времени и первому входу счетчика-интегратора, второй вход которого соединен с выходом синфазного детектора, а выход подключен к первому входу триггера, отличающееся тем, что, с целью повышения точности и быстродействия устройства, оно содержит последовательно соединенные дискретизатор помех, вычислитель, второй блок сравнения, два элемента ИЛИ и

15 второй счетчик времени, первый вход которого соединен с выходом делителя частоты, второй вход соединен с выходом первого элемента ИЛИ, третий вход соединен с выходом опорного генератора, а выход подключен к первому входу второго блока сравнения, второй вход которого соединен с выходом вычислителя, а выход подключен ко второму входу первого блока сравнения, третьему входу первого счетчика времени и первому входу второго элемента ИЛИ, вы25 ход которого соединен с третьим входом счетчика-интегратора, вторым входом триггера и первым входом первого элемента ИЛИ, второй вход которого соединен с выходом триггера, первый вход дискретизатора помех соединен с входом устройства, второй вход подключен к выходу делителя частоты, а выход соединен с входом вычислителя.

Источники информации, принятые во внимание при экспертизе з5 1. Авторское свидетельство СССР № 325674, кл. Н 04 В 3/04, 1969.

2. Авторское свидетельство СССР № 474756, кл. G 01 R 23/00, 1974.

3. Патент США № 3577178, кл. 324 — 83 D

1973.

653596

Редактор Н. Веселкина

Заказ 1289/35

Составитель Э. Митрошин

Техред О. Луговая Корректор Д.Мельниченко

Тираж 1014 Подписное

11НИИПИ Государственного комитета СССР по делам изобретений и открытий

I 13035, Москва, Ж35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4