Устройство для подавления импульсных помех

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистииескиз

Республик

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ («) 653754

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 26.04.77 (21) 2481440/18-09 с присоединением заявки №вЂ” (23) Приоритет— (51) М К

Н 04 В 15/00

Гооударотвеииый комитет

СССР по делам изооретеиий и открытий (53) УДК 621.396..66 (088.8) Опубликовано 25.03.79. Бюллетень № 11

Дата опубликования описания 30.03.79. (72) Автор изобретения

В. Ю. Солонин (71) з аявитель (54) УСТРОИСТВО ДЛЯ ПОДАВЛЕНИЯ

ИМПУЛЬСНЫХ ПОМЕХ

Изобретение относится к радиотехнике и может использоваться в импульсных устройствах, работающих с сигналами с большим уровнем помех.

Известно устройство для подавления импульсных помех, содержащее первый согласующий каскад, выходной фазоинверсный каскад, база транзистора которого соединена через диод с выходом первого согласующего каскада и через резистор — с общей шиной, а эмиттер через параллельную

RC-цепь — с общей шиной, и второй согласующий каскад, затвор транзистора которого через последовательную диодно-резисторную цепь соединен с выходом первого согласующего каскада и через запоминающий конденсатор — с общей шиной (1) .

Однако в известном устройстве велико влияние частоты и взаимного расположения импульсов помехи и полезного сигнала.

Цель изобретения — уменьшение влияния частоты и взаимного расположения импульсов помехи и полезного сигнала.

Для этого в известное устройство для подавления импульсных помех параллельно запоминающему конденсатору включен ключ, между выходом первого согласующего каскада и управляющим входом ключа включены последовательно дополнительный диод и дифференцирующая цепь, а исток транзистора второго согласующего каскада и вход дифференцирующей цепи подключены к эмиттеру транзистора фазоинверсного каскада через соответствующие дополнительнье резисторы

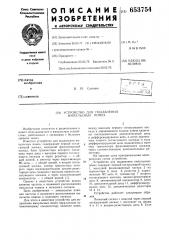

На чертеже дана принципиальная электрическая схема устройства.

Устройство для подавления импульсных помех содержит первый согласующий каскад

1, выходной фазоинверсный каскад 2 на транзисторе 3, диод 4, резистор 5, параллельную RC-цепь 6, транзистор 7 второго согласующего каскада, диодно-резисторную цепь 8, запоминающий конденсатор 9, ключ

10, дополнительный диод 11, дифференцирующую цепь 12, дополнительные резисторы

l3 и 14.

Устройство работает следующим образом.

Полезный сигнал с помехой через первый согласующий каскад 1 поступает на диоды

4 и 11 и диодно-резисторную цепь 8. Если

653754

Формула изобретения

Составитель Е. Любимова

Техред О. Луговая Корректор А. Гриценко

Тираж 774 Подписное

Редактор Т. Клюкина

Заказ 1310/43

Ц НИ И П И Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская иаб., д. 4/5 филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

3 сигнал больше порогового напряжения, то вырабатывается короткий импульс, которым ключ 10 на время, равное его длительности, приоткрывается, и запоминающий конденсатор 9, заряженный предыдущим импульсом полезного сигнала, частично разряжается. Короткий импульс по длительности меньше длительности полезного сигнала, поэтому за оставшееся время запоминающий конденсатор 9 заряжается до напряжения, равного амплитуде нового сигнала. Разностью между амплитудой полезного сигнала и пороговым напряжением приоткрывается транзистор 3 и на его выходе вырабатывается сигнал без помехи. Таким образом, после прохождения полезного сигнала до прихода следующего напряжение на запоминающем конденсаторе 9 практически остается неизменным. Это вызывает неизменность порогового напряжения, и все помехи, появившиеся в отсутствии полезного сигнала, через устройство не проходят. Очередной сигнал, если он отличается от предыдущего, корректирует пороговое напряжение, и следующий сигнал ограничивается новым пороговым напряжением.

Устройство для подавления импульсных помех, содержащее первый согласующий кас4 кад, выходнои фазоинверсныи каскад, база транзистора которого соедийена через диод с выходом первого согласующего каскада и через резистор — с общей шиной, а эмиттер через параллельную RC-цепь — с общей шиной, и второй согласующий каскад, затвор транзистора которого через последовательную диодно-резисторную цепь соединен с выходом первого согласующего каскада и через запоминающий конденсатор — с общей шиной, отличающееся тем, что, с целью уменьшения влияния частоты и взаимного расположения импульсов помехи и полезного сигнала, параллельно запоминающему конденсатору включен ключ, между выходом первого согласующего каскада и управляющим входом ключа включены последовательно дополнительный диод и дифференцирующая цепь, а исток транзистора второго согласующего каскада и вход дифференцирующей цепи подключены к эмиттеру транзистора фазоинверсного каскада через соответствующие дополнительные резисторы.

Источники информации, принятые во внимание при экспертизе

l. Линия задержки магнитострикционная. Схема принципиальная электрическая

1Ц3.084.028.ЭЗ,ТУ 25-01 (1 Ц3.084.028) — 74.

Государственное союзное конструкторскотехнологическое бюро по проектированию счетных машин, Л., 1973.