Устройство для цифро-аналогового формирования однополостных сигналов с амплитудно-фазовой модуляцией

Иллюстрации

Показать всеРеферат

(ц 653764

Союз Соеетскмн

С©цмалмстмчесниз

Республик (6l} Дополнительное к авт. свиа-ву (22) Заявлено 29.11.76 (ß} 2425282/18-09 с присоединением эаявки №вЂ” (23) ПриоритетОпубликоваио25.03.79,Бюллетень M 11

Дата опубликования описания 28.03.79 (5i) М. Кл

Н 04 Ь 27/04

Н 04 Хы 27/20

Госудврстаннны1 иветт

СССР а делам нзабретеннй н аткрытнй (53} УДК 621.394. .6 (088.8) (72} Автори иэобретения

В. И. Васильев, В. A. Свириденко и В. Я. Нерода

Московский институт инженеров гражданской авиации (7 I) Заявитель (54) УСТРОЙСТВО ДЛЯ ЦИФРОАНАЛОГОВОГО ФОРМИРОВАНИЯ

ОДНОПОЛОСНЫХ СИГНАЛОВ С АМПЛИТУДНО-ФАЗОВОЙ

МОДУЛЯЦИЕЙ

Изобретение относится к технике передачи данных в системах телемеханики и связи.

Известно устройство для цифроаналогового формирования однополосных сигналов с амплитудно-фазовой модуляцией, содержащее блок определения знака и модуля передаваемого символа, первый выход которого подключен к информационному входу дешифратора, выходы которого через накапливающие сумматоры подключены к входам сглаживающих фильтров, делители амплитуды, к управляющим входам которых подключен второй выход блока определения знака и модулч передаваемого символа, генератор гармонического сигнала, выход которого подключен к первому входу первого аналогового умножителя и через фазовращательк первому входу второго аналогового умножителя, и выходной сумматор, к выходам которого подключены выходы первого и второго аналоговых умножителей (Ц

Однако это устройство не позволяет добиться требуемой точности выходного сигнала.

Цель изобретения — повышение точности формирования выходного сигнала.

Для этого в устройство для цифроаналогового формирования однополосных сигналов с амплитудно-фризовой модуляцией, содержащее блок определения знака и модуля передаваемого символа, первый выход которого подключен к информационному входу дешифратора, выходы которого через накапливающие сумматоры подключены к входам сглаживающих фильтров, делители амплитуды, к управляющим входам которых подключен второй выход блока определения знака и модуля первдава емого символа, генератор гармонического сигнала, выход которого подключен к первому входу первого аналогового умножителя и через фазовращатель - к первому входу второго аналогового умножителя, и выходной сумматор, к входам которого подключены выходы первого и вто653764 рого аналоговых умножителей, введены запоминающие блохи, выходы которых подключены к управляющим входам дешифраторв, а выходы сглаживающих фильтров подключены к сигнальным входам делите- 5 лей амплитуды, выходы которых подключены к вторым входам первого и второго аналоговых умножителей.

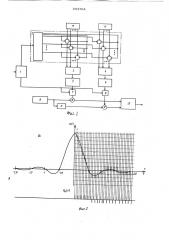

На фиг. 1 дана структурная электрическая схема предложенного устройства; 10 на фиг. 2 — синфазная компонента R(t) однополосного сигнала с амплитудным спектром, имеющим форму "приподнятого косинуса",, его цифровая копия Rp(t) полученная путем дельта-модуляции и последовательность из + 1, отображаю-. щая цифровой сигнал Rq(t ); на фиг. 3 аналогичные иллюстрации для квадратурной компоненты Ц (= ); на фиг. 4 » иллюстрация формирования аналогового сигнала по его цифровой дельта-копии, записанной в запоминающем блоке.

Устройство для цифроаналогового формирования однополосных сигналов с амплитудн ààoàî6 модуляцией содержит блок 1 определения знака и модуля передаваемого символа, дешифратор 2, включающий распределитель импульсов и управляемые ключи-инверторы, накапливающие сумматоры 3 и 4, сглаживающие фильтры

5 и 6, делители 7 и 8 амплитуды, генератор 9 гармонического сигнала, первый аналоговый умножитель 10, фазовращатель 11, второй аналоговый умножитель

12, выходной сумматор 13 и запоминаю35 щие блоки 14 и 15.

Устройство работает следующим образом.

От источника сообщения каждые T сек, 40 поступают символы в моментыЙ =КТ, где К 0,1,2... В устройстве для цифроаналогового формирования однополосных сигналов с амплитудно-фазовой модуляцией каждому символу О нужно поставить

45 в соответствие сигнал . Зк(+ ), определяемый соотношением

S„= а„8Л)=(61 п Иок 4P(t) cos 0t+

+ фЦ 6ЬНдвЦ, 50 где sign ay — знак символа;

A(t)

Для формирования однополосного сигнала синфазнвя Я (t ) и квадрвтурнвя

Я (t ) компоненты умножаются в аналоговых умножителях 10 и 12 соответст венно на соа о1 и sin сов1 (эти гармонические колебания формируются с помощью генератора 9 гармони IpcKoI о сигнала и фвзоврвщателя ll на

По заданному спектру 3(co) =8(и)е 4 сигнала 8 (t ) подсчитываются компоненть! R(t) и Q(t)

В силу того, что принцип формирования Ц (t ) и Q (t ) аналогичны, то достаточно рассмотреть только формирование компоненты Й {т ).

Функцию К (t ) подвергают дельтамодуляции. В этом случае Р (t ) аппроксимируется ступенчатым колебанием с шириной, ступеньки по оси времени At < Т и ее. высотой по оси уровня Ь А.

Параметры М. и 6 А дельта-модуляции определяются производной Р (t) и

I точностью аппроксимации.

Перепад такого колебания на шаг Ю вверх обозначим +1, вниз — 1.

Легко видеть, что ступенчатое колебание и последовательность из +1 и -1 взаимно однозначны .(см. фиг. 2а, 6).

В силу четности Й (t) достаточно аппроксимировать только при ЬЪО или /t<0>

Аналогичные замечания относятся и к нечетной функции Я (t) с учетом ин- вертирования последовательности из +1 и -1 при переходе ото. О иВЪО (см. фиг. За, 6).

Последовательность из +1 н -1 (или, что эквивалентно, 1 и О) записывается в запоминающий блок 14, последовательно через интервал ЙЙ считывается с помощью дешифратора 2 и подается

+1 и -1 в накапливающий сумматор 3.

Процесс формирования R (t) в упрощенной форме представлен на фиг. 4, где для наглядности дешифратор 2 представлен в механической интерпретации (см. фиг. 46), на фиг. 4а дана последовательность +1 и -1, отображающая ступенчатый сигнал {см. фиг. 4в) на выходе сумматора 3 такой последовательности. Он является аппроксимацией аналогового сигнала 6 (t). Элементы последовательности записаны в ячейки запоминающего блока 14, которые считываются дешифратором 2 через интервал dt .

При необходимости инвертировать ступенчатый сигнал на вход инверторв, включенного перед сумматором, подается управляющий импульс.

Нв фиг. 4в гладкая» кривая представляет собой результат обработки ступенчатой кривой в:.сглаживающем фильтре 5 (без учета задержки) .

653764 6 размера и относительно большей емкости существенно расширяет функциональные воэможности устройства для цифроаналогового формирования однополосного сиг% нала.

В формирователе инвертирование необходимо после считывания всех ячеек запоминающего блока 15 и начала процесса его считывания в другом направлении (с учетом нечетности Q (t)I.Ñ÷è тывание из запоминающего блока 14 в обратном направлении производится без инверсии элементов последовательности, записанной в запоминающий блок 14 в силу четности R (t). 1О

Для обеспечения знака однополосного сигнала 6 (t ), соответствующего знаку символа Ок, в распределителе дешифратора 2 одновременно вырабатываются сигналы дпя управления ключами-инверторами дпя обеспечения требуемого знака компонент Р (t) и О (t).

Формирование сигнала 6 (t) требуемой амплитуды обеспечивается путем изменения коэффициента передачи управляемых 20 делителей 7 и 8 сигналами из блока 1, соответствующих модулю символаая .

Использование нового принципа цифрового формирования синфазной и квадратурной компоненты однополосного сигнала, регулируемого с помощью запоминающих блоков, дешифратора и накапливающего сумматора, позволяет обеспечить наперед заданную точность генерации сигнала и снижает требования к сглаживающему фильтру. Для формирования сигнала с произвольным спектром достаточно записать соответствующую ему цифровую копию синфаэной и квадратурной компонент сигнала в запоминающий блок или использовать набор запоминающих блоков, выбирая иэ него всякий раз такую пару, которая позволяет обеспечить требуемый спектр однополосного сигнала, Последнее обстоятельство, в виду промышленного изготовления запоминающих блоков на интегральных схемах, их малого веса, Формула изобретения

Устройство для цифроаналогового формирования однополосных сигналов с амплитудно-глазовой модуляцией, содержа.щее блок определения знака и модуля передаваемого символа, первый выход которого подключен к информационному входу дешифратора, выходы которого через накапливающие сумматоры подключены к входам сглаживающих фильтров, делители амплитуды, к управляющим входам которых подключен второй выход блока определения знака и модуля передаваемого символа, генератор гармонического сигнала, выход которого подключен к первому входу первого аналогового умножителя и через фазовращатель — к первому входу второго аналогового умножителя, и выходной сумматор, к входам которого подключены выходы первого и второго аналоговых умножителей, о т л и ч а ю» ш е е с я тем, что, с цепью повышения точности формирования, введены запоминающие блоки, выходы которых подключены к управляющим входам дешифратора, а выходы сглаживающих фильтров подключены к сигнальным входам делителей амплитуды, выходы которых подключены к вторым входам первого и второго аналоговых умножителей.

Источники информации, принятые so внимание при экспертизе

1. Данилов В. С., Штейнбок М. Г.

Однополосная передача цифровых сигналов. М., "Связь, 1974, с. 55-65.

653764

Составитель В. Лякишев

Редактор Л. Гребенникова Техред Н. Бабурка Корректор С. Шекмар

Заказ 1315/44 Тираж 774 Подписное

IIHHHHH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r Ужгород, ул. Проектная, 4