Устройство сопряжения

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1656049

Союз Советских

Социалистимеских

Республик (6!) Дополнительное к авт. свид-ву— (22) Заявлено 20. 04. 77 (21) 2479140/1Â вЂ” 24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл

6 06 F 3/04

Гвсударствеиие|й комитет

СССР пе делам иэебретеиий и открытий

Опубликовано 05. 04. 79. Бюллетень № 13

Дата опубликования описания 05.04. 79 (53) УДК 681. Зг5 (088.8) А, Г. Бодня, Н. Н. Васерин, Ю. Н. Виноградов, А. С. Горелик, И. Н. Крылов и В. П. Лысый (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО СОПРЯЖЕНИЯ

Изобретение относится к области вычислительной техники, в частности, к устройствам сопряжения различных по скоростным характеристикам источников и приемников информации и может быть использовано в системах обмена данными.

Известно устройство сопряжения, содержащее коммутатор, блок управления, блок преобразования, распределитель, элементы

И, ИЛИ, триггер, счетчик, блок пуска, регистр адреса, шифратор, пульт управления, долговременное запоминающее устройство, 1о линию задержки (1J.

Недостатком устройства является необходимость затрат значительного количества оборудования.

Наиболее близким к изобретению по тех15 нической сущности и достигаемому результату является устройство сопряжения, содержащее дешифратор адреса, формирователь, триггер, первый и второй элементы И (21.

Недостатками данного устройства являются: большой объем электронного оборудо- 20 вания из-за наличия буферного запоминающего блока; ограниченный объем передаваемой информации, зависящий от емкости буферного запоминающего блока; отсутстl

2 вие приоритетного выбора передаваемой информации; ограничение диапазона скоростей сопрягаемых устройств, так как средняя скорость поступления входной информации должна быть меньше скорости считывания.

Цель изобретения — сокращение оборудования и расширение функциональных возможностей путем обеспечения произвольной последовательности передачи данных.

Поставленная цель достигается тем, что устройство содержит коммутатор каналов, регистр сдвига, дешифратор кода запроса, схему сравнения, третий и четвертый элементы И, элемент ИЛИ, элемент НЕ, причем единичный и нулевой выходы триггера соединены с первыми входами соответственно первого, второго третьего и четвертого элементов И, вторые входы первого и второго элементов И соединены соответственно с первым и вторым выходами коммутатора каналов, выходы первого и третьего элементов И через элемент ИЛИ соединены с первым входом регистра сдвига и со входом элемента НЕ, выход которого соединен с первым входом дешифратора адреса и через формирователь — с единичным входом триггера, нулевой вход которого соединен с вы656049 ходом схемы сравнения, первый и второй выходы дешифратора кода запроса соединены соответственно со входом коммутатора каналов и с первым входом схемы сравнения, второй вход которой соединен с выходом дешиф ратора адреса, второй вход, первый и второй выходы регистра сдвига соединены соответственно с выходом второго элемента И, со вторыми входами дешифратора адреса, второй вход, первый и второй выходы дешифратора кода запросасоединены соответственно со входом коммутатора каналов и с первым входом схемы сравнения, второй вход которой соединен с выходом дешифратора адреса, второй вход, первый и второй выходы регистра сдвига соединены соответственно с выходом второго элемента И, со вторыми входами дешифратора адреса и четвертого элемента И, а группа входов коммутатора каналов, вход дешифратора кода запроса, второй вход третьего элемента И и выход четвертого элемента И являются соответственно группой входов устройства, первым, вторым входом и выходом устройства.

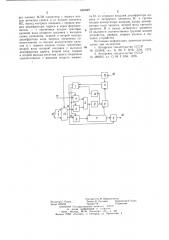

Структурная схема устройства приведена на чертеже.

Устройство сопряжения содержит триггер 1, элементы И 2 — 5, элемент ИЛИ 6, регистр сдвига 7, элемент НЕ 8, дешифратор 9 адреса, формирователь 10, схему сравнения 11, дешифратор кода запроса 12, коммутатор каналов 13. Позициями 14 — 19 обозначены на чертеже выходы коммутатора каналов, группа входов устройства, первый и второй входы и выход устройства.

Устройство работает следующим образом.

Дешифратор кода запроса 12 по коду запроса, поступающему на вход 18, производит выбор определенного канала, одновременно формируя код адреса требуемой информации в схему сравнения 11.

В исходном положении триггер 1 находится в состоянии «1» и сигналы информационного выхода 15 коммутатора каналов

13 через открытый элемент И 3 поступают на информационный вход регистра сдвига 7, а тактовые импульсы с выхода 14 коммутатора каналов 13 через элемент И 2 и элемент ИЛИ 6 поступают на тактовый вход регистра сдвига 7 и элемент HE 8. После окончания записи информации в регистр сдвига 7, элемент НЕ 8 вырабатывает сигнал окончания записи, который поступает в дешифратор 9 как разрешение дешифрации и в формирователь 10. Формирователь

10 формирует импульс установки триггера

1 в состояние «1». В режиме записи информации состояние триггера 1 не изменится.

Если адрес принятой информации не совпадает с адресом, требуемым кодом запроса, то схема совпадения 11 не срабатывает и в регистр сдвига 7 поступает следующая информация. При совпадении адресов с де25

Таким образом, устройство позволяет исключить буферный запоминающий блок, а наличие в устройстве дешифратора кода запроса и коммутатора каналов отличает его от известного устройства. В устройстве производится передача только запрашиваемой информации, нет ограничений по частотным характеристикам приемника и датчиков, обеспечена возможностью подключения группы датчиков с различными частотными характеристиками, отсутствует ограничение по объему передаваемой информации, увеличение объема передаваемой информации не требует увеличения объема электронного оборудования.

Формула изобретения

1О

20 шифратора 9 и дешифратора кода запроса

12 схема совпадения 11 вырабатывает импульс установки триггера 1 в состояние «О», и единичный выход триггера 1 запрещает поступление в регистр сдвига 7 тактовых и информационных сигналов коммутатора каналов 13, а нулевй выход триггера 1 разрешает прохождение импульсов по входу 17 от приемника через элемент И 4 и информации, записанной в регистр сдвига

7 через элемент И 5. По окончании выхода информации элемент НЕ 8 через формирователь 10 устанавливает триггер 1 в состояние «1», тем самым подготавливая элементы И 2, 3 для пропуска тактовых и информационных сигналов от коммутатора каналов 13 в регистр сдвига 7. Так как передача информации происходит независимо от приема, то частота тактовых импульсов датчиков и приемника может быть произвольной. В зависимости от кода запроса, можно передавать всю последовательно поступающую информацию датчика одного канала, или информацию с различных датчиков в любой необходимой приемнику последовательностии.

Устройство сопряжения, содержащее дешифратор адреса, формирователь, триггер, первый и второй элементы И, отличающееся тем, что, с целью сокращения оборудования и расширения функциональных возможностей за счет обеспечения произвольной последовательности передачи данных, оно содержит коммутатор каналов, регистр сдвига, дешифратор кода запроса, схему сравнения, третий и четвертый элементы И, элемент ИЛИ, элемент НЕ, причем единичный и нулевой выходы триггера соединены с первыми входами соответственно первого, второго и третьего, четвертого элементов И, вторые входы первого и второго элементов

И соединены соответственно к первым и вторым выходам коммутатора каналов, выходы первого и третьего элементов И че656049

Составитель Ф. Шагиакметов

Редактор С. Равва Техред О. Луговая Корректор Е. Папи

Заказ 1522/39 Тираж 779 Подписное

LLHHHflH Государственного комитета СССР по делам изобретений и откргитий

I 13035. Москва, )К-35, Раушска я на 5., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 рез элемент ИЛИ соединены с первым входом регистра сдвига и со входом элемента

НЕ, выход которого соединен с первым входом дешифратора, адреса и через формирователь — с единичным входом триггера, нулевой вход которого соединен с выходом схемы сравнения, первый и второй выходы дешифратора кода запроса соединены соответственно со входом коммутатора каналов и с первым входом схемы сравнения, второй вход которой соединен с выходом дешифратора адреса, второй вход, первый и второй выходы регистра сдвига соединены соответственно с выходом второго элемен| та И, со вторыми входами дешифратора адреса и четвертого элемента И, а группа входов коммутатора каналов, входы дешифратора кода запроса, второй вход третьего элемента И и выход четвертого элемента

И являются соответственно группой входов устройства, первым, вторым входом и выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 433482, кл. G 06 F 9/18, 3/04, 1974.

2. Авторское свидетельство СССР № 488202, кл. G 06 F 3/04, 1976.