Преобразователь двоичного кода в перестановочный код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОВГЕтЕНИЯ ""65605З

Союз Соаетсиик

Социапистичвсиик

Республик

К ЛВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 241077 (Я) 2539752/18-24 с присоединением заявки И— (23) Приоритет— (51) М. Кл.

G 06 F 5/02

Государственный иомитет

СССР ио делам изобре еиий н открытий

Опубликовано 050479. Бктллетень Хв 13 (оЗ) УДК (088. 8)

Дата опубликования описания 070479 (72) Автор изобретения

Б.M.Çëoòíèê

Pl) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОЛА

В ПЕРЕСТАНОВОЧНЬ)Й КОЛ

Изобретение относится к области автоматики и цифровой вычислительной техники и может быть использовано при построении систем передачи и обработки информации, телеуправления и телеиэмерения.

Известно устройство для преобразования двоичного кода в перестановочный код (1), содержащее дешифратор числового кода, сдвиговый регистр, формирователь номера сигнала и блоки формирования символов.

Недостатками такого устройства являются его сложность н увеличение количества аппаратуры при увеличении числа разрядов преобразуемого кода.

Наиболее близким по технической сущности к изобретению является преобразователь (2) двоичного кода в перестановочный код, содержащий первый и второй формирователи символов перестановочного кода, выходы которых соединены с выходными шинами преобразователя, регистр сдвига, счетчик числа символов и блок управления.

Недостатком такого устройства является его сложность при числе символов, равном трем и ограниче-. нии числа смежных символов одного значения.

Целью изобретения явлется упрощение преобразователя.

Эта цель достигается. тем, что предложенный преобразователь содержит блок преобразования младших разрядов входного кода и дешифратор старших разрядов входного кода, выходы которого соединены с первой группой входов первого формирователя символов перестановочного кода.

Вторая группа входов первого формирователя символов перестановочного кода соединена с первой группой выходов блока преобразования младших разрядов входного кода, второй и третий выходы которого соединены соответственно с первым и вторым входами второго формирователя символов. Третья группа входов второго формирователя символов соединена с первой группой выходов первого формирователя символов.

Блок преобразования младших разрядов входного кода содержит и -выходной полный дешифратор младших разрядов входного кода, группу иэ 0 /2 элементов ИЛИ, первый и второй элементы ИЛИ, входы которых соединены

3 6560 соответственно с четными и нечетнымй выходами дешифратора младших раэрядон входного кода; Выходы первого и второго элементов ИЛИ являются вторым и третьим выходами блока преобразования младших раэрядон входного кода. Входы -ro ((-1 - . I)/2) элемента ИЛИ группы соединены с (2(-1) — ым! и 2(-ым выходами дешифратора младших разрядов входного кода, а выходы группы элементон ИЛИ являются выходами блока преобразования младших .разрядов входного кода.

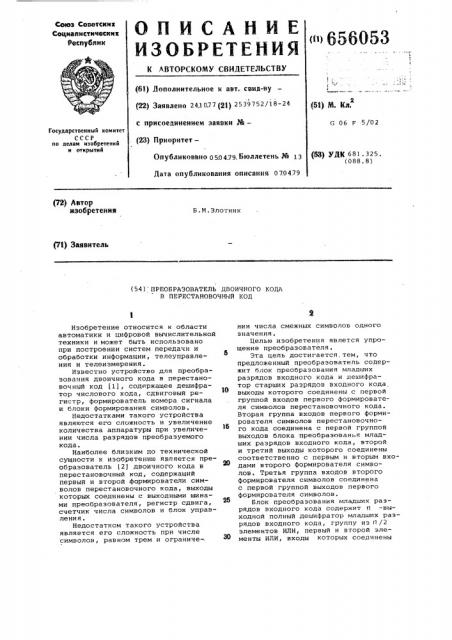

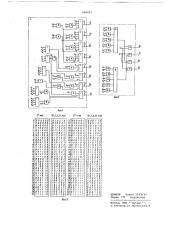

На фиг.l дана структурная схема предлагаемого устройства; на фиг.2 схема блока преобразования млад-, ших разрядов входного кода (на три разряда); на фиг.3 — схема дешифратора старших раэрядон входного кода; на фиг.4 и 5 — схемы первого и второго формирователей символов (для преобразователя,шестиразрядного дноич-20 ного кода н шестиразрядный троичный код с двумя символами каждого значения в словах (6,2,2,2)-код; на фиг.бтабличное представленне (6 2,2,2)— кода. 25

Предлагаемое устройство содержит шины 1 1 — 1к входного кода, блок 2 преобразования младших разрядов входного кода, дешифратор.3 старших разрядов входного кода, первый формирователь 4 симнолон, шину 5 четных комбинаций, шину б нечетных комбинаций, второй формирователь 7 символов, выходные шины 8 1 — 8 л первого ненулевого символа, выходные шины 91 — 9Л второго ненулевого символа перестановочного кода, первую и вторую группы выходных шин 10-11.

Шины. 11 — lp младших разрядов входного кода присоединены ко входам блока 2, шины lq — 1 старших 40 разрядон входного кода — ко входам дешифратора 3. Выходы блока 2 и выходы дешифратора 3 соединены со входами формирователя 4 символов, выходы которого и шины 5 и б соединены 45 со входами формирователя 7 символов.

Выходы формирователя 4 подключены также к шинам 8 g — 8II 2и 91 — 9п выходы формирователя 7 — к шинам 8II;j„.

8п и 9л l, 9II 50

Входное К -разрядное слово полного двоичного кода поступатет в устройство по шинам 11 — 1к. По шинам

1 1 — lp оно возбуждает блок 2, а по шннам 1I) — 1 — дешифратор 3.

Выходные сигналы блока 2 и дешифратора 3 формируют в формирователе 4 ненулевые символы W --2 младших разрядов перестановочного кода. Появление сигнала на любом четном или нечетном выходе блока 2 возбуждает шину 5 или б соответственно. При возбуждении шин

5 или б и выхода формирователя 4 в формирователе 7 формируются ненулевые символы двух старших разрядов перестановочного кода. Сигналы первого 65 и второго ненулевых символов возбуждают выходные шины соответственно

81 — 8Л и 91- 9П °

Блок преобразования младших раз рядов (фиг.2) содержит дешифратор

12 младших раэрядон нходного кода, группу элементов ИЛИ 13, первый

14 и второй 15 элементы ИЛИ, которые формируют единичный выходной сигнал при возбуждении четного или нечетного выхода дешифратора 12.

Рассмотрим работу устройства на примере преобразования слон

000000, 100110 и llllll двоичного кода н (6; 2,2,2) -код. Поступление первого слова возбуждает н блоке 2 шины д1и 5, в дешифраторе 3 — шину 1 ф н фоРмиРователе 4 — шины С2 d 4i н формирователе 7 — одну из шин и выходные шины 82, 94, 8з и 96 образуя слово 010212 перестаноночного кода. Поступление слова 100110 возбуждает входные шины 1, 1 и 1 н блоке преобраэонания 2 — шиныа,, б, в дешифраторе 3 - шину V4 и формирователе 4 — шины C4,34, в формирователе 7 — одну из шин «) и выходные шины 81, 9А,,9 и .8, образуя слово 100221 перестаноночного кода. Поступление слова 111111 возбуждает шины 11, 1>, в блоке преобразования 2 — шины а, б, н дешифраторе 3 — шину V>, в формирователе

4 — шины Д, C 4, н формирователе 7 одну иэ шин и выходные шины 9з, 84", 9 g и 8g образуя слово 002121 перестаноночного кода..

Предлагаемое устрйство преобразует перестановочный код во вторичный без потери скорости передачи информации и с ограниченным числом смежных символов одного значения, что важно, например, при передаче

ИКМ сигналов н оснонной полосе, так как ограничивает снизу частотный спектр сигнала и уменьшает межсимвольные искажения, Преобразователь двоичного кода в (6; 2,2,2) -код позволяет передавать цифровые сигналы на более, чем с тремя нулевыми, и не более,чем с двумя одинаковыми ненулевыми смежными символами. В результате передаваемая последовательность сигналов, обладая таким же частотным спектром, как у лучших кваэитроичных кодов, позволяет упростить линейные узлы передачи и приема, дает возможность обнаружить ошибки по числу симнолон каждого значения в словах, уменьшить джиттер и понысить надежность синхронизации за счет равномерной и высокой плотности ненулевых символов.

Использование кода н (бу 2,2,2)код потребовало в 1,6 раза меньше аппаратуры по.сравнению с известным. устройством (2) за счет исключения сумматора и других функциональных узлов.

656053

Формула изобретения

15

20 и

Ч4

9п-I

tp вп-г

9п г ! в

1. Преобразователь двоичного кода в перестаноночный код, содержащий первый и второй формирователи символов перестановочного кода, выходы которых соединены с выходными шинами преобразонателя, о т л и ч а ю шийся тем, что, с целью упрощения преобразователя, он содержит блок преобразования младших разрядов входного кода и дешифратор старших разрядон входного кода, выходы которого соединены с первой группой входов первого формирователя символов перестановочного кода; вторая группа входов первого формирователя символов перестановочного кода соединена с первой группой выходов блока преобразования младших разрядов входного кода, второй и третий выходы которого соединены соот-. ветственно с первым и вторым входами второго формирователя символов, третья группа входов нторого формирователя символов соединена с перной группой выходов первого формирователя символ„он.

2. Преобразователь по п.1, о т л и ч а ю шийся тем, что в нем блок преобразования младших разрядов входного кода содержит и -выходной полный дешифратор младших рязрядов входного кода, группу из n/2 элементов ИЛИ, первый и второй элементы ИЛИ, входы котор х соединены соответственно с четными и нечетными выходами q --выходного полного дешифратора младших разрядов входного кода; выходы первого и второго элементов

ИЛИ являются вторыми и третьими выходами блока преобразования младших разрядов входного кода; входы -го (! .=1 + tI/2) элемента ИЛИ группы соединены . с (2 1 -1) -ым и 2 1 -ым выходами дешифратора младших разрядов входного кода, а ныходы группы элементов

ИЛИ являются выходами блока реобра зования младших раэрядон входного кода.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р362437, кл. EI 03 К 3/80, 1970.

2. Авторское свидетельство СССР

Р510709, кл." G 06 Г 5/02, 1975.

656053

Фиг.4

Zо-код (8i 2,2,2)-код

Ф//г б

О

2

4

5 б

8

0

lf

l2

Ц

14

l5 б

I7

/8

19

Zl гг г3

24

Z5

Z8 г7

28

29

0102 /2

О/ог2(О //202

О //220

О/20/2

0 I 202 I

0 I2 102 о/г !го

0201/2

020 121

02! 012

02/OZf

02/ 2 (0

021 20/

О 22 / /0

022101 ! го/02

120/20

/гог/о (20201 (2/002

/2(020

1220 10

122 О О 1

I00 2(2

I00 22/

10 1 202 (а! ггО

/02 О 12

10202 /

/02 102

102 120

52

33

34

3б

37

39

4D

4(42

44

4б

47

48

49

5/

52

54

58

57

58

59

80 б/

62

2 -код (6;Z,г,г)-код

000 00/

100Î О I

OtOOO I

/10 001

o0/ 0 0 1 (О (О О (Of /O0 I

I(tOO(000 tof (00 10 I

О/0(О 1

/!О (О t

O0I(O I

IO(/О /

0 // l 0I

l t I /O/

000 О I I (ОО O(l

0f0 О fl

//О О //

00/О f f

I 0 I O 11

Ol / О / l

It lO (I

000(/(1001 l I

0IO((I

/ОО II

oot f(t

l0f f I I

Of / I (1 (!1((1

ЦНИИ ПИ Заказ 152 3/39

Тираж 779 Подписное

Филиал ППП Патент, r.Óæãoðoä,óë.Проектная,4