Элемент однородной вычислительной среды

Иллюстрации

Показать всеРеферат

Свюз Советских

Социалистических

Республик

ОП ИСАН

ИЗОБРЕТЕН

К АВТОРСКОМУ СВИДЕТЕЛЬС (61) Дополнительное к авт. свил-в (22) Заявлено 20.06.72 (Я) 1799416 с присоединением заявки ла (23) Приоритет

Государственный комитет

СССР по делам изооретений и открытий

Опубликовано 050479. Бвллет

Дата опубликования описани (72) Авторы изобретения

В.A. Торгашев, B.М. Кисельников, В. Б. Смирнов, В.И.Андрианов и Л.И.Бердников

Ленинградский институт авиационного приборостроения (71) Заявитель (54) ЭЛЕМЕНТ ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ

Изобретение относится к вычислительной технике, может быть использовано при разработке вычислительных

4 средств на основе однородных вычислительных сред.

Известен элемент однородной вычислительной среды, содержащий элементы

И, дешифраторы и статический регистр jlJ .

Недостаток этого элемента — невозможность получения управляемой за= держки выходного сигнала.

Известен элемент однородной вычислительной среды, содержащий статический регистр, логический узел, два элемента И, элемент ИЛИ и элемент HE (2J .

Недостаток этого элемента — невозможность получения регулируемой. задержки выходного сигнала, Цель изобретения — получение регу.лируемой задержки выходного сигнала. цель достигается тем, что в элемент однородной вычислительной среды, содержащей статический регистр, логический узел, два элемента И, элемент ИЛИ и элемент НЕ, введены два дешифратора входных переменных, дешифратор управляющей переменной, дешифратор кода операций, йинамичес кий регистр и дешифратор-селектор, первая и вторая группа входов. которого соединены соответственно с выходами динамического регистра и с первой группой выходов статического регистра, вторая, третья, четвертая и пятая группы выходов которого соединены с первыми группами входов соответственно первого и второго дешифраторов входных переменных, дешифратора кода операций и дешифратора управляющей переменной) входы логического узла соединены с выходами дешифраторов входных переменных и дешифратора кодов операций, выход логического узла соединен с первыми входами первого и второго элементов И, выходы которых соединены соответственно со входом динамического регист® ра и с первым входом элемента ИЛИ, выход и второй вход которого соединены соответственно с выходом элемента однородной вычислительной среды и выходом дешифратора-селекторау выход дешифратора управляющей переменной соединен со вторым входом перво го элемента И и входом элемента ilB выход которого соединен со вторым входом второго элемента Иу вторые @. группы входов дешиФратора входных

656054 переменных и дешифратора управляющеи переменной соединены соответственно с первой, второй и третьей группами входов элемента однородной вычислительной среды.

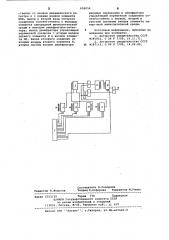

Структурная схема элемента однородной вычислительной среды показана на чертеже.

Элемент однородной вычислительной среды содержит статический регистр 1, логический узел 2, элементы И 3 и 4, элемент ИЛИ 5, элемент НЕ 6, дешиф- 10 раторы 7 и 8 входных переменных, дешифратор 9 управляющей переменной,дешифратор 10 кода операций, динамический регистр ll и дешифратор-селектор

12, первая и, вторая группы входов 15 которого соединены соответственно, с выходами динамического регистра ll и первой группой выходов статического регистра 1, вторая, третья, четвертая и пятая группы выходов которого соединены с первыми группами входов дешифраторов входных переменных 7 и 8 соответственно дешифратора кода операций 10 и дешифратора управляющей переменной 9. Входы логического узла 2 соединены с выходами дешифраторов входных переменных

7 и 8, дешифратора кодов операций 10.

Выход логического узла 2 соединен с первыми входами элементов И 3 и 4, выходы которых соединены соответственно со входом динамического регистра 11 и с первым входом элемента ИЛИ

5, выход и второй вход которого соединены соответственно с выходом 13 элемента однородной вычислительной среды и выходом дешифратора-селектора 12. Выход дешифратора управляющей переменной 9 соединен со вторым входом элемента И 3 и со входом элемента HE 6,, выход которого соединен со 40 вторым входом элемента И 4. Вторые группы входов дешифраторов входных переменных 7 и 8 и дешифратора управляющей переменной 9 соединены соответственно с группами входов 14,15 и 48

16 элемента однородной вычислительной среды..

Элемент однородной вычислительной среды работает следующим образом.

После занесения настроечного кода в статический регистр 1 на выходах дешифраторов 7 и 8 появляются значения входных переменных Х1 и Х> а на выхо,де дешифратора 10 — код операций, которые поступают в логический блок

2, выполняющий соответствующую операцию над переменными Х и Х . Результат операции поступает на информационные входы элементов И 3 и 4.

Управляющая переменная Х иа выхо- . 80 де дешифратора 9 лринииает значение логического 0 или 1 . При

Х =О элемент И 3 закрыт, а элемент

И 4 открыт выходным сигналом элемента HE 6. Результат операции, выполнен-6яной логическим узлом 2, поступает при этом на вход элемента ИЛИ 5 и далее - на выход 13.

При х q =1 элемент И 3 открыт, а элемент И 4 закрыт. Информация с логического узла 2 поступает через открытый элемент И 3 в динамический регистр 11, в котором она сдвигается с частотой тактирования регистра. В зависимости от той части кода настройки, которая управляет работой дешифратора-селектора 12, на выходе

его проходит сигнал от определенного разряда динамического регистра 11.

Таким образом, результат операции поступает на выход дешифратора-селектора 12 и затем на выход 13 элемента однородной вычислительной среды с задержкой, определяемой кодом настройки элемента и вырабатываемой путем съема сигнала с определенного разряда динамического регистра 11 °

Следовательно, на выходе элемента реализуется функция

g(t i Х ()1 XÄ(t)» Х, (), где ц — выходной сигнал, момент появления которого завщсит от х и от кода настройки элемента величина задержки, определяемая кодом настройки элемента;

ХЭ((,)- значение управляющей переменной в момент

xg(4) и xg(t) — входные сигналы, поступающее в момент — операция, выполняемая логическим узлом.

Формула изобретения

Элемент однородной вычислительной среды, содержащий статический регистр, логический узел, два элемента И, элемент ИЛИ и элемент iiE о т л и ч а ю шийся тем, что, с целью получения регулируемой задержки выходного сигнала, в него дополнительно введены два дешифратора входных переменных, дешифратор управляющей переменной, дешифратор кода операций, динамический регистр, дешифратор-селектор, первая и вторая группы входов которого соединены соответственно с выходами динамического регистра и первой группой выходов статического регистра, вторая, третья, четвертая и пятая группы выходов которого соединены с первыми группами входов соответственно первого и второго дешифраторов входных переменных, дешифратора кода операций и дешифратора управляющей переменной, входы логического узла соединены с выходами дешифраторов входных переменных и дешифратора кодов операций, выход логического узла соединен с первыми входами первого и второго элементов

Я, выходы которых соединены соответ656054

Составитель О.Скворцов

Техред Л.Алферова Корректор М. Ряшко

Редактор Б.федотов

Закаэ 1523/39 Тирам 779 Подписное

I1HHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб;, д. 4/5

\ филиал ППП Патент, r.Óæãîðîä, ул.Пр ектная,4 ственно со входом динамического регистра и с первым входом элемента

HJIH„ выход и второй вход которого соединены соответственно с выходом элемента однородной вычислительной среды н выходом дешифратора-селектора, выход дешифратора управляющей переменной соединен с вторым входом первого элемента И и входом элемента НЕ, выход которого соединен со вторым входом второго элемента И, вторые группы входов дешифратора входных переменных и дешифратора управляющей переменной соединены соответственно с первой, второй и третьей группами входов элемента однорсчной вычислительной среды.

8 Источники информации, принятые во внимание при экспертиз

1. Авторское свидетельство СССР

9395832, G 06 F 7/00, 16.11.71.

2. Авторское свидетельство СССР

10 9287115, G 06 F 7/00, 14.06.69.