Устройство для возведения в степень

Иллюстрации

Показать всеРеферат

описА4ИЗОБРЕТЕН

Союз Советских

Социалистических

Реотублик

6056

К АВТОРСКОМУ СВИДЕТЕЛЬ (61) Дополнительное к авт. свид-ву (22) Заявлено 21.12.76, (21) 2432790/1 с присоединением заявки № (23) Приоритет

Опубликовано 05.04.79. Бюллет

Дата опубликования описания

Кл

6 F 7/38

Государственный «омотет

СССР ао делам нзооретеннй н открытнй

К .325 (088.8) (72) Авторы изобретения

А. П. Уриков, А. Г. Ермаков и А. В. Паевский (71) Заявитель

Морской гидрофизический институт АН УССР (54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В СТЕПЕНЬ

Изобретение относится к области вычислительной техники и может быть использовано в различных цифровых вычислительных машинах, построенных на больших интегральных схемах, для возведения в степень исходных двоичных кодов.

Известны устройства для возведения в степень (например, в квадрат (1), содержащее регистры, группы логических элементов, генератор импульсов, распределитель импульсов, недостатком которых является функциональная ограниченность.

Наиболее близким по технической сущности к предложенному является устройство для возведения в степень, содержащее регистр операнда, разрядные выходы которого соединены с первыми входами элементов И первой группы, вторые входы которых подключены к соответствующим разрядным выходам вспомогательного регистра операнда, а выходы — ко входам блока комбинационных сумматоров, выход которого соединен со входом регистра результата, вторую группу элементов И, первые входы которых соединены с информационным входом устройства, а выходы подключены к разрядным входам регистра операнда, третью группу элементов И, блок управления, вход которого подключен ко входу синхронизации устройства, а управляющий выход — ко входам начальной установки всех регистров (2) .

Недостатком известного устройства является его сложность.

Целью настоящего изобретения является упрощение устройства.

Указанная цель достигается тем, что устройство дополнительно содержит многовходовой элемент ИЛИ и кольцевой регистр, разрядные выходы которого соединены со вторыми входами элементов И второй группы, выходы блока управления соединены с первыми входами элементов И третьей группы, вторые входы которых подключены к соответствующим выходам регистра результата, а выходы подключены ко входам многовходового элемента ИЛИ, один из входов которого подключен к информационному входу устройства, а выход соединен со входом вспомогательного регистра операнда.

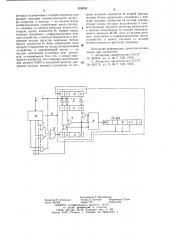

На чертеже представлена функциональная схема устройства, содержащая: информационный вход 1 и вход синхронизации 2 устройства, регистр 3 операнда, вспомога656056 тельный регистр 4 операнда, первая вторая и третья группы элементов И 5, 6, 7 соответственно, блок комбинационных сумматоров 8, регистр результата 9, блок управления

10, -вход 11 начальной установки всех регистров, многовходовой элемент ИЛИ 12, кольцевой регистр 13.

Работает устройство следующим образом.

По входу 2 поступает на вход блока 10 управления синхронизирующий импульс (СИ) 10 по этому импульсу блок 10 управления. вырабатывает по выходам 11 импульс начальной установки всех регистров устройства.

Затем по информационному входу 1 начинает поступать код операнда Х. Вход 1 уст- 15 ройства соединен с первыми входами второй группы 6 элементов, вторые входы этих элементов И соединены с разрядными выходами вспомогательного кольцевого регистра

13. Кольцевой регистр 13 импульсом начальной установки обнуляется, а триггер первого разряда его устанавливается в 1 состояние, причем на каждом такте умножения эта единица сдвигается в следующий разряд, подавая разрешающий потенциал на элемент И соответствующего разряда Т. о. к началу первого такта разрешающий потенциал с регистра 13 подан на элемент И первого разряда и первый разряд кода операнда Х запишется в триггер первого разряда регистра 3. Первый разряд кода операнда через элемент 12 ИЛИ запишется также во вспомогательный регистр 4. Выходы триггеров регистра 3 и 4 соединены со входами элементов И, группы 5. Таким образом, после записи первого разряда кода в регистры 3 и 4, этот разряд кода анали- З5 зируется элементом И и, если эта единица, то на выходе элемента И установится потенциал единицы и через блок сумматоров 8 на следующем такте будет записана единица в регистре 9 результата (если первый разряд был равен О, то в регистр 9 результата будет записан О), которая и является младшим разрядом квадрата операнда, на втором такте будет в состоянии 1 уже триггер второго разряда вспомогательного кольцевого регистра 13 и, следовательно, открыт 45 будет второй элемент И группы 6, через которую и запишется второй разряд кода операнда Х во второй разряд регистра 3, этот же разряд операнда через элемент ИЛИ 12 запишется во вспомогательный регистр 4, но в триггер первого разряда, при этом значение первого разряда кода операнда Х сдвинется во второй разряд регистра 4, то есть регистр 4 сдвиговой, в отличии от регистра 3, триггера которого объединены только по входам сброс. Теперь уже 55 в образовании второго младшего разряда квадрата участвуют два элемента И группы 5, и на очередном такте в регистр 9 результата будет записан с выхода блока сумматоров второй младший разряд произведения. После и тактов код операнда Х будет записан в регистр 3 так, что первый разряд кода будет в первом разряде регистра 3 а и-й в п-м в регистре 4 этот же код запишется в обратном порядке — 1-м разряде — п-й в п-м — 1-й, а в регистре

9 результата будет записано и младших разрядов квадрата. После п-тактов генератор тактовых импульсов блока 10 управления переключается на более высокую частоту, чем частота поступления разрядов исходного кода из канала связи, и в устройстве совершается п быстрых тактов, в результате которых регистр 4 очистится, а в регистр 9 результата будут записаны и старших разряда квадрата, в регистре 3 код Х останется без изменения. После возведения исходного кода в квадрат, блок 10 управления вырабатывает разрешающий потенциал по выходу, соединенному со входом элемента И группы 7, второй вход которого соединен с выходом (N — 2) и разрядов регистра 9 результата. Это позволит через элемент ИЛИ 12 подать на вход вспомогательного регистра 4 код квадрата с регистра 9 результата. Аналогичным образом могут быть получены и более высокие степени исходного кода. Причем вычисление всех степеней (кроме квадрата) может осуществляться на высокой тактовой частоте, которая может быть на несколько порядков выше, чем частота поступления исходных кодов. После вычисления наивысшей необходимой степени блок 10 управления вырабатывает на выходах 11 импульс сброса регистров устройства в исходное сотояние и устройство может оперировать с очередным операндом.

С помощью предлагаемого устройства можно вычислять выражения вида х 1, где

« N, N — показатель степени, так как после вычисления любой степени соответствующий код может быть передан с регистра 9 результата на любое внешнее устройство.

Схема устройства достаточно проста, она содержит четыре регистра (и — 1) — одноразрядный комбинационный сумматор, три группы элементов И и блок управления (известное (.N + 2) регистра, (N — 1) — сумматор, (.M — 1) групп элементов И и блок местного управления) .

Простота устройства позволяет повысить его надежность и снизить стоимость и энергоем кость.

Формула изобретения

Устройство для возведения в степень, содержащее регистр операнда, разрядные выходы которого соединены с первыми входами элементов И первой группы, вторые входы

656056

Составитель Н. Шелобанова

Редактор Э. Губницкая Техред О. Луговая Корректор Е. Папп

Заказ 1522/39 Тираж 779 Подписное

11НИИПИ Государственного комитета СССР по делам изобретений и от к р мт н й

113035, Москва, % 35, Раушская наб., д. 4/5

Филиал ППП <<Патент», г. Ужгород, ул. Проектная, 4 которых подключены к соответствующим разрядным выходам вспомогательного регистра операнда, а выходы — ко входам блока комбинационных сумматоров, выход которого соединен со входом регистра результата, вторую группу элементов И, первые входы которых соединены с информационным входом устройства, а выходы подключены к разрядным входам регистра операнда, третью группу элементов И, блок управления, вход которого подключен ко входу синхронизации устройства, а управляющий выход — ко входам начальной установки всех регистров, отличающееся тем, что, с целью упрощения устройства, оно содержит многовходовой элемент ИЛИ и кольцевой регистр, разрядные выходы которого соединены со вторыми входами элементов И второй группы, выходы блока управления соединены с первыми входами элементов И третьей группы, вторые входы которых подключены к соответствующим выходам регистра результата, а выходы подключены ко входам многовходового элемента ИЛИ, один из входов которого подключен к информационному входу устройства, а выход соединен со входом вспомогательного регистра операнда.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

No 364934, кл. G 06 F 7/38, !970.

2. Авторское свидстельство СССР

М 425175, кл. G 06 F 7/38, 1972.