Многоканальное устройство тестового контроля цифровых узлов электронных вычислительных машин

Иллюстрации

Показать всеРеферат

ОП ИСАНИ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l) Дополнительное к авт. свид-ву М 390526 (22) Заявлено 06. 04. 77 (21) 2479016/18 — 24 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 05, 04. 79. Бюллетень №

Дата опубликования описания 05.04.

656065

Союз Советских

Социалистических

Республнк м. кл

G 06 F 11/04

Государственных комитет

СССР но делам нзебретенхй н аткрытнй

УДК 681. 32S (088.8) (72) Авторы изобретения

P. Е. Глух и В. И, Ефремов (71) Заявитель (54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ

ЦИФРОВЫХ УЗЛОВ ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ

МАШИН

Изобретение относится к области электронной вычислительной техники может быть использовано в аппаратуре контроля и настройки цифровых узлов электронных вычислительных машин и является усовершенствованием известного устройства, описанного в авт. св. № 390526.

В основном изобретении по авт. св. № 390526 описано многоканальное устройство тестового контроля цифровых узлов

ЭВМ. Это устройство содержит запоминающее устройство для хранения тестов, регистр теста, устройство записи информации из запоминающего регистра в регистр теста, формирователи входных сигналов, формирователи выходных сигналов, коммутационное устройство и устройство сравнения. Запоминающая ячейка любого из разрядов регистра тестов подключена через выходной формирователь выходных сигналов и переключатель коммутационного устройства и через устройство сравнения и входной формирователь к входному контакту проверяемого цифрового узла.

Недостатком этого устройства является то, что при контроле цифровых узлов, управляемых импульсными сигналами микроопера2 ций, это устройство не обеспечивает подачу на входы проверяемого узла импульсов нужной полярности, задержанных относительно момента изменения потенциальных сигналов тестовой информации и имеющих длительность меньшую, чем длительность такта известного устройства. Кроме того, известное устройство не обеспечивает возможность контроля импульсных выходных сигналов, имеющих длительность меньшую, чем длительность такта этого устройства.

Целью изобретения является повышение быстродействия.

Цель достигается тем, что в предложенное устройство введены по числу разрядов элементы И, элементы НЕ, формирователь стробирующих импульсов, элементы задержки, формирователь входных воздействий, группа переключателей, причем выход каждого переключателя группы соединен с выходным формирователем и схемой сравнения соответствующего разряда, первый вход каждого переключателя группы соединен с выходом соответствующего разряда регистра теста и с первым входом соответствующего элемента И, вторые входы которых объединены и соединены со входом первого элемен656065 та задержки и выходом формирователя входных воздействий, вход которого соединен с выходом второго элемента задержки, вход которого соединен с устройством записи информации, выход первого элемента задержки соединен со входом формирователя стробирующих импульсов, выход которого соединен со входами всех схем сравнения коммутатора, второй вход каждого переключателя группы соединен с выходом соответствующего элемента И и входом соответствующего элемента НЕ, выходы элементов НЕ соединены соответственно с третьими входами переключателей группы.

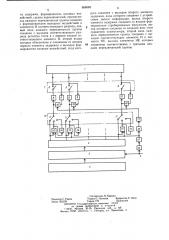

Функциональная схема предлагаемого многоканального устройства тестового контроля цифровых узлов электронных вычислительных машин показана на чертеже.

Показанный на чертеже проверяемый узел 1 в состав устройства не входит, а приведен для пояснения описания.

Предлагаемое устройство содержит запоминающее устройство 2, соединенное через устройство записи информации 3 с регистром теста 4. Вход 5 служит для подачи сигнала управления переписью информации из запоминающего устройства в регистр теста. Каждый контакт проверяемого узла 1 соединен через переключатель 6 коммутатора 7 и выходной формирователь 8 и через включенный параллельно ему входной формирователь 9 и устройство сравнения 10 с выходом переключателя 11 группы переключателей 12.

Входы переключателя 11 соединены: первый — с выходом соответствующего разряда регистра теста 4, второй — с выходом элемента И 13, первый вход которого соединен с тем же выходом регистра теста 4, а третий — через элемент НЕ 14 со вторым входом этого же переключателя 11. При этом вторые входы всех элементов И соединены через формирователь входных воздействий

15 и элемент задержки 16 с управляющим входом 5, а третьи входы элемента И 10 соединены через формирователь стробирующих импульсов 17 и элемент задержки 18 с выходом формирователя входных воздействий 15.

Устройство работает следующим образом.

Проверяемый узел 1 имеет п контактов, каждый из которых может быть входным или выходным, что фиксируется соответственно замкнутым или разомкнутым положением переключателя 6 коммутатора 7. При этом каждый входной контакт может быть потенциальным или импульсным, что фиксируется соответственно левым или двумя правыми положениями переключателя 11 переключательной группы 12.

По сигналу управления (вход 5) тестовая информация из запоминающего устройства

2 через устройство записи 3 записывается в регистр теста 4.

Если, например, первый контакт проверяемого узла 1 является входным потенциальным, то информация с выхода первого разряда регистра теста 4 через переключатель

11, формирователь входных воздействий 8 и переключатель 6 поступает на этот контакт в виде потенциала.

Если, например, этот входной контакт

10 является импульсным, то при наличии единицы в соответствующем разряде регистра теста 4 через элемент И 13, переключатели 11 и 6 и формирователь входных импульов 8 на этот контакт поступает импульс, 1$ адержанный элементом задержки 16 относительно сигнала управления (вход 15) и сформированный формирователем входных. воздействий 15. При этом, если входной контакт предназначен для приема импульса противоположной полярности, то переклю20 чатель 11 фиксируется в крайнем правом положении и импульс на этот контакт поступает проинвертированным элементов HE 14.

Таким образом, осуществляется подача импульсных входных воздействий, в том числе разнополярных.

Если же рассматриваемый контакт является выходным, то переключатель 6 размыкается, а переключатель 11 устанавливается в левое положение. Информация с выходного контакта проверяемого узла 1 через

З0 формирователь входных воздействий 9 поступает на элемент И 10, где сравнивается с контрольной, хранящейся в этом случае в триггере соответствующего разряда регистра теста 4. При этом для обеспечения пра35 вильного сравнения с импульсным выходным сигналом на третьи входы элементов И 10 подаются стробирующие импульсы, задержанные элементом задержки 18 относительно импульсов входных воздействий и сформированные формирователем стробирующих

40 импульсов 17. Длительность стробирующих импульсов меньше длительности импульсов входных воздействий.

Указанные отличия в предлагаемом уст45 ройстве позволяют повысить быстродействие и обеспечивают возможность контроля импульсных входных сигналов, имеющих длительность, меньшую чем длительность такта этого устройства.

Формула изобретения

Многоканальное устройство тестового контроля цифровых узлов электронных вычислительных машин по авт. св. № 390526, отличающееся тем, что, с целью повышения быстродействия, в него введены по числу разрядов элементы И, элементы НЕ, формирователь стробированных импульсов, элемен656065 ты задержки, формирователь входных воздействий, группа переключателей, причем выход каждого переключателя группы соединен с формирователем выходных воздействий и элементом И соответствующего разряда, первый вход каждого переключателя группы соединен с выходом соответствующего разряда регистра теста и с первым входом соответствующего элемента И, вторые входы которых объединены и соединены со входом первого элемента задержки и выходом формирователя входных воздействий, вход которого соединен с выходом второго элемента задержки, вход которого соединен с устройством записи информации, выход второго элемента задержки соединен со входом формирователя стробированных импульсов, выход которого соединен со входами всех схем сравнения коммутатора, второй вход каждого переключателя группы соединен с выходом соответствующих элемента И и элемента НЕ, выходы элементов НЕ которых

l6 соединены соответственно с третьими входами переключателей группы.

Составитель H. Быкова

Редактор С. Равва Техред О. Луговая Корректор Е. Папп

Заказ 1522 39 Тираж 779 Подписное

11НИИПИ Государственного комитета СССР по делам изобретений и открытий! 13035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4