Устройство для моделирования сетевого графика

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистииеских

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

" 656067 (61) Дополнительное к авт. свид-ву— (22) Заявлено 01.09.76 (21) 2397734/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл

G 06 F 15/20

Государственный комитет

СССР ао делам изобретений и открытий

Опубликовано 05.04.79. Бюллетень № 13

Дата опубликования описания 05.0,79 (53) УДК681.325..65 (088.8) (72) Авторы изобретения

В. Ф. Муравьев и В. А. Полунов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ

СЕТЕВОГО ГРАФИ КА

Изобретение относится к области вычислительной техники и может быть использовано в качестве основного командно-информационного устройства на сложных технологических комплексах.

Известно устройство для моделирования технологических процессов (1), содержащее блок управления с подключенными к нему блоком анализа, элементы И и блоки логики.

Наиболее близким по технической сущности к изобретению является устройство для моделирования сетевого графика (2), содержащее блок управления, первая группа выходов которого подключена к первым и вторым входам элементов И первой группы, первым входам элементов И второй группы, вторая группа выходов блока управления соединена с управляющими входами элементов ИЛИ вЂ” НЕ,и запоминающую матрицу.

Недостатком известных устройств является низкая точность моделирования.

Целью изобретения является повышение точности устройства.

Указанная цель достигается тем, что устройство содержит дополнительную запоминающую матрицу, арифметический блок, блок оперативной памяти, блок сопряжения, блок регистрации и группу генераторов случайных чисел, выходы которых подключены к соответствующим входам запоминающей матрицы, выходы которой соединены с одними входами блока регистрации и арифметического блока соответственно, другие входы арифметического блока подключены к соответствующим выходам дополнительной запоминающей матрицы, входы которой соединены с выходами элементов И первой и второй групп, третьи входы элементов И первой группы и вторые входы элементов И второй группы объединены и подключены к соответствующим выходам блока оперативной памяти, информационные входы которого соединены с выходами арифметического блока, управляющий вход блока оперативной памяти соединен с первым выходом блока управления, второй выход которого подключен к управляющим входам группы генераторов случайных чисел, выходы блока оперативной памяти подключены к соответствующим входам дополнительной запоминающей матрицы, соответствующие выходы

656067 которой соединены с информационными входами элементов ИЛИ вЂ” НЕ, выходы которых подключены к другим входам блока регистрации, управляющий вход которого подключен к третьему выходу блока управления, соответствующие выходы запоминающей матрицы соединены со входами блока сопряжения, выходы которого подключены к третьим входам элементов И второй группы, соответствующие выходы первой группы блока управления соединены со входами группы генераторов случайных чисел.

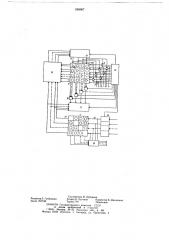

На чертеже изображена функциональная схема устройства для моделирования сетевых графиков.

Устройство для моделирования сетевых графиков содержит запоминающую матрицу 1, в ячейках которой размещены элементы памяти 2 и 3, дополнительную запоминающую матрицу 4, в ячейках которой, исключая ячейки одной из диагоналей, размещены элементы памяти 5, через строки запоминающей матрицы проложены шины выбора операций 6 и шины ограничений на одновременность 7, первую группу элементов

И 8, вторую группу элементов И 9, блок управления 10, через столбцы матрицы 1 проложены шины анализа связей 11 и шины продолжительности выполнения операций 12.

Элементы памяти 2 подключены к шинам 6, 7, 1, а элементы памяти 3 — к шинам 12 (подключение па чертеже не показано). Через строки дополнительной запоминающей матрицы 4 проложены шины отказов 13, которые подключены к группе генераторов случайных чисел 14. Элементы памяти 5 подключены к шинам 13 (на чертеже подключение не показано). Выходы строк матриц

1 и 4 подключены к арифметическому блоку

15. Выходы элементов ИЛИ вЂ” НЕ 16 и выходы строк дополнительной запоминающей матрицы 4 подключены к входам блока регистрации 17. Выходы ячеек дополнительной запоминающей матрицы 4 через блок сопряжения 18 подключены к шинам отказа 13 и элементам И 9 второй группы,причем выход ячейки п-го столбца матрицы 4 подключены к шине 13 одноименной строки матрицы 4 и к соответствующему элементу

И 9 второй группы. Выходы группы генераторов случайных чисел 14 через шины отказов 13 и блок сопряжения 18 подключены к соответствующим элементам И 9 второй группы. Выходы управляющих шин блока управления 10 подключены к входам группы генераторов случайных чисел 14. Выходы арифметического блока 15 подключены к входам блока оперативной памяти 19. Выходы блока оперативной памяти 19 через шины

12 подключены к элементам памяти 3 диагональных ячеек запоминающей матрицы 1 и к элементам И 8 первой группы.

Устройство работает следующим образом, Каждой строке и каждому столбцу за5

55 поминающих матриц 1 и 4 соответствует один элемент моделируемого процесса. При этом перечень элементов, соответствующий строкам сверху вниз, одинаков с перечнем элементов, соответствующим столбцам слева направо. В общем случае, если процесс состоит из m элементов, необходимо иметь квадратные матрицы с m строками и m столбцами. В элементы памяти 2 и 5 известным способом вносится информация, отображающая логическую взаимосвязь двух рассматриваемых элементов процесса, находящихся на пересечении одной строки и одного столбца матрицы. Также вносится информация в элементы памяти 2 и 5 о наличии ограничений на одновременность выполнения элементов процесса.

Перед началом процесса моделирования сигналом с блока управления 10 включается блок регистрации 17. При подаче сигнала на шины 6 и 7 через группы элементов И 8 и 9 включается группа генераторов случайных чисел 14. Генераторы случайных чисел группы 14 подают в случайные моменты времени импульсы случайной длительности в соответствии с заданным законом распределения времени пребывания элементов процесса в состоянии отказа с учетом времени поиска отказа и его устранения. Одновременно информация, занесенная в элементы памяти 2 запоминающей матрицы 1, передается в элементы ИЛИ вЂ” HE 16. Элементы

ИЛИ вЂ” НЕ 16 анализируют логические связи между элементами процесса и при отсутствии такой связи выдают соответствующие сигналы в блок регистрации 17. По истечении времени, заданного для выполнения элемента процесса, сигналом с блока управления 10 отключаются элементы И групп 8 и 9 п-й строки запоминающей матрицы 1, которая соответствует элементу, выполнение которого имитируется. Одновременно отключается соответствующий выполненному элементу элемент ИЛИ вЂ” НЕ 16. Неотключенные элементы ИЛИ вЂ” НЕ вновь анализируют логические связи между оставшимися элементами и процесс продолжается подачей сигнала по шинам 6 и 7 по описанному выше способу.

Если во время имитации выполнения некоторого элемента процесса группа генераторов случайных чисел 14 выдаст в соответствующую шину отказа 13 сигнал об отказе, то этот сигнал передается в блок регистрации 17. Одновременно сигнал об отказе через блок сопряжения 18 подается к соответствующему элементу группы И 9. Таким образом, если зависимость между отказавшим элементом и остальными представляет собой ограничение на одновременность, то соответствующий элемент группы И 9 закроется и тем самым будет дано разрешение на выполнение зависимого элемента. Кроме того, с элементов памяти 5 строки матрицы 4 сигнал об отказе через блок

656067

1О

20

40 сопряжения 18 подается в шину отказа 13, соответствующую элементу, который зависит от отказавшего.

Таким образом, в блоке регистрации 17 производится регистрация элементов, выполняемых как без отказов, так и с независимыми или зависимыми отказами. В ходе моделирования выполняется число реализаций исследуемого процесса. При этом сигналы по шинам 6, 7 и 13 подаются в арифметический блок 15, в котором выполняются следующие операции: определение среднего времени пребывания в состоянии отказа каждого элемента, определение среднего времени безотказного выполнения каждого элемента, определение вероятности отказа при выполнении каждого элемента и определение среднего времени, потребного на выполнение каждого элемента с учетом вероятного. времени нахождения элемента в состоянии отказа. Результаты расчета переносятся в блок оперативной памяти 19.

После окончания моделирования производится анализ информации, записанной в блоке регистрации в ходе моделирования и вносятся необходимые поправки в логические зависимости между элементами процесса, производится стирание старой информации в элементах памяти 2 и 5 и запись новой информации, извлеченной из блока регистрации 17. Затем включается блок оперативной памяти 19 и информация по продолжительности выполнения элементов процесса переносится в элементы памяти 3 диагональных ячеек запоминающей матрицы 1.

Для получения окончательной информации по моделированию выполняется контрольная реализация процесса. При этом группа генераторов случайных чисел 14 отключается и включается блок оперативной памяти 19. Элементы групп И 8 и 9 включаются с блока управления 10, а отключение их производится с блока оперативной памяти

19 в фиксированные моменты времени, чем имитируется окончание выполнения элементов процесса. В ходе контрольной реализации в блоке регистрации 17 регистрируется окончательная модель процесса.

Благодаря введению новых блоков связей между ними повысилась точность моделирования.

Формула изобретения

Устройство для моделирования сетевого графика, содержащее блок управления, первая группа выходов которого подключена к первым и вторым входам элементов И первой группы, первым входам элементов И второй группы, вторая группа выходов блока управления соединена с управляющими входами элементов ИЛИ вЂ” НЕ,и запоминающую матрицу, отличающееся тем, что, с целью повышения точности устройства, оно содержит дополнительную запоминающую матрицу, арифметический блок, блок оперативной памяти, блок сопряжения, блок регистрации и группу генераторов случайных чисел, выходы которых подключены к соответствующим входам запоминающей матрицы, выходы которой соединены с одними входами блока регистрации и арифметического блока соответственно, другие входы арифметического блока подключены к соответствующим выходам дополнительной запоминающей матрицы, входы которой соединены с выходами элементов И первой и второй групп, третьи входы элементов И первой группы и вторые входы элементов И второй группы объединены и подключены к соответствующим выходам блока оперативной памяти, информационные входы которого соединены с выходами арифметического блока, управляющий вход блока оперативной памяти соединен с первым выходом блока управления, второй выход которого подключен к управляющим входам группы генераторов случайных чисел, выходы блока оперативной памяти подключены к соответствующим входам дополнительной запоминающей матрицы, соответствующие выходы которой соединены с информационными входами элементов ИЛИ вЂ” HE, выходы которых подключены к другим входам блока регистрации, управляю ций вход которого подключен к третьему выходу блока управления, соответствующие выходы запоминающей матрицы соединены со входами блока сопряжения, выходы которого подключены к третьим входам элементов И второй группы, соответствующие выходы первой группы блока управления соединены со входами группы генераторов случайных чисел.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 368620, кл. G 06 G 7/48, 1970.

2. Авторское свидетельство СССР № 368602, кл. G 06 F 9/00, 1970.

656067

Составитель И. Дубинина

Редактор Э. Губницкая Техред О. Луговая Корректор Е. Дичинская

Заказ 1527/40 Тираж 779 Подписное

LlHHHfIH Государственного комитета СССР по делам изобретений и открьпий

113035, Москва, Ж-35, Раушская наб:, д. 4/5

Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4