Устройство для управления оперативным накопителем

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических еесвублик

:- i::àâ l (51) М. Кл. (61) Дополнительное к авт. свид-ву— (22) Заявлено 22.04.77 (21) 2478434/18-24 с присоединением заявки №вЂ” (23) Приоритет— б 11 С 7/00

Государстееииый кюютет

СССР аа делам изооретеиий и открытий

Опубликовано 05.04.79. Бюллетень № 13

Дата опубликования описания 05.04.79 (53) УДК681.327.

66 (088.8) (72) вторы изобретения

Л. П. Грузнов, М. Я. Дроздов, В. П. Карпычев и Ю. К. Кутьин

Ивановский научно-исследовательский институт хлопчатобумажной промышленности (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ

ОПЕРАТИВНЫМ НАКОПИТЕЛЕМ

Изобретение относится к области вычислительной техники и может быть использовано при построении запоминающих устройств ЦВМ.

Известны устройства для управления оперативным накопителем, содержащие регистры адреса и числа, дешифраторы адреса, усилители считывания и блок управления.

Одно из известных устройств для управления оперативным накопителем содержит регистр адреса, соединенный с дешиф- 10 ратором адреса, регистр числа, соединенный с ключевыми элементами, блок управления и управляющие шины (1).

Недостатком устройства является его относительная сложность.

Наиболее близким техническим решением к данному изобретению является устройство для управления оперативным накопителем, которое содержит регистр адреса, подключенный через адресные усилители к дешифраторам адреса, усилители считывания, 2Ц элемент ИЛИ, ключевые элементы, соединенные со входами регистра числа, блоком управления, одними входами регистра адреса и управляющими шинами, дополнительный счетчик и узел задания режима работы, входы которого подключены к управляющим шинам, а выходы — ко входам ключевых элементов и дополнительного ключевого элемента, выходы которого соединены со входами элемента ИЛИ, и разрядные шины (2) .

Известное устройство обеспечивает возможность работы управляемого им оперативного накопителя в двух режимах: комплексном и автономном. Комплексный режим соответствует обычному режиму работы оперативного накопителя в составе ЗВМ. В автономный режим оперативный накопитель может быть переведен по команде внешнего устройства, в частности, процессора вычислительной машины. В этом режиме устройством обеспечивается самостоятельная запись в оперативный накопитель спорадически посгупающих от внешнего источника сообщений, причем эти сообщения размещаются в последовательных ячейках оперативного накопителя. После записи сообщений в каждую из ячеек оперативного накопителя, он автоматически переключается на режим комплексной работы.

Однако в ряде применений алгоритм предварительной обработки поступающей с дат656106

2О

Зо

3 чиков информации очень примитивен: он заключается в увеличении на единицу содержимого счетчика, которому соответствует поступившее сообщение. Так,например, в ткацких станках при поступлении сообщений о срабатывании датчиков выработки обрыва основы и обрыва утка какого-либо ткацкого станка должно быть увеличено на единицу содержимое соответствующих счетчиков для рассматриваемого станка. В этом случае использование известного устройства для управления оперативным накопителем нецел есооб разно.

Целью изобретения является расширение области применения устройства за счет осуществления счета и суммирования спорадически поступающих от внешнего источника сообщений.

Поставленная цель достигается тем, что устройство содержит элемент задержки, вход которого соединен с выходом элемента ИЛИ, первый и третий выходы — с блоком управления, четвертый выход — со входами установки в нуль регистров адреса и числа, а второй выход — с дополнительным счетчиком, выходы дополнительного ключевого элемента соединены с другими входами регистра адреса, а выходы усилителей считывания через ключевой элемент соединены с разрядными шинами устройства.

Указанные отличия позволяют осуществить счет и хранение в ячейках управляемого оперативного накопителя сумм числа поступивших сообщений, имеющих одинаковый код. При этом двоичному коду поступившего сообщения ставится в соответствие номер ячейки памяти оперативного накопителя, в которой хранится сумма счета поступивших сообщений, имеющих такой код.

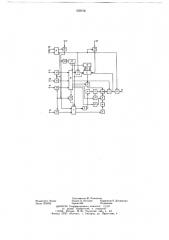

На чертеже представлена структурная схема предложенного устройства.

Устройство содержит регистры адреса 1 и числа 2. Регистр адреса 1 соединен через адресные усилители 3, дешифраторы адреса 4 с ключевыми элементами 5. Формирователи 6 и. усилители считывания 7 соединены с блоком управления 8. Узел 9 задания режима работы соединен с дополнительным ключевым элементом 10 и ключевыми элементами 11, Дополнительный счетчик 12 соединен с регистром числа 2 и с одним из выходов элемента задержки 13, вход которого соединен с выходом элемента ИЛИ 14. Для соединения устройства с вычислительной машиной и источником информации служат разрядные, информационные, адресные и управляющие шины 15 — 23.

Ключевые элементы 5, часть формирователей б и усилители считывания 7 соединены с управляемым оперативным накопителем 24.

Устройство работает следующим образом.

В зависимости от состояния узла 9 задания режима работы оно обеспечивает функционирование управляемого оперативного накопителя или в комплексном режиме совместно с вычислительной машиной как обычное ОЗУ, или в автономном режиме, принимая и суммируя поступающие на вход шины

17 устройства сообщения. Перевод. узла 9 задания режима работы в комплексный режим осуществляется подачей импульса из устройства управления вычислительной машины на управляющую шину 22 устройства.

В этом случае на одном выходе узла 9 появляется разрешающий потенциал, который открывает ключевые элементы 11, а на другом выходе узла 9 появляется запрещающий потенциал, который закрывает дополнительный ключевой элемент 10.

Открытые ключевые элементы 11 обеспечивают работу накопителя 24 в составе машины, когда из ее устройства управления в необходимой временной последовательности поступает: адресная информация на адресные шины 18, разрядная числовая информация на шину 16, управляющие сигналы записи или чтения на управляющие шины 20 или 21. По этим сигналам блок 8 управляет процессами в циклах записи или чтения соответствующей ячейки памяти накопителя 24. В конце циклов блок 8 выдает импульсы установки в нуль регистров адреса 1 и числа 2, импульс конца обращения, поступающий на шину 19 и далее в машину.

В конце цикла чтения считываемая из ячейки накопителя 24 числовая разрядная информация выдается по шинам 15 на разрядный выход устройства.

Перевод накопителя 24 из режима комплексной работы в режим автономной работы производится импульсом, поступающим по шине 23 из устройства управления вычислительной машины. В этом случае управляющие. потенциалы на выходах узла 9 меняют знаки на обратные. В результате ключевые элементы 11 закрываются, а дополнительный ключевой элемент 10 открывается разрешающим потенциалом.

При этом импульсный код сообщения от внешнего источника по шине 17 через открытый элемент 10 поступает на регистр адреса 1, устанавливая на нем соответствующий адрес ячейки памяти накопителя 24.

Одновременно импульсный код сообщения поступает на элемент ИЛИ 14, который формирует одиночный импульс поступления информации.

Этот импульс подается на вход элемента задержки 13. С его первого выхода, после необходимой временной задержки в блок управления 8 выдается управляющий импульс чтения, по которому блок 8 осуществляет цикл чтения содержимого установленной ячейки памяти накопителя 24.

Цикл чтения заканчивается выдачей на регистр числа 2 содержимого этой ячейки

656106

5 памяти. Выдачи считанного числа на шину

15 и сброса в нуль триггеров регистров адреса 1 и числа 2 не происходит, так как ключевые элементы 11 закрыты. Импульс конца обращения по той же причине на шину 19 устройства не выдается.

Затем со второго выхода элемента задержки 13 с задержкой равной времени цикла чтения на счетный вход дополнительного счетчика 12 выдается импульс счета. В результате этого содержимое регистра числа

2, который вместе со счетчиком 12 образует сумматор, увеличивается на единицу. Таким образом, в регистре числа 2 осуществляется суммирование числа сообщений.

После окончания процесса счета с третьего выхода элемента задержки 13 в блок

8 выдается управляющий импульс записи.

По этому импульсу блок 8 осуществляет цикл записи суммы счета, имеющейся в регистре числа 2, в ту же ячейку памяти накопителя, адрес которой остается установленным на регистре адреса 1.

После задержки на время цикла записи с последнего выхода элемента задержки 13 выдается импульс установки в нуль регистров адреса 1 и числа 2, поступающий на соответствующие входы триггеров этих регистров. Тем самым устройство подготавливается к приему следующего импульсного кода сообщений. Прием и суммирование поступающих сообщений производится подобным образом до тех пор, пока накопитель 24 не будет переведен в комплексный режим работы. При этом накопленные суммы поступивших за определенное время сообщений обычным путем с помощью ЭВМ могут быть использованы для дальнейших расчетов.

Расчеты показывают, что использование предложенного устройства позволяет увеличить точность учета выработки ткацких станков до одной уточины каждого станка и до дециметра уточной или перематываемой нити сновальных, шлихтовальных, прядильных и т. п. машин.

Формула изобретения

Устройство для управления оперативным накопителем, содержащее регистр ад10 реса, подключенный через адресные усилители к дешифраторам адреса, усилители считывания, элемент ИЛИ, ключевые элементы, соединенные со входами регистра числа, блоком управления, одними входами регистра адреса и управляющими шинами, допол15 нительный счетчик и узел задания режима работы, входы которого подключены к управляющим шинам, а выходы — ко входам ключевых элементов и дополнительного ключевого элемента, выходы которого соедине20 ны со входами элемента ИЛИ, и разрядные шины. огличаюи1ееся тем, что, с целью расширения области применения устройства за счет осуществления счета и суммирования спорадически поступающих от внешнего источника сообщений, оно содержит элемент

25 задержки, вход которого соединен с выходом элемента ИЛИ, первый и третий выходы— с блоком управления, четвертый выход — со входами установки в нуль регистров адреса и числа, а второй выход — с дополнительным счетчиком, выходы дополнительно30 го ключевого элемента соединены с другими входами регистра адреса, а вь1ходы усилителей считывания через ключевой элемент соединены с разрядными ц.инами устройства

Источники информации, принятые во вни35 мание при экспертизе

1. Преснухин Л. Н., Нестеров П. В. Цифровые вычислительные машины. M., «Высшая школа», 1974, с. 19.

2. Авторское свидетельство СССР № 463145, кл. G 11 С 7/00, 29.06.73.

656106

Редактор С. Равна

Заказ 1535/42

Составитель Ю. Розенталь

Техред О. Луговая Корректор Е. Дичинская

Тираж 680 Подписное

ЦН И И П И Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4