Формирователь импульсов

Иллюстрации

Показать всеРеферат

Тп ) ЬМ Й 2

Союз Советскии

Социалистицескиа

Республик (6i) Дополнительное к авт. саид-ву (22) Заявлено 22.12.75(21) 2300940/18-21 с присоединением заявки № (23) Приоритет—

Опубликовано 05,04.79.Бюллетень № 13

Дата опубликования описания 07.04.79 (51) М. Кл

Н 03 К 5/02

Гооударственный комитет

СССР оо делам изооретений и открытий (53) УЙК 621,373 (088,8) (72) Авторы изобретения

А. 3. Иванников, А. L1 Кравцов и Ю. Т. Федоров (71) Заявитель (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ

Изобретение относится к автоматике и вычислительной технике и предназначено для подачи тока в нагрузку при одном определенном сочетании логических сигналов на входах и обеспечения регулируемого потенциала на выходе для всех остальных комбинаций логических сигналов на входе. Оно может быть, в частности, использовано для выбора строки в матрице памяти ОЗУ и установления потенциала хранения для ячеек матрицы.

Известен формирователь импульсов, в котором вход соединен с эмиттером входного транзистора, база которого через резистор подключена к положительному полюсу источника питания, а коллектор соединен с базой переключающего тран1 зистора, Коллектор переключающего транзистора через резистор связан с нагрузкой и амиттером повторительного транзистора. Эмиттер переключающего транзистора соединен с базой управляющего транзистора и через резистор — c его эмиттером, с отрицательным полюсом источника питания и с нагрузкой. Коллектор управляющего транзистора связан с базой повторительного транзистора, с коллектором ускоряющего транзистора и через резистор — с положительным полк

5 с©ом источника питания. Коппектор повто,рительного транзистора .соединен с базой ускоряющего транзистора, эмиттер которого подключен к положительному полюсу источника питания (1).

Недостатком данного формирователя является относительная сложность построения и, как следствие, пониженная надежность и невысокая степень интеграции его в интегральном исполнении.

Наибонее близким к данному изобретению является двухвходовый формирователь импульсов, содержащий переключающий транзистор, управляющий и повторительный транзисторы, соединенные таким образом, что эмиттер переключающего транзистора соединен с баЗой управляющего транзистора и через резистор — с его

Ь эмиттером, коллектор управляющего тран»

656192 зистора подключен к базе повторительного транзистора и через резистор - к положительному полюсу источника питания, в то время как коллектор переключающего транзистора связан с эмиттером повторительного транзистора(2) .

Недостатком формирователя являются

:"тносительно низкое быстродействие и . алая нагруэочная способность.

Белью изобретения является повышение 36 быстродействия формирователя и увеличение его нагруэочной способности.

Поставленная цель достигается тем, что в формирователь импульсов, содержаб щий Ч ° входных цепей, два транзистора разной проводимости в тиристорном вкцючении и два резистора, введена N - 1 пара транзисторов разной проводимости в тиристорном включении, причем входы формирователя подключены к соединению 29 коллектора р-л-р транзистора с базой

rl-p-rl транзистора,. коллекторы р-р-и и базы

Р-И-р транзисторов соединены вместе, эмиттеры и-р-и транзисторов подключены к шине нулевого потенциала, а эмиттеры

p-n-p транзисторов объединены и через первый резистор подключены к выходу .формирователя, который через второй резистор соединен с шиной питания.

Формирователь импульсов показан на Зо чертежах.

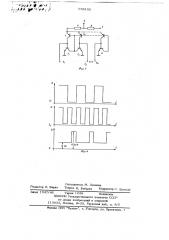

На фиг. 1 изображен двухвходовый двухканальный формирователь; на фиг. 2отдельный элеМент; на фиг. 3 — формирователь импульсов для выборки строки в матрице памяти ОЗУ, содержащий К входных цепей; на фиг. 4 — временные диаграммы прохождения импульсных сигналов на входах и выходе устройства:

Элемент, изображенный на фиг. 2, содержите-р-г1 переключающий транзистор и р-и-р инжектируюший транзистор, Вход формирователя подключен к объединению базы переключающего и коллекто45 ра инжектируюшего транзисторов, база инжектируюшего транзистора — к коллектору переключающего, эмиттер которого соединен с общей шиной. Двухвходовый двухканальный формирователь может осу50 шествлять выборку строки в матрице памяти ОЗУ на 256 бит (организация матрицы 16 строк х 16 разрядов). Для выборки строки в матрице памяти на

1024 бит (органиэация матрицы 32 строки х 32 разряда) к двухканальному формирователю подключается еше один элемент (канал), показанный на фиг. 2. B результате получается трехвходовый трехканальный формирователь, Бля выборки строки в матрице памяти ОЗУ с более высокой организацией требуется подключение соответствующего числа элементов (каналов), показанных на фиг, 2.

Формирователь содержит в каждом канале и-р-и переключающий транзистор 1,, база которого объединена с коллектором инжектируюшего транзистора 2

К ним подключен вход формирователя31 .

Коллектор транзистора 1 объединен с базой транзистора 2 . Эмиттер транзистора 1, подключен к обшей шине. Эмит ðì транзи ров 21, 22 - 2и соединены и через резистор 4 подключены к выходу 5 формирователя, к которому через резистор 6 подключен источник питания 7.

Базы транзисторов 2 1 ... 2„и колneK pI тра эистор в l1, 1, - 1м объединены.

Рассмотрим работу устройства на примере двухканального двухвходового формирователя.

Пусть ко входам 3 и 3, приложен высокий потенциал. Через переход базаэмиттер транзисторов 1 . и 1 протекает суммарный коллекторный ток инжектируюших транзисторов 2 и 2 обоих каналов и ток,текущий по соответствующему входу. Транзисторы 2 и 2 > открываются, и ток от источника питания 7 через резисторы 6 и 4, переход эмиттер- база транзисторов 2, и 2> насыщенные транзисторы 1 и 1 замыкается на общую. шину.

Уровень напряжения на выходе 5 формирователя равен падению напряжения на резисторе 4, транзисторах 1, 1 и

2, 2, и допускает регулирование изменением величины резистора 4.

Если на вход 31 подать высокий потенциал, а на вход 3 низкий, то состояние левого канала не изменяется.

Ток от источника питания 7 протекает через резисторы 6 и 4, транзисторы

1 и 2 левого канала ыа общую .. шину.

Инжектируемый транзистором 2 правого канала ток замыкается на общую шину через открытую низким потенциалом входную цепь по входу 3 . На выходе 5 устройства устанавливается уровень напряжения за счет тока, протекающего через окрыляй левый канал.

656192

Состояние выбора, при котором ток протекает в нагрузку, соответствует низкоЪ му уровню потенциалов на входах 3 и 3 . Ток, инжектируемый транзисторами 2, левого и 2> правого каналов, зааея через входы 31 и 32 на общую шину. Низкий коэффишеент усиления транзисторов 2 и 2 ограничивает ток, протекающий по цепи: резистор 4, транзисторы 2 и 2 и входы 3, 3 на общую шину. Основной ток от источника питания 7 через резистор 6 протекает к нагрузке, подключенной к выходу.

Следовательно, только определенная комбинация входных сигналов (логический

"0" на входах З,е и 3 ) устройства обеспечивает передачу тока в нагрузку.

Остальные сочетания входных сигналов определяют появление на выходе устройства напряжения, соответствующего потенциалу хранения в ячейках памяти.

Таким образом, чтобы обеспечить протекание тока в нагрузку, необходимо лишь запереть транзисторы 1, 1 ... 1„ формирователя. Так существенно повышается быстродействие устройства.

Устройство может быть использовано ие только как формирователь, но и как источник напряжения хранения для ячеек памяти матрицы, что расширяет его функциональные возможности.

Интегральное исполнение устройства на р-л-р и n-p-еч транзисторах с совмещенными областями позволяет умень шить число элементов, межсоединений и количество контактных соединений, что способствует повышению надежности уст6 ройства. Выполнение активных элементов устройства в обшей изолированной области приводит к повышению степени его интеграции на кристалле.

5 Использование резисторов в выходной пепи определяет широкий диапазон нагрузочных токов формирователя, 16 Формула изобретения

Формирователь импульсов, содержащий

N входных цепей, два транзистора разной: lIpoBQBHMocTH B тиристорном включении и два резистора, о т л и ч а ю— шийся тем, что, с целью повьппения быстродействия и нагрузочной способности, в него введена М -1. пара транзисторов разной проводимости в тири @ сторном включении, причем входы формирователя подключены к соединению кол» лектора р-и--р транзистора с базой д-р-ее транзистора, коллекторы и-р-и и базы р-и-р транзисторов соединены вмес те, эмиттеры и-р-ее транзисторов подключены к шине нулевого потенциала, а

1 эмиттеры р-и-р транзисторов объединены и через первый резистор подключены к выходу формирователя, который через второй резистор . соединен с шиной питания, Источники информации, принятые Bo .

<внимание при экспертизе

1. Шагурин И. И. Транзисторно-тран33, зисторные логические схемы, М, Советское радио, 1974, с. 4-2, рис, 1, 29а.

2. Авторское свидетельство СССР

N. 496885, кл. Н 03 К 5/02.

Зр

656192 уг

Риг. 3

Х ф

tl

Составитель М. Леонова

Редактор Н. Вирко Техред H. Вабурка Корректор С. Шекмар

Заказ 1547/46 Тираж 1059 Подписное

IIHHHHH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 1