Селектор импульсов

Иллюстрации

Показать всеРеферат

био. :.(".. :: - 4, Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ ((»656197

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (б1) Дополнительное к авт. свил-ву(22) Заявлено 19.10.77 (21) 2534849/18-21 с присоединением заявки № (23) ПриоритетОпубликовано 05.04.79,Бюллетень №13

Дата опубликования описания09.04.79 (51) М. Кл.

Н 03 К 5/18

Государственный комитет

СССР по делам изобретений и открытий (53) УЙК 621.374..33 (088.8 ) (72) Авторы изобретения

А. А. Маслов, В. Г. Тодуров и Г. И. Окользин (71) Заявитель (54) СЕЛЕКТОР ИМПУЛЬСОВ

Изобретение относится к импульсной технике.

Известен селектор импульсов, содержащий входной вентиль, блок управления входным вентилем. В состав блока управления входит счетчик времени, одновибратор и блок ложки. Импульс входного сигнала запускает счетчик, который запускает одновибратор с задержкой, длительность импульса которого равна периоду селектируемого импульса. Этот сигнал соответствующим образом управляет входным вентилем (1).

Недостатком селектора является его сложность.

Наиболее близким по технической сущности к изобретению является селектор импульсов, содержащий многосекционную линию задержки, вход которой через усилитель соединен с входной шиной, а выходы секции через N пороговых элементов и включенных последовательно с ними инверторов подключены к первым входам N логических элементов И, выходы которых соединены со входами порогового обнаружителя, выход которого соединен со входом формирователя выходных импульсов (2).

Недостатком этого селектора является низкая помехоустойчивость.

Целью изобретения является повышение помехоустойчивости.

Поставленная цель достигается тем, что в селектор импульсов, содержащий многосекционную линию задержки, вход которой через усилитель соединен с входной шиной, а выходы секций через N пороговых элементов и включенных последовательно с ними инверторов подключены к первым входам

N логических элементов И, выходы которых соединены со входами порогового обнару.жителя, выход которого соединен со входом формирователя выходных импульсов, введены N дополнительных пороговых элементов, первый вход каждого из которых соединен со входом одного из пороговых элементов и 2N формирователей пороговых напряжений, входы которых соединены и подключены к дополнительному выходу многосекционной линии задержки, а выход каждого из которых соединен со вторым входом одного из упомянутых пороговых элементов, причем выход каждого дополнительного порогового

6561

97

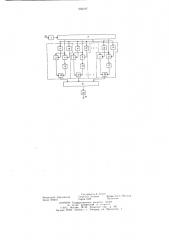

4 потенциал, который совместно с разрешающим потенциалом с соответствующего инвертора приводит к отпиранию одного из логических элементов И, находящегося в открытом состоянии до момента достижения сигналом второго порогового уровня. При достижении сигналом второго порогового уровня срабатывает пороговый элемент, и на выходе соответствующего инвертора устанавливается запрещающий потенциал, который приводит к запиранию упомянутого логического элемента И.

При одновременном срабатывании Х из

М логических элементов И пороговый обнаружитель 21 производит выделение сигнала. Параметр N (М рассчитывается из условий обеспечения требуемой достоверности приема при резких искажениях формы, приводящих к отсутствию обнаружения элементов сигнала по указанному выше правилу на М вЂ” N позициях.

Сигнал, удовлетворяющий правилам селекции, с выхода порогового обнаружителя

21 поступает на вход формирователя 22, преобразуется в нем и поступает на выход устройства.

Формула изобрегc í! J. i

Селектор импульсов, содержащий многосекционную линию задержки, вход которой через усилитель соединен с входной шиной, а выходы секций через N пороговых элементов и включенных последовательно с ними инверторов подключены к первым входам

N логических элементов И, выходы которых соединены со входами порогового обнаружителя, выход которого соединен со входом формирователя выходных импульсов, отличаюи1ийся тем, что, с целью повышения помехоустойчивости, в него введены 1х дополнительных пороговых элементов, первый вход каждого из которых соединен со входом одного из пороговых элементов и 2N формирователей пороговых напряжений, входы которых подключены к дополнительному выходу многосекционной линии задержки, а выход каждого из которых соединен со вторым входом одного из упомянутых пороговых элементов, причем выход каждого дополнительного порогового элемента подключен ко второму входу соответствующего логического элемента И.

Источники информации, принятые во внимание при экспертизе

1. Патент Великобритании Хе 1264284, кл. G 1 U, 16.02.72. элемента подключен ко второму входу соответствующего логического элемента И.

На чертеже дана структурная электрическая схема предложенного селектора.

Селектор содержит усилитель 1, секционированную линию 2 задержки, пороговые элементы 3 — 8, формирователи 9 — 14 пороговых напряжений, инверторы 15 — 17, логические элементы И 18 — 20, пороговый обнаружитель 21, формирователь 22 выходных импульсов. 10

Входной сигнал подан на входную шину 23, выходной сигнал снимается с выхода 24.

Селектор работает следующим образом.

В исходном состоянии сигналы на выходах усилителя 1, выходах секций линии 2

15 задержки, входах пороговых элементов 3 — 8 и формирователях 9 — 14 пороговых напряжений отсутствуют.

Напряжения на выходе формирователей пороговых напряжений 9, 10 равны нулю. 20

Пороговые элементы 3 — 8 находятся в закрытом состоянии, так как амплитуды входных сигналов не превышают величин пороговых уровней.

Входной сигнал в процессе распростра- 25 нения по линии задержки последовательно появляется на входах пороговых элементов

3 — 8 и входах формирователей пороговых напряжений 9 — 14. Сигнальные входы пороговых элементов подключаются последовательно к.отводам линии задержки, распределенных по ее длине. Суммарное время задержки выбирается, исходя из длительности селектируемого сигнала, а длительность задержки между соседними отводами (шаг) выбирается по правилам дискретизации с учетом скорости изменения сигнала.

Входы формирователей пороговых напряжений подключаются к опорному отводу линии задержки, на котором в момент выделения присутствует сигнал с максимальной амплитудой.

С помощью формирователей 9 — 14 производится формирование напряжений нижних и верхних границ зоны обнаружения сигнала. Формирование напряжений нижних и верхних границ производится воспроиз- 45 ведением М дискретных элементов эталонного сигнала с учетом возможного разброса амплитуд элементов селектируемого сигнала.

Пороговые напряжения на входах элементов 3 — 8 изменяются в соответствии с

50 формои,эталонного сигнала и амплитудой реального сигнала, задержанного на время t

В момент обнаружения напряжения нижних и верхних границ достигают значений, при которых амплитуды сигнала удовлетворяют условно селекции. 55

При превышении сигналом порогового уровня на выходе некоторого порогового элемента устанавливается разрешающий

2. Патент Японии М 39144, кл. 98(5) с5, 27.06.67.

656197

Составитель А. Аогюх

Редактор И..1!арховская Техрел О. Луговая Корректор С. 111екмар

3 а к аз 1548/47 Тираж l059 Полпнсноp

liHHHHH Государственного комитета СССР по делам изобретений и открьт«й

I I 3035, Москва, )К-35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4