Устройство для сравнения напряжений

Иллюстрации

Показать всеРеферат

Союэ Советскмк

Соцмалмстнческик

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИ ТИЛЬСТВУ

657406 (61) Дополнительное к авт. свил-ву (22) Заявлено 09.03.76(2!) 2332282/18-21 с присоединением заявки № (23) Приоритет—

Опубликовано 1 5.04. 7 В Бюллетень ¹14

Дата опубликования описания18.04.79 (51) М. Кл.

G05 В 1/01

Гюеударственнвй кеметет

СССР ае делам лзебретеей и аткрапмй (53) УДК Ñ>21.3 . 33 (088. 8) (72) Авторы изобретения

В. 51. Загурский и Г. И. Готлиб (71) Заявитель

11нститут эаектроники и вычислительной техники

ЛН Латвийской CCP (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ НЛПРЯЖЕНИЙ

Изобретение относится к импульсной

1технике, в частности к устройствам, в которых импульсы выдаются в момент времени, соответствующий наличию определенной характеристики входного сигнала, предназначено дпя сравнения двух электрических сигналов, например двух напряжений, и может быть использовано в системах автоматического контроля, электроизмернтельных системах, технике аналого-цифрового преобразования.

Известно устройство дпя сравнения напряжений, содержащее аифференциапьный каскад (11.

Основным недостатком этого устройства является ограничение функцпонапьных возможностей при зааанных параметрах чувствительности и недостаточное быстродействие.

Наиболее близким техническим решением к данному изобретению является устройство дпя сравнения напряжений, содержащее дифференциальный каскаа, нелинейную нагрузку, эмиттерные повторители, источники тока, смешения и опорного напряжения, транзисторы и резисторы(2).

Это устройстВо не может работать в режиме без стробирования, кроме того, оно обладает низким быстродействием, обусловленным сложностью схемы и наличием длинной цепи обратной связи.

1(ель изобретения — повышение быстео родействия устройства.

С этой целью в устройство апя сравнения напряжений, содержащее дифференциальный каскад, нелинейную нагрузку, эмиттерные повторители, источники тока, смещения и опорного напряжения, транзисторы и резисторы, введен многоэмиттерный транзистор, база которого соединена с зажимами источника опорного напряжения, коллектор соединен с нелинейной нагрузкой и через первый эмкт- терный повторитель — с базой первого транзистора, коллектор этого транзистора через второй эмиттерный TloBT<1ритепь

657406 соединен с выходным зажимом и через .резистор — с источником смешения, при этом эмиттер первого транзистора соединен с первым эмиттером многоэмиттерного транзистора, с первым источником тока и эмиттером третьего транзистора, база которого соединена с прямым выходом дифференциального каскада, эмиттер второго транзистора соединен с вторым эмиттером многоэмиттерного тран10 зистора и с вторым источником тока.

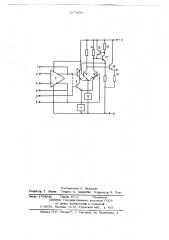

На чертеже представпена принципиапьная эпектрическая схема предлагаемого устройства.

Устройство включает в себя прямой

1S выход 1 дифференциального каскада, прямой вход 2 дифференциапьного каскада и инверсный вход 3 дифференциального каскада которые являются входами устройI

20 ства, инверсный выход 4, допопнитепьный вход 5, зажим 6 источника опорного напряжения, дифференциальный каскад 7, соответственно третий, второй и первый транзисторы 8 - 10, второй и первый

25 источники тока 11 и 12, многоэмиттерный транзистор 13, резистор 14 нелинейной нагрузки, транзистор 1 5 не линейной нагрузки, резистор 16 смещения транзистора 15 транзистор 17 эмиттерного ю

30 повторителя цепи положительной обратной связи, выходной эмиттерный повторитепь

18 и выходной зажим 19.

Устройство обеспечивает возможность . работы в следующих основных режимах: режим сравнения напряжений без гистерезиса с чувствительностью, регулируемой как по величине, так и по знаку; режим сравнения со стробированием и фиксацией выбранного логического состояния.

Дпя реализации режима сравнения без гистерезиса с регулируемой чувствительностью базу транзистора 9 подключают к выходу 1 дифференциального каскада, а зажим 6 подключают к источнику опорного напряжения, величина которого определяет чувствительность и .ее знак.

Дпя получения:максимальной стабильной чувствительности зажим 6 подключают к инверсному выходу дифференциального каскада.

В режиме сравнения с регупируемой чувствительностью, устройство работает следующим образом.:

Вход. 5 соединяют с выходом;1, а: зажим 6 соединяют с источником .онорного напряжения, равного попусумме высокого и низкого уровней напряжения на зажиче 19. Входы 2 и 3 ;шляются вхопами устройства. !1усть в исходном состоянии напряжение по входу 2 меньше по величине, чем по входу 3, и одинаково с ним по знаку. Напряжение и» прямом выходе 1 дифференциального каскада меньше опорного, транзисторы 8 и 9 заперты, а ток источников 11 и 12 переключен в нелинейную нагрузку транзистора 1 3.

Транзистор 10 выключен, поскольку напряжение на эмиттере транзистора 17 меньше напряжения на базах транзисторов 8 и 9. Напряжение на зажиме 19 устройства соответствует низкоМу уровню напряжения.

Увеличение напряжения по входу 2 приводит к увепичению напряжения на выходе 1. Когда напряжение на нем станет равным опорному, то напряжение на эмиттере транзистора 17 также станет равно опорному, и транзистор 1 0 начинает открываться, что приводит к развитию лавинообразного процесса переключения тока источника 12 за счет положительной обратной связи, реализуемой транзисторами-17 и 10, при этом транзистор 10 открыт, а транзисторы 13 и 8 заперты. На зажиме 19 устанавливается фиксированный низкий уровень напряжения. Дальнейшее увепичение напряжения по входу 2 не приводит к каким-либо изменениям на зажиме 19, ток источника 1 1 переключается в транзистор 9, на выходе эмиттерного повторителя появляется высокий уровень напряжения.

Если напряжение на входе 2 уменьшается, то при равенстве напряжений на выходе 1 и опорного, ток источника 11 начинает переключаться транзистором 9 в нагрузку транзистора 1 3, напряжение на эмиттере транзистора 17 уменьшается и по достижении напряжения на выходе 1 происходит павинообразный процесс переключения тока источника 1 2, в результате чего транзистор 10 закрывается, а транзисторы 18 и 13 включаются, на зажиме

19 напряжение достигает фиксированного высокого уровня.

Транзистор ). 5 автоматически ограничивает изменение напряжения на резисторе 14, искпючая насыщение транзистора 13. Максимальная величина ограничиваемого напряжения равна. сумме напряжения. на,переходе эмиттер-база транзистора 15; и падения напряжения на резисторе 16 при протекании коппек657406 торного тока транзистора 1 7. Отрицатепьная обратная связь между транзистс рами 15 и 17 стабипизирует режим ограничени я, что повышает на аежн ость работы и быстродействие устройства.

Скорость развития павинообразного перекгпочения не зависит от крутизны входного сигнапа, а зависит лишь от быстродействия переключатепей тока.

Выбор опорного напряжения опредепяет чувствительность устройства, поскольку напряжение на выходе 1 опредепяется напряжениями как по входу 2, tBK и по входу 3. Чувствительность устройства максимапьна, еспи опорное напряжение на зажиме 6 равно напряжению на выходе 1 при равенстве напряжений по входам 2 и 3. Поскопьку дифференциальный каскад 7 симметричный, то для подучения максимальной чувствительности устройства достаточно зажим 6 соединить с инверсным выходом 4.

В режиме сравнения со стробированием и фиксацией погического состояния вход 5 основного перекпючатепя тока используют как вход стробирования, а зажим 6 ttoltключают к источнику опорного напряжения, равному попусумме высокого и низкого уровней напряжения на зажиме 19. Уровни напряжения и вепичина сигнапа стробирования выбираются равными величине и уровням выходного сигнала устройства.

В этом режиме сравнение происходит только при воздействии высокого уровня сигнала стробирования по входу 5. Еспи низкий уровень напряжения на зажиме 19 получен в процессе сравнения, то on фиксируется до окончания стробируюшего сигнапа. При подаче низкого уровня напряжения на вход 5 ос новного перекшочатепя тока на выходе эмиттерного повторителя устанавливается также низкий уровень напряжения, а на зажиме 19 устройства- высокий уровень напряжения, независимо от вепичины сравниваемых напряжений.

Формула изобретения

Устройство для сравнения напряжений, содержащее дифференциальный каскад, непинейную нагрузку, эмиттерные повторит пи, источники тока смешения и опорного напряжения, транзисторы и ре-!

5 зисторы, о т л и ч а ю щ е е с я. тем, что, с целью повышения быстродействия устройства, в него введен многоэмиттерный TpGHBHctop, база которого соединена с зажимами источника опорного на20 пряжения, коппектор соединен с нелинейной нагрузкой и через первый эмиттерный повторитель — с базой первого транзистора, коплектор которого через второй эмиттерный повторитепь соединен с выходным зажимом, и через резистор с источником смещения, при этом эмиттер первого транзистора соединен с первым эмиттером многоэмиттерного транзистора с первым источником тока и эмиттером третьего транзистора, база которого соединена с прямым выходом дифференциапьного каскада, эмиттер второго транзистора соединен со втоЗ рым эмиттером многоэмиттерного транзистора и со вторым источником тока.

Источники информации, принятые во внимание при экспертизе

1. Журнал "Эпектроника", No 21, > 1972, с. 54-62.

2. Патент США Ю 3638041, кп. 307-247, 25.06.72.

657406

+и

Составитель Л, Федорова

Редактор Т. Янова Техред О, Андрейко Корректор M. Пож

Заказ 1794/46 Тираж 1014 Подписное

Ц1{ИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, >К-35, Раушская наб., д. 4/Г

Филиал П11П Патент, г. Ужгород, ул. Проектная, 1