Дискретный фазовращатель

Иллюстрации

Показать всеРеферат

Союз Советскмк

Социалистических

Рек;лублмк

ОП ИСАНИЕ(657591

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДВТВЛЬСТВУ (6t) Дополнительное к авт. свил-ву(22) Заявлено 17.05.76 (21) 2361255/18-21 (б! ) М. Кл. 2

Н 03 Н 7/18

Ci 06 -Т 3/00 с присоединением заявки №вЂ” (23) Приоритет

Гввудвр@твенный намнтетСССР нв делам нзабрвтеннй н 0TKpblTMN

Опубликовано15.04.79.бюллетень №14 (53) УДК 621.317. . 377(088. 8) Д.ата опубликования описания 18.04.79 (72) Авторы изобретения

Л. И. Ильченко, Ю. И. Кузьмин и М. Ф. Ярема (713 Заявитель (54) ДИСКРЕТНЫЙ ФАЗОВРАЩАТЕЛЬ

0 = А (ocosuvt+Qs nuut), Изобретение относится к измеритель ной технике и предназначено для дискретного изменения фазы входного синусои.дального напряжения от 0 до 360 в соответствии с управляющим сигналом.

Наиболее близким техническим решением к данному изобретению является дискретный фазовращатель, содержащий источники управляющего сигнала, фаэовращатель, вход которого подключен к первому входу первого умножителя сигналов, выход фазовращателя подключен к первому входу второго умножителя сигналов, выходы первого и второго умножителей сигналов подключены ко входам сумматора (11. В этом фазовращателе напряжение выходного сигнала равно где А - постоянный коэффициент;

g)- частота входного сигнала; сн ф - сигналы, поступающие на вход

1 первого и второго умножителей сигналов соответственно.

Недостатком такого устройства являет ся то, что сигналы а и в в нем пред» ставляют собой кусочнопинейные функции от величины управляющего сигнала. От клонение укаэанных функций от синусоидальных"приводит к значительному изме« нению амплитуды и нелинейному изменению фазы выходного сигнала при линейном изменении величины управлякицего сигнала. Это не позволяет получить сдвинутый по фазе синусоидальный сигнал с наименьшими амплитудными и фазовыми искажениями.

Целью изобретения является получе ние дискретных фазовых сдвигов синусо идального сигнала с наимейьшими ампли тудными и фазовыми искажениями.

Это достигается тем, что в предлагаемый дискретный фаэоврашатель вве дены импульсный генератор, два элемента совпадения, два делителя частот ы изб)триггеров каждый, два блока диффе ренцирования, два ключа, две запоминюо щие емкости, фильтр низких частот, при»

657591 чем выход импульсного генератора подключен непосредственно ко входу первого делителя частоты и через первый элемент совпадения ко входу второго делителя частоты„ второй вход первого элемента совпадения подключен к выходу источника управляющих сигналов, выход, первого делителя частоты через фильтр низких частот соединен со вторыми входами первого и второго ключа, выход вто- 1О рого делителя частоты подключен непосредственно к первому входу второго элемента совпадения и через первый блок дифференцирования к первому входу первого ключа, выход которого соединен с пер- И вой запоминающей емкостью и со вторым входом первого умножителя сигналов, вы ход (ги-1)-го триггера второго делителя частоты через второй элемент совпадения и второй блок дифференцирования подключен к первому входу второго ключа, выход которого соединен со второй запоминающей емкостью и со вторым входом второго умножителя сигналов.

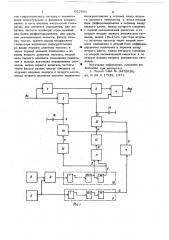

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, иллюстрирующие его работу.

Дискретный фазовращатель содер;.кит фазовращатель 1, первый и второй умножители сигналов 2 и 3, сумматор 4, импульсный генератор 5, первый делитель час оты 6, фильтр низких частот 7, источник управляющего сигнала 8, элемент совпадения 9, второй делитель частоты

10, элемент совпадения 11, первый и второй блоки дифференцирования 12, 13, первый и второй ключи 1 4, 1 5, первую и вторую запоминающие емкости 16, 17.

Вход фазовращателя 1 подключен к первому входу умножителя сигналов 2.

Выход фазовращателя 1 подключен к первому входу умножителя сигналов 3. Выходы умножителей сигналов 2 и 3 подключены ко входам сумматора 4. Выход импуль45 сного генератора 5 подключен непосредственно ко входу делителя частоты 6 и через элемент совпадения 9 ко входу делителя частоты 10. Второй вход элемента О совпадения 9 подключен к выходу источника управляющих сигналов 8. Выход дели- теля частоты 6 через фильтр низких -частот соединен со вторыми входами ключей

1 4 и 1 5. Один выход делителя частоты .10 подключен непосредственно к первому входу элемента совпадения 11 и через блок дифференцирования 12 к одному из входов ключа 14, выход которого соединен с запоминающей емкостью 16 и со вторым входом умножителя сигналов 2.

Другой выход делителя 10 (выход гп-1)го триггера) через последовательно соединрнные элемент совпадения 11 и блок дифференцирования 13 подключен к одному из входов ключа 15, выход которого соединен с запоминающей емкостью 17 и со вторым входом умножителя,сигналов 3.

Устройство работает следующим обра3DM.

Входной синусоидальный сигнал поступа1 ет на вход фазовращателя 1 и первый вход умножителя сигналов 2, где он умножается на, коэффициент, пропорциональный величине сигнала 6, поступающего на втоо рой его вход. Сдвинутый на 90 входной сигнал с выхода фазовращателя 1 поступает на первый вход умножителя сигналов 3, где он умножается на коэффициент, пропорциональный величине сигнала 3, поступающего на второй его вход. Умноженные сигналы поступают.на сумматор 4, в котором складываются„и суммарный сигнал — это выходной сигнал устройства.

Сигналы а и в, пропорциональные соответственно синусу и косинусу одной и той же величины, получаются следующим образом. Сигнал с .выхода импульсного генератора 5 делится в триггерном делителе 6, содержащем .А триггеров, и поделенный импульсный сигнал (фиг. 2а) преобразуется в синусоидальный в фильтре низкой частоты 7 (фиг. 26). При отсутствии сигнала с выхода источника управляющих сигналов 8, через схему совпадения 9 пройдут сигналы импульсного генератора 5 на вход делителя 10 {который также содержит Ф триггеров), на его выходе появятся поделенные сигналы (фиг. 26),, идентичные выходным сигналам делителя

6 (фиг. 2а). С выхода (.Ф-1)-го триггера {фиг. 2в) делителя 10 и с выхода ,ф-го триггера делителя 10 (фиг. 2а) сигналы поступают на элемент совпадения

1 1, на выходе которого появляется сигнал (фиг. 2а) со скважностью, равной четырем, о и положительный фронт его на 90 отстоит от положительного фронта сигнала с выхода, щ-r o триггера делителя 1 О. Блоки дифференцирования 12 и 13 формируют короткие импульсы в моменты, соответствующие положительным фронтам импульсов с выхода;Ф-го триггера делителя 1 0 (фиг, 2е) и с выхода элемента совпаде ния 11 (фиг. 2ж). Зти короткие импульсы отстоят один от другого на четверть периода выходной частоты делителей 6 и

657591

10. Выходные сигналы блоков дифференцирования 12 и 13 поступают на первые входы ключей 14 и 15 соответственно. На вторые входы ключей 14 и 15 поступает синусоидальный сигнал с выхода фильт- 5 ра низкой частоты 7 и с частотой, равной частоте выходного сигнала делителей

6 и 10. На выходах ключей 14 и 15 появляются короткие импульсы с амплитудой, равной амплитуде выходного сигналафильтра низкой частоты 7 в моменты открыва »»ия ключей 14 и 15 (в моменты поступления на их входы коротких импульсов). Эта амплитуда запоминается емкостями 16 (фиг. 2з) и 17 (фиг. 2и) и передается на вторые входы умножителей сигналов

2 и 3 соответственно. B случае, когда управляющий сигнал с блока 8 отсутст-. вует, выходные сигналы делителя 6 и делителя 10 (выход и»-го триггера) не сдвинуты по фазе один относительно другого. При наличии сигнала управления фаза выходного сигнала делителя 10 (вьтход N-го триггера) сдвигается относи тельно выходного сигнала делителя 6 на величину, пропорциональную количеству импульсов, поступающих с выхода источника управляющего сигнала 8. Соответственно меняются амплитуды импуль36 сов с выходов ключей 14 и 15.

Так например, при отсутствии управ> ляющего сигнала на выходе блока дифференцирования 12 появлялся бы импульс в момент, соответствующий нулевому зна35 чению сигнала с выхода фильтра низкой частоты 7 (момент 1 фиг. 2б), а на выходе блока дифферейцирования 13— в момент, соответствующий максимуму сигнала с выхода фильтра низкой часто/ ты 7 (момент времени tZ, фиг. 2б}.

Соответственно, на выхоце ключа 14 будет нулевой сигнал, а на выходе ключа

15 — максимальный. Коэффициент Сд = 0, () мс кс"

4%

В рассматриваемом на временных ди аграммах случае управляющий сигнал сдвинул по фазе сигнал с выхода делителя 10 фиг. 2r) относительно сигнала с о выхода делителя 6 (фиг. 2a), на 30 .

Тогда импульс с выхода блока дифференцирования 12 (фиг. 2е) откроет ключ 14 в момент времени (фиг. 2б), и амплитуда выходного сигнала ключа 14 соответствует значению синусоидального выходного сигнала фильтра низкой частоты

7 в этот момент где U (С ) — значение выходного сигнала фильтра низкой частоты в момент времениф

U максимальное значение выходного сигнала фильтра низкой частоты.

Емкость 1 6 запоминает это мгновенное значение сигнала с выхода фильтра низкой частоты и на ней поддерживается постоян ное напряжение, равное 0,50п»(ф»»г. 2э).

Импульс с выхода блока дифференцирования 13 (фиг. 2ж) откроет ключ 15 в момент времени, и амплитуда выходного сигнала ключа 15 соответствует значению синусоидального выходного сигнала фильтра низкой частоты 7 в этот момент времени

U(+ ) — 0 !Вю(ЗО )=0 сОЯЗО 0 ч где:U(t,>) - значение выходного сигнала фильтра низкой частоты в момент време3

Запоминающая ел»кость 17 запоминает это мгновенное значение сигнала с выхода фильтра низкой частоты и на ней будет постоянное напряжение, равное (Х

0 (фиг. 2и}.

Таким образом напряг»ение на запоминающих емкостях 16, 17, соответствующие коэффициентам а и в, имеют значения,. пропорциональные синусу и косинусу одного и того же угла, а обеспечение таких величии напряжений позволяет получить на выходе устройства сигнал неизменной амплитуды. Кроме того, в зависимости от числа управляющих импуль сов с выхода источника управляющего сигнала 8 фаза выходного сигнала устройства меняется линейно. Прирост изменения фазы постоянен и эависйт от коэффициента деления делителей 6 и 10.

Следовательно, предлагаемая схема обеспечивает минимальные амплитудные и фаэовые искажения синусоидального сигнала, сдвинутого по фазе.

Формула изобретения дискретный фаэоврашатель, содержащий источник управляющего си гнала, фаэовращатель, вход которого подключен к первому входу первого умножителя сигналов, выход фазовращателя подключен к первому входу второго умножитсля сигналов, Bb»» ходы первого и второго умножнтелс.й сигналов подкл»очень» ко входам сут матера, отличающийся тем, то,с целью получен»я дискретных флзо»ч»х сппи. 657591 гов синусоидального сигнала с наименьшими амплитудными и фазовыми искажениями, в него введены импульсный генератор, два элемента совпадения, два делителя частоты из Рьгриггеров каждый, 5 два блока дифференцирования, два ключа, две запоминающие емкости, фильтр низких частот, причем выход импульсного генератора подключен непосредственно ко входу первого делителя частоты и 1Ф через первый элемент совпадения - ко входу второго делителя частоты, второй вход первого элемента совпадения подключен к выходу источника управляющих сиг налов, выход первого делителя частоты через фильтр низких частот соединен со вторыми входами первого и второго ключа, выход второго делителя частоты подключен непосредственно к первому входу второго элемента совпадения и через первый блок дифференцирования к первому входу первого ключа, выход которого соединен с первой запоминающей емкостью и со вторым входом первого умножителя.сигналов, выход (1а-1)-го триггера второго целителя частоты через второй элемент совпадения и второй блок дифферен» цирования подключен к первому входу второго ключа, выход которого соединен со второй запоминающей емкостью и со вторым входом второго умножителя сиг налов.

Источники информации, принятйе во внимание при экспертизе

1, Патент США % 3475626, кл. Н 03 К 17/28, 1971.

657591

Составитель Л. Плетнева

Техред С. Мигай Корректор А. Гриценко

Редактор H. Каменская

Филиал Г!ПГ! "Патент", г. Ужгород, ул. Проектная, 4

Заказ 1 82 2/5 б Тираж 1059 . -Подписное

Ц!1ИИ1!И Государственного комитета СССР по делам изобретений и открытий

1l 3035, Москва, )!(-35, Раушская наб.„д. 4/5