Делитель частоты импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АРТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик оо657618 (61) дополнительное к авт. свид-ву (22) ЗаЯвлено 23.0976 (2l) 2405883/18-21 с присоединением заявки № (23) Приоритет

Опубликовано 150479. Бюллетень ¹ 14

Дата опубликования описания 1804.79 (51) М. Кл, H 03 К 23 04

Государственный комитет

СССР но делам изобретений и открытий (53) УДК821. 374. 3 (088. 8) (72) Авторы изобретения

Таганрогский радиотехнический институт им.В.Д.Калмыкова (71) Заявитель (54 ) ДЕЛИТЕЛЬ ЧАС ТОТЬ) ИМПУЛЬСОВ

Изобретение относится к импульсной технике.

Известен делитель частоты импульсов, состоящий из счетчика импульсов на триггерах, блока управления, схемы совпадений, цепи установки счетчика в исходное состояние, содержащей последовательно соединенные ячейки И и ИЛИ 111 .

Недостатком такого счетчика является недостаточная надежность.

Наиболее близким по технической . сущности к данному изобретению является делитель частоты, содержащий генератор импульсов, триггерный счетчик импульсов, входы установки триггеров которого соединены с выходами логических элементов И, один вход каждого из которых соединен с выходом первого дешифратора, другие входы которого соединены с одноименными входами второго дешифратора и с выходами триггеров счетчика, а соответствующие выходы дешифраторов соединены между собой и подключены ко входам блока управления, выходы которого подключены ко вторым входам логических элементов И (2) .

ЗО

Недостатком этого делителя является недостаточное быстродействие.

Целью изобретения является повышение быстродействия .

Поставленная цель достигается тем, что в делитель частоты, содержащий генератор импульсов, триггерный счетчик импульсов, входы установки триггеров которого соединены с выходами логических элементов И, один вход каждого из которых соединен с выходом первого дешифратора, одни входы которого соединены с одноименными входами второго дешифратора и с выходами триггеров счетчика, а соответствующие другие входы дешифраторов соединены между собой и подключены к первым выходам блока управления, другие выходы которого подключены ко вторым входам логических элементов И, введены счетный триггер и логический элемент ИЛИ, причем вход счетного: триггера соединен с выходом генератора импульсов, выход счетного. триггера соединен со входом триггерного счетчика импульсов и дополнительным входом второго дешифратора, а входы логического элемента ИЛИ соединены с выходамй дешифраторов.

657618 4

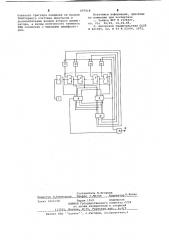

На чертеже показана структурная электрическая схема предлагаемого делителя.

Делитель содержит генератор импульсов l триггер 2, счетчик 3 из триггеров 4-7, дешифраторы 8 9, блок управления 10, логические элементы

И 11-14 логический элемент ИЛИ 15.

Выходной сигнал снимается с выхода

16.

Принцип работы описываемого делителя заключается в следующем.

Выходные импульсы генератора импульсов 1 поступают на вход счетчика 3 с последовательным переносом, образованного триггерами 4-7, которые работают в счетном режиме. В блоке управления 10 хранится информация о любом требуемом коэффициенте делителя частоты- код Я„ и о исходном состоянии делителя частоты Nо . Код и „ поступает на входы дешифраторов

8 и 9, а код И подается в виде разрешающих 1 (запрещающих С ) потенциалов на первые входы двухвходовых элементов И 11-14.

В процессе работы, при накоплении на счетчике 3 информации, равной коду Ny » во втором дешифраторе 9 происходит совпадение состояний триггеров счетчика 3, поступающих на первые входы дешифратора 9, с кодом Nygp поступающим с выходов блока управления 10 на другие входы дешифраторов 8,9, в результате чего на выходе дешифратора 9 формируется сигнал, соответствующий каждому Йу„ импульсу с выхода генератора импульсов 1. Сигнал с выхода дешифратора

9 поступает через логический элемен

ИЛИ 15 на выход 16 устройства.В процессе дальнейшей работы в счетчике продолжается накопление информации. B связи с тем, что триггер 2 непрерывно работает в режиме деления на два, на вход счетчика 3 поступает каждый второй импульс с выхода генератора импульсов 1, поэтому информация, соответствующая коду Nyz появляется на входах дешифратора 8, связанных с выходами. триггеров счетчика, при действии каждого 2 и „ импульса с выхода генератора импульсов 1. При этом, в дешифраторе 8 происходит совпадение состояний триггеров счетчика

3 с кодом Ку) р, поступающим на входы дешифраторов 8,9 с выходов блока управления 10 и на выходе дешифратора

8 Формируется сигнал, соответствующий каждому 2 Йщр импульсу с выхода генератора импульсов 1. Сигнал с выхода дешифратора 8 поступает через логический элемент ИЛИ 15 на выход

16 устройства и в виде разрешающего 1 потенциала на входы логических элементов И 11-14. В результате совпадения 1 и 1 (не совпаТаким образом, на выходе 16 делителя частоты выделяется каждый N импУльс и каждый 2 Nупр импУльс

УПР за время прохождения каждых 2 Ny„p импульсов с генератора импульсов 1, т.е. появляется каждыйМ римУпр пульс из выходной последовательности импульсов генератора импульсов 1, что соответствует требуемому коэфФициенту деления N делителя частоты. Но установка в исходное состоя20 ние триггеров счетчика 3 происходит при накоплении информации равной

2 йу„рв счетчике . Это соответствУет только четным коэффициентам деления, а на четных коэффициентах деления

25 установка исходного состояния в триггер не требуется., Следовательно триггер 2 работает в режиме непрерывного двоичного счета, за счет чего и достигается высокое быстродействие предлагаемого делителя частоты. Установка исходного состояния в триггерах счетчика 3 происходит в паузе

Формула изобретения

65 дения 0 и . 1 ) сигналов на первом и втором логических элементах

И 11-14 на их выходе появляется (не появляется) сигнал, производящий установку исходного состояния в триггерах счетчика 3, соответствующего коду Nz, который поступает на первые входы логических элементов И 11-14 с выходов блока управления 10. Далее работа делителя частоты повторяется. между импульсами с выхода триггер@

2, а так как триггер 2 работает в режиме двоичного непрерывного счета, то на входе счетчика действует сигнал с частотой в два раза меньшей чем частота с выхода генератора импульсов 1.

Делитель частоты импульсов, содержащий генератор импульсов, триггерный счетчик импульсов, входы у=тановки триггеров которого соединены с выходами логических элементов

И, первые входы которых соединены с выходом первого дешифратора, первая группа входов которого соединена с одноименными входами первой группы второго дешифратора и с выходами триггеров счетчика, а входы второй группы первого дешифратора соединены с соответствующими входами второй группы второго дешифратора и подключены к первой группе входов блока управления, выходы второй группы которого подключены ко вторым входам логических элементов И, о тл и ч а ю шийся тем что, с целью повышения быстродействия, в него введены счетный триггер и логический элемент ИЛИ, причем вход счетного триггера соединен с выходом генератора импульсов, выход

657018

Составитель B.Åãoðoâà

Редактор Н.Каменская Техред С.Мигай Корректор О Билак

Тираж 1059 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва, Ж-35 Раушская наб. д.4j5

Заказ 1823/58

Филиал ППП Патент, г.ужгород, ул.Проектная,4 счетного триггера соединен со входом триггерного счетчика импульсов и дополнительным входом второго дешиф— ратора, а входы логического элемента

ИЛИ соединены с выходами дешифраторов.

Источники информации, принятые во внимание при экспертизе

Заявка ФРГ Р 1928327, кл. 21а 36/22, 16.04.68.

2. ьвторское свидетельство СССР

:Р 401005, кл. Н 03 К 23/04, 1972.