Устройство для оценки достоверности приема дискретных сигналов

Иллюстрации

Показать всеРеферат

II ./ с

Ф

1 с

О П И С А Н. И- Е

ИЗОБРЕТЕНИЯ i-киче

Союз Советских

Соцкелкстнческих

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

{6l) дополнительное к авт. свил-ву

{22) Заявлено 071276 (21) 2426910/18-09 с присоединением заявки № (53) М. Кл.

Н 04 В 3/46

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано150479. Бвллетень М 14

Дата опубликования описания 150479 (+) УДМ621. 395. .664(088.8) (72) ABtophf

НЗОбрЕТЕНИЯ Ю.Я. Личидов, Н.Н. Ольшевский и В.Ф. Котлов (54 ) УСТРОЙСТВО ДЛЯ ОЦЕНКИ ДОСТОВЕРНОСТИ

ПРИЕМА ДИСКРЕТНЫХ СИГНАЛОВ

Изобретение относится к области электросвязи.

Известно устройство для оценки достоверности приема дискретных сигналов, содержащее блок автоматической регулировки усиления, основной регенератор, сигнальный вход которого объединен с сигнальными входами, 2п дополнительных регенераторов по числу дополнительных порогов регенерации, счетчик объема выборки, и элементов И с объединенными тактовыми входами, сумматор, индикатор и генератор тактовых импульсов (1).

Однако оценка достоверности в таком устройстве зависит от вида помех и помехозащищенности приемника. Цель изобретения — оценка достоверности приема дискретных сигналов независимо от вида помех и помехоэащищенности приемника.

Для этого в устройство для оценки достоверности приема дискретных сигналов, содержащее блок автоматической регулировки усиления, основной регенератор, сигнальный вход которого объединен с сигнальными входами 2 и дополнительных регенераторов по числу дополнительных порогов регенерации, счетчик объема выборки, и Ю элементов И с объединенйыми тактовыми входами, сумматор, индикатор и генератор тактовых импульсов, введены п пар блоков сравнения, и элементов

ИЛИ, и счетчиков ошибок, установочные входы которых объединены с первым входом триггера, выход которого через элемент совпадения подключен к входу формирователя стробирующих импульсов, выход каждого из п счетчиков ошибок подключен к соответствующему входу введенного мультиплексора, выходы которого через обратный функциональный преобразователь подключены к соответствующим входам введенного демультиплексора, каждый из выходов которого через один из п блоков памяти подключен к входу соответствующего из введенных и умножителей, а также функциональный преобразователь и распределитель импульсов, вход пуска которого соединен с вторым входом триггера, а соответствующие выходы распределителя импульсов подключены к вторым входам блоков памяти и к объединенным управляющим входам мультиплексора и демультиплексора, при этом первые входы п блоков сравнения объединены, а выходы первого и второго блоков сравнения

657629 каждой из п пар подключены соответственно к первому и второму Входам соо-.ветствующего элемента. HJIt4, при этом выход блока автома- è÷åñêîé регулировки усиления подключен к сиг.нальному входу основного регенератора, тактовый вход которого объединен 5 с тактовыми входами дополнительных регенераторов: и соединен с выходом генератора тактовых импульсов и вторым входом элемента совпадения, выход которого подключен к сигнальному вхо-f0 ду счетчика объема выборки, установочный выход и вход которого соединены соответственно с первым и вторым входами триггера, выход основного регенератора подключен к объединенным первым входам и блоков сравнения, второй вход каждого из которых соединен с выходом одного из дополнительных регенераторов, выход каждого из и элемен-.îâ ИЛИ подключен к сигнальному входу соответствующего

20 счетчика ошибок через один из элементов И, тактовые входы которых подключены к выходу формирователя стробирующих импульсов, выход каждого блока умножения подключен к соответству- 25 ющему входу сумматора, выходы которого через функциональный преобразователь подключены к соответствующим входам индикатора, управляющий вход которого соединен с управляющим входом сумма- M тора и с соответствующим выходом распределителя импульсов.

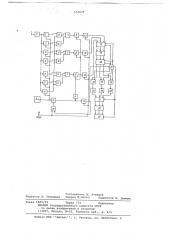

На чертеже представлена структурная электрическая схема предложенного устройства. 35

Устройство для оценки достоверности приема дискретных сигналов содержит вхоц 1 блока 2 автоматической регулировки усиления, являющийся входом устройства, 2 и дополнительных ре- 40 генераторов 3, основной регенератор

4, генератор 5 тактовых импульсов, и пар блоков 6 сравнения, и элеМентов

ИЛИ 7, п элементов И .8, формирователь

9 стробирующих импульсов, и счетчиков 10 ошибок, счетчик ll объема вы45 борки, триггер 12, клемму 13 Пуск, элемент 14 совпадения, мультиплексор

15, распределитель 16 импульсов, обратный функциональный преобразователь

17, демультиплексор 18, и блоков 19 50 памяти, и умножителей 20, сумматор

21, функциональный преобразователь

22 и индикатор 23.

Устройство работает следующим образом. 55

Демодулированный сигнал исследуемого приемника дискретных сигналов поступает на вход 1 блока 2 автоматической регулировки усиления, который стандартизует уровень сигнала..

Стандартизованный сигнал регенерируется дополнительными регенераторами

3 и основньи регенератором 4. Затем выходная по"ледовательность основного регенератора 4 сравнивается по модулю 2 в блоках 6 сравнения с выходными последовательностями дополнительных регенераторов 3. При несовпадении знаков в какой-либо из пар сравниваемых последовательностей на выходе соответствующего блока сравнения 6 появляется единичный сигнал ошибки.

Выходные сигналы блоков 6 сравнения попарно объединяются элементами

ИЛИ 7 и поступают на первые входы элементов И 8 соответственно. До начала цикла счета числа ошибок все элементы И 8 закрыты, так как на их вторых входах отсутствуют стробирующие импульсы. Цикл счета начинается подачей сигнала Пуск на клемму

13, который устанавливает счетчики

10 ошибок и счетчик 11 объема выборки в нулевое состояние, а триггер 12 в единичное состояние, открывая тем самым элемент 14 совпадения, который начинает пропускать сигнал тактовой частоты с генератора 5 тактовых импульсов на вход счетчика 11 объема выборки, подсчитывающего число тактов, и на вход формирователя 9 стробирующих импульсов. Стробирующие импульсы разрешают прохождение сигналов ошибок через элементы И 8 на входы счетчиков

10 ошибок.

Цикл счета числа ошибок продолжается до тех пор, пока счетчик 11 объема выборки не зафиксирует заданное число тактов. На его выходе при этом появится сигнал, который установит триггер 12 в нулевое состояние.

Злемент 14 совпадения закроется и прекратится поступление тактового сигнала на счетчик 11 объема выборки и стробирующих импульсов на элементы

И 8, что в свою очередь запретит прохождение сигналов ошибок на входы счетчиков 10 ошибок. Показания счетчиков 10 ошибок, отнесенные к объему выборки, при достаточной величине смещения будут представлять собой частоту ошибок при ухудшенном по сравнению с рабочим соотношении сигнал/шум. Одновременно со сбросом триггера 12 в нулевое состояние сигнал с выхода счетчика 11 объема выборки производит запуск распределителя 16 импульсов, который формирует серию управляющих сигналов.

По этим сигналам зафиксированные к момен у окончания просчета показания счетчиков 10 ошибок, соответствующие частоте ошибок при определенных смещениях порога дискриминации, считываются поочередно через мультиплексор

15 на входы обратного функционального преобразователя 17. Обратный функциональный преобразователь 17 моделирует некоторую заданную сложную функцию, например, интеграл вероятностей, формируя на своем выходе сигнал, величина которого равна аргументу этой функции в точке, где значение функции равно величине, заданной на вход обратного функционального преобразоватеC57С29 ля 17. Полученные на его выходе сигналы, равные значениям аргументов, через демультиплексор 18, управляемый также распределителем импульсоа 16, считываются поочередно на блоки 19 памяти. Зафиксированные а блоках 19 памяти величины умножаются на некото- 5 рые постоянные коэффициенты с помощью умножителей 20 и суммируются сумматором 21, который таким образом формирует значение аргумента аппроксимирующей функции в рабочей точке р (при нулевом смещении порога дискриминации). Это значение аргумента с выхода сумматора 21 поступает на вход функционального преобразователя 22, который формирует значение функции, соответствующее заданному аргументу.

Это значение функции представляет собой искомую частоту ошибок в рабочей точке, =.е. является оценкой достоверности приема дискретного сигнала. Сформированный на выходе функ20 ционального преобразователя 22 сигнал поступает на индикатор 23, который осуществляет вывод его для визуального считывания либо для печати.

Формула изобретения

Устройство для оценки достоверности приема дискретных сигналов, со- 30 держащее блок автоматической регулировки усиления, основной регенератор, сигнальный вход которого объединен с сигнальными входами 2п дополнительных регенераторов по числу допол; нительных порогов регенерации, счетчик объема выборки, и элементов И с объединенными тактовыми входами, сумматор, индикатор и генератор тактовых импульсов, о т л и ч а ю 40 щ е е с я тем, что, с целью оценки достоверности независимо от вида помех и помехозащищенности приемника, введены и пар блоков сравнения, и элементоа ИЛИ, и счетчиков ошибок, установочные входы которых объединены с первым входом триггера, выход которого через элемент совпадения подключен к входу формирователя стробирующих импульсов, выход каж. дого из и счетчиков ошибок подклю- 50 чен к соответствующему входу введенного мультиплексора, выходы которого через обратный функциональный преобразователь подключены к соответствующим входам введенного демультиплексора, каждый из и выходов которого через оцин из и блоков памяти подключен к входу соотгетствующего из введенных и умножителей, а также функциональный преобразователь и распределитель импульсов, вход пуска которого соединен с вторым входом триггера, а соответствующие выходы распределителя импульсов подключены к вторым входам блоков памяти и к объединенным управляющим входам мультиплексора и демультиплексора, при этом первые входы П блоков сравнения объединены, а выходы первого и второго блоков сравнения каждой из И пар подключены соответственно к первому и в-aport, входам соответствующе-. го элемента ИЛИ, при этом выход блока автоматической регулировки усиления подключен к сигнальному входу основного регенератора, тактовый вход которого объединен с тактовыми входамй дополнительных регенераторов и соецинен с выходом генератора тактовых импульсов и вторым входом элемента совпадения, выход которого подключен к сигнальному входу счетчика объема выборки, установочный выход и вход которого соединены соответственно с первым и вторым входами триггера, выход основного регенератора подключен к объединенным первым входам блоков сравнения, второй вход каждого из которых соединен с выходом одного из дополнительных регенераторов, выход каждого из 11 элементов ИЛИ подключен к сигнальному входу соответствующего счетчика ошибок через один из элементов И, тактовые входы которых подключены к выходу формирователя стробирующих импульсов, выход кажцого блокч умножения подключен к соответствующему входу сумматора, выходы которого через функциональный преобразователь подключены к соответствующим входам индикатора, управляющий вход которого соединен с управляющим аходом сумматора и с соответствующим выходом распределителя импульсов.

Источники информации, принятые ао внимание при экспертизе, 1. Шварцман В.О. Каналы передачи данных. И., Связь, 1970, с. 272273.

657629

Составитель B. Лякишев

Редактор Л. Гельфман Техред Я.Петко Корректор М. Демчик

Заказ 1825/59 Тираж 774 Подписное

ЦНИИПИ Государственного .комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. ужгород, ул. Проектная, 4