Устройство для передачи и приема цифровых сигналов с положительным стаффингом

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

"657634

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сви 1-ву (22) Заявлено 3012.75 (21) 2306047/18-09

FI 04 Х 3/18 с присоединением заявки,яп1 (23) Приоритет

Государственный комитет

СССР но делам изобретении н открытий (53) УД Кб 2 1 . 3 7 6 ...56:621.391.31 (088.8) Опубликовано 150479 Бюллетень pk 14

Дата опубликования описания1504.79 (72) Авторы изобретения

Л.Д. Колыхалов, Л. Н. Оганян, Л. Н. Смирнов и Б.Н. Тихонов (71) заявитель (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ЦИФРОВЫХ

СИГНАЛОВ С ПОЛОЖИТЕЛЬНЫМ СТАФФИНГОМ

Изобретение относится к технике электросвязи и может быть использовано в многоканальных системах электросвязи с временным делением каналов.

Известно устройство для передачи и приема цифровых сигналов с положительным стаффингом в многоканальных системах связи с временным разделением каналов, содержащее на передающей стороне блок памяти, вход Считывание которого соединен с выходом элемента Запрет, который подключен к одному входу фазового детектора, другой вход которого соединен с входом Запись 15 блока памяти, выход последнего подключен к первым входам ключа и блока формирования сигналов стаффинга,, выход которого подключен к второму входу ключа, выход которого подключен к первому входу элемента Запрет, к второму входу которого подключен выход блока генераторов, второй выход которого подключен к соответствующему входу блока объединения цифровых сиг" к5 налов и сигналов стаффинга, другой соответствующий вход которого соединен с выходом блока формирования сигналов стаффинга, второй вход кото. рого соединен с выходом блока генера- @ торов, на приемной стороне — последовательно соединенные блок генераторов, приемник сигналов стаффинга, элемент Запрет, другой вход которого соединен с другим выходом блока генераторов, вход которого соединен с одним из выходов блока разъединения цифровых сигналов и сигналов стаффинга, другой выход которого подключен к другому входу приемника сигналов стаффинга, выход элемента Запрет подключен к запрещающему входу блока памяти., информационный вход которого соединен с третьим выходом блока разъединения цифровых сигналов и сигналов стаффинга (11.

Однако это устройство характеризуется недостаточной пропускной способностью каналов.

Целью изобретения является повышение пропускной способности каналов путем повышения скорости передачи цифровых сигналов с положительным стаффингом.

Для этого в устройство для передачи и приема цифровых сигналов с положительным стаффингом в многоканальных системах связи с временным разделением каналов, содержащее на передающей стороне блок памяти, вход

65763 Считывание которого соединен с выходсм элемента Запрет, который подключен к одному входу фазового детектора, другой вход которого соединен с вх,одом Запись блока памяти, выхоц последнего подключен к первым входам ключа и блока формирования сигна- 5 лов стаффинга, выход которого подключен к второму входу ключа, выход которого подключен к первому входу элемента Запре т, к второму входу которого поцключен выход блока гене- 10 раторов, второй выход которого подключен к соответствующему входу блока объединения цифровых сигналов и сигналов стаффинга, другой соответствующий вход которого соединен с вы- 5 ходом блока формирования сигналов стаффинга, второй вход которого соединен с выходом блока генераторов, на приемной стороне — последовательно соединенные блок генераторов, приемник0 сигналов стаффинга, элемент Запрет, другой вход которого соединен с другим выходом блока генераторов, вход которого соединен с одним из выходов блока разъединения цифровых сигналов и сигналов стаффинга, другой выход которого подключен к другому входу приемника сигналов стаффинга, выход элемента Запрет подключен к запрещающему входу блока памяти, информационный вход которого соединен с третьим выходом блока разъединения цифровых сигналов и сигналов стаффинга, введены на передающей стороне элементы И и ИЛИ, на приемной стороне — элемент И, инвертор и 35 триггер, при этом на передающей стороне выход ключа поцключен к одному из входов элемента И, выход которого подключен к одному из входов элемента ИЛИ, другой вход которого соединен 40 с выходом блока памяти, а выход элемента ИЛИ подключен к соответствующему входу блока объединения цифровых сигналов и сигналов стаффинга, на приемной стороне информационный вход блока памяти объединен с одним из входов элемента И, другой вход которого соединен с выходом элемента Запрет, выход элемента И подключен к одному из входов триггера и к входу инвертора, выход, которого подключен к другому входу триггера.

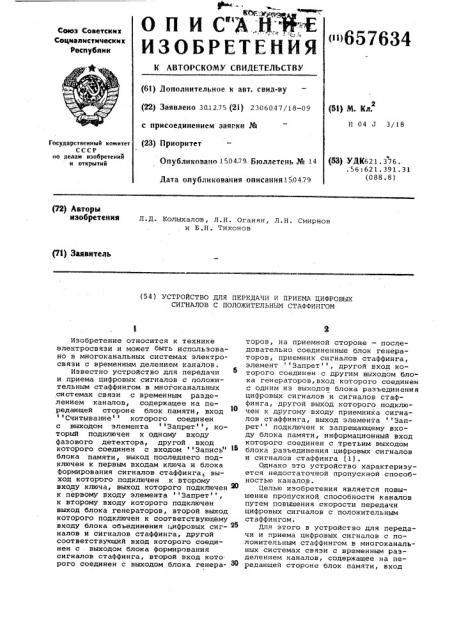

На чертеже приведена структурная электрическая схема предложенного устройства. устройство д я переда и и рие. а 55 цифровых сигналов с положительным стаффингом в многоканальных системах связи с временным разделением каналов содержит на передающей стороне блок памяти i, элемент Запрет 2, фаза- 60 вый детектор 3, ключ 4, блок 5 для формирования сигналов стаффинга, блок

6 генераторов, блок 7, предназначен ный для объединения цифровых сигналов и сигналов стаффинга, на приемной стороне — блок 8 генераторов, приемник

4 4

9 сигналов стаффинга, элемент Запрет 10, блок разъединения 11 цифровых сигналов и сигналов стаффинга, блок памяти 12, введены на передаю-. щей стороне — элемент И 13, элемент

ИЛИ 14, на приемной стороне — элемент

И 15, инвертор 16, триггер 17.

Устройство работает следующим образом.

Запись информации в блоке памяти 1 осуществляется с тактовой частотой объединяемого цифрового потока, а считывание — с частотой, превышающей частоту записи и определяемой блоком

6 генераторов. Как только разность фаз между сигналами записи и считывания достигнет порогового значения фазового детектора 3, на один вход ключа 4 с выхода фазового детектора 3 подается сигнал. На второй вход ключа

4 поступает сигнал с выхода блока

5 в моменты, определенные структурой объединенного цикла передачи, после чего с выхода ключа 4 на элемент Запрет 2 поступает сигнал запрета, вследствие чего будет пропущен один такт считывания из блока памяти

1, так как в объединенном цикле передачи появится балластная вставка.

Для обнаружения и устранения балластных вставок при разъединении цифровых потоков из блока 5 по каналу управления стаффингом в приемник 9 передаются сигналы о наличии балластных вставок. В связи с тем, что в устройстве на тактовые позиции введены символы дополнительной информации,. то они поступают на вход элемента

И 13. На второй вход элемента И 13 будет подаваться стробирующая импульсная последовательность с выхода ключа 4. Таким образом с помощью элемента И 13 осуществляется ввод дополнительной информации способом наложения . Дополнительная дискретная информация с выхода элемента И 13 через элемент ИЛИ 14 будет введена на тактовые позиции балластных вставок и через блок объединения 7 будет передана по линейному тракту в блок разъединения 11 приемной части.

Из блока разъединения 11 цифровой поток поступает в блок памяти 12. В моменты прихода балластных вставок с выхода .приемника 9 на элемент Запрет 10 поступает сигнал, запрещающий импульс записи от блока 8 на блок памяти 1?. Одновременно с выхода приемника 9 на .элемент И 15 будет передан сигнал, по которому символ дополнительной информации через элемент

И 15 будет поступать на один из раздельных входов триггера 17. На второй разцельный вход триггера 17 подается последовательность инверсных символов от инвертора 16. На выходе триггера 17 формируется огибающая па- чек импульсов, соответствующая символам дополнительной дискретной информации на входе элемента И 13.

657634

Передающая

mepoerz

-1

Составитель Л. Каграманоэа

Редактор А. Зиньковский, Тсхред M.Петко Корректор М. Демчик

Заказ 1825/59 Тираж 774

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филкал ППП Патент, r. Ужгород, ул. Проектная, 4

Таким образом в предложенном устройстве на балластных тактовых позициях передается дополнительная дискретная информация, что повыщает эффективность использования цифрового линейного тракта.

Формула изобретения

Устройство для передачи и приема цифровых сигналов с положительным стаффингом в многоканальных .системах связи с временным разделением каналов, содержащее на передающей стороне блок памяти, вход Считывание которого соединен с выходом элемента Запрет, который подключен к одному входу фазового детектора, другой вход которого соединен с входом Запись блока памяти, выход последнего подключен к первым входам ключа и блока формирования сигналов стаффинга, выход которого подключен к второму входу ключа, вы- 20 ход которого подключен к первому входу элемента Запрет, к второму входу которого подключен выход блока генераторов, второй выход которого подключен к соответствующему входу 25 блока объединения цифровых сигналоэ и сигналов стаффинга, другой соответствующий вход которого соединен с выходом блока формирования сигналов стаффинга, второй вход которого соеди-g0 нен с выходом блока генераторов, на приемной стороне — последовательно соединенные блок генераторов, приемник сигналов стаффинга, элемент Запрет, другой вход которого соединен с другим выходом блока генераторов, вход которого соединен с одним из выходов блока разъединения цифровых сигналоэ и сигналов стаффинга, другой выход которого подключен к другому входу приемника сигналов стаффинга, выход элемента Запрет подключен к запрещающему входу блока памяти, информационный вход которого соединен с третьим выходом блока разъединения цифровых сигналов и сигналов стаффинга, о т л и ч а ю щ е е с я тем, что, с целью повышения пропускной способности каналов путем повышения скорости передачи цифровых сигналов с положительным стаффингом, введены на передающей стороне элементы И и ИЛИ, иа приемной стороне — элемент И, инвертор и триггер, при этом на передающей стороне выход ключа подключен к одному из эходоэ элемента И, выход которого подключен к одному из входов элемента ИЛИ, другой вход которого соединен с выходом блока памяти, а выход элемента ИЛИ подключен к соответствующему входу блока объединения цифровых сигналов и сигналов стаффинга, на приемной стороне информационный вход блока памяти объединен с одним из входов элемента И, другой вход которого соединен с выходом элемента Запрет, выход элемента И подключен к одному из входов триггера и к входу инвертора, выход которого подключен к другому входу триггера.

Источники .информации, принятые эо внимание при экспертизе

1. Патент СШй 9 3136861, кл. 179-15, 1964.

7pverrhag

r ynggg