Устройство фазирования псевдослучайных последовательностей

Иллюстрации

Показать всеРеферат

О П И С А Н ИИЗОБРЕТЕНИ

76-37

Союз Советских

Социапистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 29л074 (21) 2071478/18-0 с присоединением заявки РЙ (23) Приоритет

Опубликовано 150479. Бюллетень K

Дата опубликования описания 1504

Ь 7/02

Государственный комитет

СССР по делам изобретений и открытий

621.374. .4(088.8) (72) Автори

ИВОбрЕтЕНИя Ф.Г. Гордон, N.ß. Вертлиб и В.А. Прощенко (71) Заявитель (54) УСТРОЙСТВО ФАЗИРОВАНИЯ ПСЕВДОСЛУЧАЙНЫХ

ПОСЛЕДОВАТЕЛЬНОСТЕЙ

Изобретение относится к передаче данных и может использоваться,,например, для когерентной работы датчиков, образованных путем сложения по модулю два ряда рекуррентных последовательностей (кодов).

Известно устройство фазирования псевдослучайных последовательностей (ПСП), содержащее в каждом из П -1 каналов обработки ПСП последовательно соединенные первый сумматор по модулю два, регистр сдвига с логической обратной связью (ЛОС) и второй сумматор по модулю два, другой вход которого соединен с соответствующим входом первого сумматора по модулю два, а в и канале — регистр сдвига с ЛОС и второй сумматор по модулю два, а также блок управления.

Однако известное устройство обеспечивает фазирование только п-сложенных по модулю два рекуррентных последовательностей.

Цель изобретения — удержание пра- вильной фазы при наличии ошибок за счет обработки различного числа ПСП.

Для этого в каждом из и -1 каналов между выходом первого сумматора по модулю два и входом регистра сдвига с логической обратной связью,а в и-ом канале на входе регистра сдвига с логической обратной связью включен ключ, к управляющим входам которого подключены соответственно выход регистра сдвига с логической обратной связью непосредственно, а выход второго сумматора по модулю два — через блок управления, причем выходы ключа и блока управления каждого канала обработки ПСП подключены соответственно к вторым входам первого сумматора по модулю два и блока управления предыдущего канала обработки ПСП.

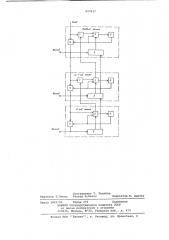

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство фазирования ПСП содержит в каждом из П -1 каналов обработки ПСП последовательно соединенные первый сумматор 1 по модулю два, ключ

2, регистр сдвига 3 с ЛОС и второй сумматор 4 по модулю два, второи вход которого соединен с одним из входов первого сумматора 1, а в

П-ом канале .последовательно соединенные ключ 2, регистр сдвига 3 с

ЛОС и второй сумматор 4, второй вход которого соединен с одним из входов ключа .2, а также в каждом из П каналов-блок управления 5, причем к

657637 управляющим входам ключа 2 подключены соответственно выход регистра сдвига

3 непосредственно, а выход второго сумматора 4 — через блок управления

5. Кроме того, другие выходы ключа 2 и блока управления 5 каждого канала, кроме первого, подключены соо вет- 5 ственно к вторым входам первого сумматора 1 и блока управления 5 предыдущего канала. Выход второго сумматора 4 кажцого канала (начиная с первого) соединен с вторым входом 10 второго сумматора 4 последующего канала обработки ПСП.

Устройство работает следующим.образом.

При включении устройства блоки управления 5 во всех П каналах устанавливаются в исходное состояние, при этом ПСП с входа устройства поступает через соответствующие сумматор 1 и ключ 2 в регистр сдвига 3.

При поступлении на вход устройства последовательности, образованной сложением по модулю два (1 рекуррентных последовательностей с помощью сумматоров 4 и регистров сдвига

3 осуществляется проверка поступающей последовательности на соответствие закону формирования ее на передаче. В случае отсутствия ошибок на выходе n -ro канала отсутствуют сигналы Ошибки при этом блок

5 VI --го канала запрещает поступление последовательности иэ сумматора 4 и-1-го канала на вход регистра сдвига

3 ll-го канала, разрешает прохождение последовательности с выхода регистра 35 сдвига 3 и-го канала на его вход через сумматор 1 П- 1-ro канала и подготавливает блок управления 5 И -1-го канала:

В сумматоре 1 П-1-го канала осуще- 40 ствляется вычитание по модулю два из входной последовательности, поступающей с выхода сумматора 4 П-2-го канала рекуррентного кода, сформированного в регистре сдвига 3 8 --го канала.45

В случае отсутствия ошибок на выходе сумматора 4 П-го канала блок управления 5 того же канала выдает сигнал, вкчючающий блок управления 5

И -1-го канала, который запрещает поступление последовательности из сумматора 4 П -2-го канала на вход регистра сдвига 3 и -1-го канала, разрешает прохождение последовательности с выхода регистра сдвига 3 )l — 1-го канала на его вход через сумматор 1

И-2-ro канала и подготавливает блок управления 5 п -2-го канала. Аналогично фазируются остальные регистры сдвига 3..

В случае поступления на вход устройства последовательности, образованной сложением по модулю два п рекуррентных кодов, где tn (rl устройство начинает фаэироваться с регистра сдвига 3 я-го канала.

Формула изобретения

Устройство фаэирования псевдослучайных последовательностей, содержащее в каждом из П -1 каналов обработки псевдослучайных последовательностей последовательно соединенные первый сумматор по модулю два, регистр сдвига с логической обратной связью и второй сумматор по модулю два, другой вход которого соединен с соответствующим входом первого сумматора по модулю два, а в П канале — регистр сдвига с логической обратной связью и второй сумматор по модулю два, .а также блок управления, о т л и ч аю щ е е с я тем, что, с целью удержания правильной фазы при наличии ошибок за счет обработки различного числа псевдослучайных последовательностей, в каждом из И -1 каналов между выходом первого сумматора по модулю два и входом регистра сдвига с логической обратной связью, а в

t1 канале на входе регистра сдвига с логической обратной связью включен ключ, к управляющим входам которого подключены соответственно выход регистра сдвига с логической обратной связью непосредственно, а выход второго сумматора по модулю два — через блок управления, причем выходы ключа и блока управления каждого канала обработки псевдослучайных последовательностей подключены соответственно к вторым входам первого сумматора по модулю два и блока управления предыдущего канала обработки псевдослучайных последовательностей.

657637

Рыл и

Составитель Г. Теплова

Редактор Т.Янова Техред N.Ïåòêo Корректор М. Демчик

Заказ 1825/59 Тираж 774 Подписное

ЦИИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, E-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4