Устройство определения скорости телеграфирования и длительности стартстопного цикла

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

K АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Cases Советских

СОцнзнистич60сих

Республик 657642 (61) Дополнительное к авт. свид-ву—

Р2) ЗаЯвлено 110577 (21) 2485553/18-09 с присоединением заявки М (23) Приоритет—

Опубликовано 1504.79. Бюллетень №14

Дата опубликования описания 15.04.79 (Я) M. кл.

Н 04 L 7/04

Н 04 L 11/08

Государственный комитет

СССР ио делам изобретении и открытий (Щ УМ 4 621. 394. .6 (088.8) (72) Автор изобретения А И Коодобовский (54 ) УСТРОИСТВО ОПРЕДЕЛЕНИЯ СКОРОСТИ

ТЕЛЕГРАФИРОВАНИЯ И ДЛЙТЕЛЬНОСТИ

СТАРТСТОПНОГО ЦИКЛА

Изобретение относится к радиотехнике.

Известно устройство определения скорости телеграфирования и длительности стартстопного цикла, содержащее посл едов ат ел ьн о с оеди н ен н ые в ходной согласующий блок, старт ст опный триггер, элемент И, другой вход которого соединен с задающим генератором, и распределитель, другой вход послед- ® него через последовательно соединенные формирователь и первую дифференциальную цепь соединен с выходом стартстопного триггера, причем выходы распределителя через блок триггеров соединены с соответствующими входами блока элементов И, один из входов которого через вторую .дифференциальную цепь соединен с другим выходом входного согласующего блока (1) М

Однако известное устройство обладает недостаточным быстродействием.

Цель изобретения — повышение быстродействи я.

Для этого в устройство определения 5 скорости телеграфирования и длительности стартстопнoro цикла, содержащее последовательно соединенные входной согласующий блок,.стартстопный тригГер, элемент И, другой вход которого соединен с задающим генератором, и распределитель, другой вход последнего через последовательно соединенные формирователь и первуЮ дифференциальную цепь соединен с выходом стартстопного триггера, причем выходы распределителя через блок триггеров соединены с соответствующими входами блока элементов И, один из входов которого через вторую дифференциальную цепь соединен с другим выходом входного согласующего блока, введены блок триггеров долговременной памяти, триггер, дешифратор и индикаторы, причем выходы блока элементов

И через блок триггеров долговременной памяти соединены с входами дешифратора и триггера, выход которого соединен с другими входами стартстопного триггера и фсрм рователя, выходы дешифратора соединены с индикаторами, причем входной сигнал подан на триггер и соответствующие входы блока триггеров долговременной памяти.

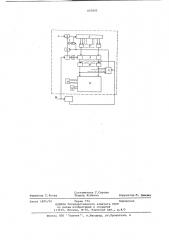

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство содержит входной согласующий блок 1. стартстопный триггер 2, элемент И 3, задающий гене657642

55 ратор 4, распределитель 5, формирователь 6, дифференци;льную цепь 7, блок триггеров 8, блок элементов И 9, блок триггеров 10 долговременной памяти, триггер 11, дешифратор 12, индикаторы 13 и дифференциальную цепь 14.

Устройство работает следующим образом.

При получении вызова, т.е. запуска автостопа, подается противоположная полярность (или земля, например).

В этом случае триггер 11 переводится )0 в рабочее положение, при котором со стартстопного триггера 2 снимается блокировка и он готов к работе..Сни— мается также блокировка с блока триггеров 10 долговременной памяти, при этом они находятся в рабочем положении.

При поступлении с противоположной станции (телеграфного аппарата) определяющих комбинаций входной согласую20 щий блок 1 повторяет эти сигналы, которые поступают на стартстопный триггер 2 и дифференциальную цепь 14, При поступлении пусковой полярности (бестоковая посылка) ст артстопный триггер

2 переводится в рабочее положение, при этом открывается элемент И 3, импульсы с задающего генератора 4 поступают на распределитель 5. Одновременно со срабатыванием стартстопного триггера 2, в результате его перехода30 в рабочее положение, формирователь 6 под действием импульса с первой дифференциальной цепи 7 вырабатывает сигнал, записывающий единицу в начале распределителя 5 и списывающий ее в 35 других местах распределителя 5. Записанная в начале распределителя 5 единица под действием тактовых импульсов перемещается вдоль него. При прохождении единицы по распределителю 5 40 в соответствующих его точках на блок триггеров 8 выдаются импульсы начало и конец пьедестала. Поступая на разные входы блока триггеров

8, эти импульсы определяют начало и конец подачи потенциала с блока триггеров 8 на блок элементов И 9. Триггеров в блоке триггеров 8 и элементов И в блоке элементов И 9, триггеров в блоке триггеров 10 должно быть столько, сколько может быть в сети различных контактных делений и скоростей телеграфирования.

В момент прихода с линии конца -"òîповой посылки дифференциальная цепь

14 вырабатывает короткий импульс, поступающий на блок элементов И 9 и проходит только через тот элемент, который в данное время является проводящим, т.е, тот, на который подан потенциал с блока триггеров 8. Пройдя через блок элементов И 9, этот импульс поступает в блок триггеров 10 долговремен ной памяти, пере брасывающи и с я в рабочее положение, закрывает стартстопный триггер 2, распределитель 5 останавливается, устройство заканчивает свою работу, так как длительность цикла и скорость телеграфирования определена срабатыванием блока триггеров 10.

Для индикации выделенных признаков потенциалы с блока триггеров 10 долговременной памяти поступают на дешифратор 12, откуда поступают на блоки индикации 13. формул а и з обр ет ени я

Устройст во определ ени я скорости телеграфирования и длительности

0 стартстопного цикла, содержащее последовательно соединенные входной согл асующий блок, стартстопный три rrep, элемент И, другой вход которого соединен с задающим генератором, и распределитель, другой вход последнего через последовательно соединенные формирователь и первую дифференци ал ьную цепь соедин ен с выходом стартстопного триггера, причем выходы распределителя через блок триггеров соединены с соответствующими входами блока элементов И, один из входов которого через вторую дифференциальную цепь соединен с другим выходом входного согласующего блока, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, введены блок триггеров долговременной памяти, триггер, дешифратор и индикаторы, причем выходы блока элементов И через блок триггеров долговременной памяти соединены с входами дешифратора и триггера, выход которого соединен с другими. входами стартстопного триггера и формирователя, выходы дешифратора соединены с индикаторами, причем входной си нал подан на триггер и соответствующие входы блока триггеров долговременной памяти.

Источники информации, принятые во внимание при,экспертизе

1. Авторское свидетельство СССР

9 340108, кл. Н 04 L 7/02, 1972.

657642

Г!

Составит ель Г. Серова

Техред М.Петко

Корректор M. Демчик

Редактор Т.Янова

Тираж 774 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретейий и открытий

1130 35, Москва, Ж-35, Раушская наб., д.4/5

Заказ 1825/59

Филиал ППП Патент, г.Ужгород, ул.Проектная, 4