Стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

-э.;i-.ичео

8539

Союэ Советских

Социалистических

Реслублин

ОП ИСАНИ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-вх— (22) Заявлено 29.03.77 (21) 2467320/24-07 с присоединением заявки U (23) Приоритет—

5 F 1, 56

Государственный комитет

СССР ов делам изобретений н открытий

Опубликовано 25.04.79. Бюллетень ¹ 15

Дата опубликования описания 05.05.79. (53) ДК 621.3! 6. .722.1 (088,8) (72) Автор1» изобретения

Н. Н. Прокопенко и В..Ч. Редько

Шахтинский технологический институт (7i) Заявитель (54) СТАБИЛИЗАТОР Г1ОСТОЯННОГО НАПРЯЖЕ=.Н11Я

Изобретение относится к области электротехники и может быть использовано в цепях питания различной радиотехнической аппаратуры.

Известен стабилизатор постоянного напряжения, содержащий регулирующий элемент и цепь обратной связи, состоящую из делителя выходного напряжения, усилителя рассогласования и источника опорного напряжения (1) .

Наиболее близким к предложенному по технической сущности является стабилизатор, содержащий регулирующий элемент, включенный в одну из силовых шин, токостабилизируюший элемент, включенный в общую эмиттерную цепь параллельно-балансного каскада, первый вход которого подключен к источнику опорного напряжения, второй вход — к выходу первого делителя, подключенного к выходным выводам, а выход параллельно-балансного каскада подключен к конденсатору и ко входу регулирующего элемента 12) .

Недостатком таких стабилизаторов является невысокое быстродействие при больших скачках тока в нагрузке или при переходе с одного уровня стабилизируемого напряжения на дргл ой. Здесь и д;1, 1ее llo,i параметрам и быстродействия о< деxi пои имать время установления переходного пр<цесса и скорость нарастания выходного паг1ряжения.

Целью изобретения является повыиц иис быстродействия стабилизaTop;f напряжения.

3То достигается тем, что в предлож< нвы Й cTkf0II, I II3

1о лители напряжения, каждый из которых выпо,-:нен на резисторе и диоде, причем второй делитель включен параллельно источнику опорного напряжения, третий делитель вклктчен между общей шиной и выходом первого делителя, а выходы третьего !i второго

15 делителеи соединены через BcTpc÷ío вкл1оченные допол11ительно введенные диоды, общая точка f

658539

so

И з

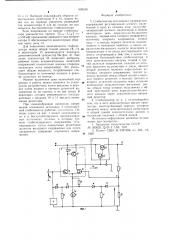

Схема предложенного стабилизатора приведена на фиг. I; на фиг. 2 — то же, вариант; на фиг. 3 показана зависимость тока нагрузки усилителя сигнала рассогласования (параллельно-балансного каскада) от входного напряжения.

Стабилизатор напряжения содержит регулирующий элемент 1 и токостабилизирующий элемент 2 в общей эмиттерной цепи параллельно-балансного каскада 3. Каскад

3 играет роль усилителя сигнала рассогласования. Источник опорного напряжения 4 связан с первым входом 5 каскада 3, второй вход 6 которого подключен к первому делителю напряжения. Резистор 7 образует верхнее плечо данного делителя. Выход каскада 3 соединен с корректирующим конденсатором 8 и входом регулирующего элемента l. К.источнику Ц опорного напряжения подключен второй делитель напряжения, выполненный на резисторе 9 и диоде 10. К выходу 6 первого делителя напряжения подключен третий делитель, содержащий резистор 11 и диод 12. Выходы второго и третьего делителей соединены через встречно включенные диоды 13 и 14. Общая точка диодов 13 и 14 подключена к токостабилизирующему элементу 2 через дополнительный резистор 15. К выводу 16 присоединяется источник напряжения постоянного тока, вывод 17 является выходом стабилизатора.

Параллельно-балансный каскад 3 выполнен на транзисторах 18, 19, 20 и диоде 21. Регулирующий элемент 1 содержит транзисторы 22 и 23.

Стабилизатор, показанный на фиг. 2, построен в соответствии со вторым пунктом формулы изобретения. Последовательно с дополнительным резистором 15 включен эмиттерно-базовый переход дополнитель ного транзистора 24. Нижнее плечо делителя выходного напряжения выполнено в виде резистора 25.

В установившемся режиме напряжения на втором входе 6 параллельно-балансного каскада 3 приблизительно равно напряжению на эталонном источнике 4 (IJ > — V )

Для устранения самовозбуждения в области высоких частот в схему введен корректирующий конденсатор 8. Он вносит уменьшение усиления по петле обратной связи с весьма низких частот (единицы †десят

Герц). В то же самое время транзисторы, применяемые в типовых стабилизаторах, имеют граничные частоты, измеряемые сотнями мегагерц. Поэтому конденсатор 8 является самым инерционным элементом в схеме компенсационного стабилизатора.

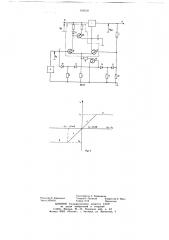

Основной особенностью параллельно-балансного каскада, определяющей быстродействие стабилизатора, является то, что он име ет узкий динамический диапазон. Если модуль напряжения между базами транзисторов 18 — 19 в переходном режиме превышает

50 мВ (! Б1э — Цsl >)Ц; 50 мВ), выходной о з зо

25 зо

40 ток каскада (i ) являющийся зарядным (разг рядным) током конденсатора 8, ограничивается (фиг. 3) .

Предположим, что ток в нагрузке стабилизатора уменьшается, причем приращение тока имеет прямоугольную форму. Это приводит к скачкообразному изменению напряжения на выводе 17, которое через резистор 7 поступает на базу транзистора 19 (Ujg возрастает). Стабилизатор отрабатывает появившийся сигнал рассогласования между Uj, и Ujq. При этом наибольший интерес представляют два случая. Первый, когда сигнал рассогласования мал (Uje — Ujg (V, =50 мВ), второй — когда сигнал рассогласования велик (U j g — U j jj >>

)) Ug 50 м В), где U jj — пороговое на и ряжение каскада 3.

В первом случае параллельно-балансный каскад работает на участке А проходной характеристики 1„.= f(Vj g — Ц8 ) фиг. 3. Стабилизатор ведет себя как линейная система автоматического регулирования. Время установления выходного напряжения — tjlj., как и любой линейной системы первого порядка, минимально и не превышает величины

3 + 4/2лfcp. где f p — частота единичного усиления по петле обратной связи.

Во втором случае, когда (Ujgj — Ujjj())

)) U>50 мВ, параллельно-балансный каскад входит в режим ограничения. Между его выходным током i è сигналом рассогласования U j g — U j jj нарушается пропорциональность (фиг. 3, участок В). Конденсатор 8 перезаряжается сравнительно небольшим но величине током, численно равным току

Ijj двухполюсника 2. Напряжение на конденсаторе 8 и, следовательно, на выходе стабилизатора изменяется по линейному закону. Время установления переходного процесса стабилизатора в данном режиме как и любой нелинейной системы, имеющей сопутствующую нелинейность во входной цепи, в десятки раз превышает „,, рассчитанное для линейного режима работы.

В стабилизаторе повышение быстродействия при больших скачках тока в нагрузке достигается за счет форсирования процесса перезарядки конденсатора 8 с помощью цепи нелинейной коррекции, состоящей из элементов 9 — 15. Цепь нелинейной коррекции не влияет на работу стабилизатора, если сигнал рассогласования мал, и наоборот, начинает функционировать при перегрузке параллельно-балансного каскада, когда (Uj g — Ujal >>Ujj50 мВ.

Если Ujg — Vjg »50 мВ, транзистор 16 входит в отсечку, а напряжение на эмиттере транзистора 19 начинает повторять изменение Ujq. Это приводит к увеличению напряжения на диоде 13. Последний открывается, что обуславливает увеличение тока эмиттера транзистора 19 за счет перераспределения тока резистора 9 между диодами

658539

Формула изобретения

5

10 и 13. Выбирая надлежащим образом сопротивления резисторов 9 и 15, можно более чем на порядок увеличить разрядный ток конденсатора 8 или во столько же раз повысить быстродействие стабилизатора.

Если напряжение на выходе стабилизатора уменьшается, причем tV S — u„) ))

)>50 мВ, приращение зарядного тока конденсатора 8 обеспечивается аналогичным образом через диод 14.

Для повышения экономичности стабилизатора между общей точкой диодов 13 — 14 и резистором 15 рекомендуется включать дополнительный транзистор 2Й (фиг. 2) . Введение транзистора 24 позволяет выбирать рабочие точки вспомогательных делителей напряжений относительно малыми (порядка нескольких сотен микроампер). Это уменьшает общую мощность, потребляемую стабилизатором от источника питания в режиме холостого на выходе.

Момент включения цепи нелинейной коррекции в работу можно изменять по усмотрению разработчика путем введения в верхние плечи второго и третьего делителей напряжения не по одному, а по два диода. В некоторых случаях рекомендуется последовательно с диодами 10 и 11 вводить низкоомные резисторы.

При скачкообразном изменении напряжения эталонного источника 4 предложенный стабилизатор работает аналогично. Поэтому схема на фиг. 1 может использоваться и в быстродействующих программируемых источниках питания, в которых уровень стабилизируемого напряжения устанавливается путем коммутации резисторов делителя выходного напряжения или путем дискретного изменения эталонного напряжения.

1Ю

zo

1$ зо

3$ I. Стабилизатор постоянного напряжения, содержащий регулирующий элемент, включенный в одну из силовых шин, токостабилизирующий элемент, включенный в общую эмиттерную цепь параллельно-бала нсного каскада, первый вход которого подключен к источнику опорного напряжения, второй вход — к выходу первого дел ител я, подкл кгченного к выходным выводам, а выход параллельно-балансного каскада ггодключегг к конденсатору и ко входу регулирующего элемента, отличающийся тем, что, с целью повышения быстродействия стабилизатора, в него дополнительно введены второй и третий делители напряжения, каждый из которых выполнен на резисторе и диоде. причем второй делитель включен параллельно источнику опорного напряжения, третий делитель включен между общей шиной н выходом первого делителя, а вы. оды третьего и второго дел и тел ей соединены через встреч но включенные дополнительно введенные диоды, общая точка которых подключена к общей эмиттерной цепи параллельно-балансного каскада через дополнительно введенный резистор.

2. Стабилизатор по п. 1, от.гuчaгогиuгicя тем, что в него дополнительно введен транзистор, эмиттер-базовый переход которого включен между дополнительным резистором и обшей точкой дополнительныx диодов, а коллектор соединен с обшей шиной.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 393025, Q 05 F 1/56, 1971.

2. Патент США № 3321698. кл. 323 — 16, 1968.

658539

Составитель С. Чернышева

Редактор Е. Кравцова Техред О. Луговая Корректор Е. Папп

Заказ 2056/43 Тираж 1014 Подписное

ЦН И И П И Государственного комитета СССР по делам изобретений и открытий

1 1 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал П П П «Патент», г. Ужгород, ул. Проектная, 4