Преобразователь кода грея в двоичный код

Иллюстрации

Показать всеРеферат

пв ен не те ничесн; в б олиэTE.;ла Ii1 Б h

Союз Советских

Соцналистнцескнх

Республик

ОП ИСАЙИ Е

ИЗОЬРИтЕНИЯ

К АВТОРСКОМУ СВИДИТИЛЬСТВУ (6l) Дополнительное к авт. свид-ву— (2 ) Заявлено22.11.76 (21) 2423178/18-24 с присоединением заявки №(23) Приоритет

Опубликовано 25.04.79Бюллетень № 15

658555 (51) M. Кл.

Cs О(i Р 5102

Гасударственный ввнвтвт

СССР вв делвм нзвбретеннв н вткритнй (53) УДК 681.82. (0,88.8) Дата опубликования описания 28.04. 79 (72) Авторы изобретения

Ю. 3. Воробьев, Т. К. Воробьева и B. A. Грехнев (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ КОДА ГРЕЯ В ДВОИЧНЬ1Й K0Il

Изобретение относится к области циф. ровой вычислительной техники и может быть использовано в вычислительных и телеметрических системах.

Известен преобразователь кода Грея в двоичный код, содержащий сдвиговый регистр, полусумматор и элемент И 11) .

Недостатком данного устройства является низкая скорость преобразования, связанная с последовательным принципом работы.

Ближайшим техническим решением цанной задачи является преобразователь, содержащий регистр и первую цепь сдвига, входы которой подключены к выходам регистра 1 21.

Недостатком известного устройства является относительно большой обьем аппаратуры, связанный с необходимостью использования регистра двоичного кода и большого количества полусумматоров

20 и ограниченность функциональных возможностей, вследствие того, что регистр нельзя использовать для других целей.

1..1елью изобретения являегся упрощение устройства и расширение его функциональных возможностей путем обеспечения параллельного и последовател :ного приелла информации в регистр полгимо функций преобразования.

Эта цель достигается тем, что предлагаемое устройство содержит (1 1 )(=le(>t4j, где A — количество разрядов числя цепей сдвига, группу элементов ИЛИ, — тый вход которых соединен с выходом ) - той цени сдвига, а выход — с информационным входолr регистра, шина сигнала преобразования соединена с управляюшими входами регистра, выходил которого соединены с первыми входами цепей сдвига, каждая из К шин управления сдвигом соединена со вторым входом соответствующей цепи сдвига.

Другое отличие предложенного устройства состоит в толл, что в нем разряды регистра содержат триггер, два элемента И-НЕ и элемент 11-11Л11-НЕ, первый и второй входы которого со .динены с выхо3 6, дами элементов И-HE соответственно, а выход соединен с входом триггера, шина управляющего входа разряда регистра соединена с первыми входами элементов

И-HE и с третьим входом элемента

И-ИЛИ-НЕ, шина информационного входа разряда регистре соединена со вторым входом первого элемента И-НЕ и четве тым входом элемента И-ИЛИ-НЕ.

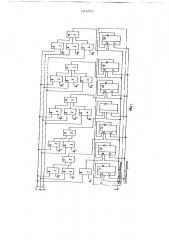

Блок-схеме преобразователя приведена на,фиг. 1, элементная схема одного разряда при использовании Д-триггера приведена на фиг. 2. Преобразователь (см.фиг. содержит регистр 1, первую цель 2 сдвига на один реэряд, втооую цепь 3 сдвига на два разряда, К-ю цепь сдвига 4 на к-

2 разрядов, группу элементов ИЛИ 5, шину сигнала преобразования 6 и шины сигналов управления сдвигом 7 - 9, Каждый разряд регистра памяти коде, Грея (см. фиг. 2) содержит триггер 10, первый 11 и второй 12 элементы И-HE и элемент И-ИЛИ-НЕ 13. Разряд имеет информационный вход 14,и управляющий вход 15. Установка триггера 10 в состояние "0 и 1 " производится сигналами по входам 16 и 17. Изменение состояния триггера происходит при поступлении синхросигнела на вход 18. На фиг. 2 приведена конструкция разряда при исподьзовании Д-триггера, хотя возможно применение триггеров других типов.

Логическая схема разряда функционирует следующим образом: при подаче нулевого уровня на управляющий вход 15 и синхросигнала на вход 18 состояние выхода триггера повторяет состояние информационного входа 14 (при соединении выхода триггера со входом 1 9). Таким

4 образом, при этих условиях разряд реализует логику Д-триггера. При подаче на управляющий вход 15 триггера .единичного уровня и синхросигнала на вход 1 8 новое состояйие триггера определится как сум4 ма по модулю два кодов предыдущего состояния триггера 10 и состояния информационного входа 1 4.

Предлагаемое устройство работает следующим образом.

Перед началом работы регистр 1 обнуляется по входам 16 сигналом, соответствующим логическому нулю. По входам

1 7 сигналами, соответствующими инверсиям разрядов подлежащего преобразованию кода Грея, осуществляется параллельный, е по входу 14 "триггера с аршего (слева на фиг. 1) разряда при наличии на шине 6 сигнала "ПРЕОБРАЗОВАНИЕ, 58555 4 соответствую1цего логическому нулю,последовательный прием кода Грея в регистр. (Входы 16 и 17 на фиг. 1 не покезаны ). Пусть в триггеры регистра будет записан подлежащий преобразованию код Грея $.... 61, где b 0,1 - разряды коде Грея и i e1,2,...,8 - номера разряр- дов.

На шину "ПРЕОБРАЗОВАНИЕ в режи10 ме преобразования должен быть подан сигнал, соответствующий логической единице.

На первом шаге преобразования на ши1 ) ну 7 подается единичный уровень, а на

8,9 нулевой Ц6 Q =6 Q о и, следоа1 ri В вательно, на входы 19 триггеров регист-, ра будут воздействовать сигналы:

611 > br в 6З Ь4 Ь bZ о1

На входы 14 этих триггеров воздеЛ-, 20 ствуют сигналы

О 68»7 6в ), °

Таким обрезом, первым синхроимпульсом триггеры регистра будут установлены

25 в состояния что является результирующим словом первого шага. К моменту поступления второго синхроимпульса единичный сигнал поступает на шину 8 и, следовательно, на входы 9 триггеров регистра воздействуют логические сигналы е на входы 14 этих триггеров логические сигналы

0,%Ь,(Э ОЬ, ЬтО Ь ЬбОЬ

b,ÅÜ4 ",Эь, .

Таким образом, вторым синхроимпульсом триггеры регистра будут установлены в состоянйя

6,Ь ЮЬ„Ь ЗЬ ()6 Ь e...+b„b В..аь, 6 " 3 с что является результирующим словом второго шага. К моменту прихода третьего синхроимпульса единичный сигнал подается на шину 9 и, следовательно, на входы

19 триггеров регистра воздействуют логические сигналы

Ь ЬЯЬ Ь896 О+Ь,Ь (Э...ЭЬ 6 Э...®b ) 5 6585 а на входы 14 этих триггеров логические сигналы

0,0,0,0. Ь8, ь,еь, Ь89Ь,еьм

Источники инфорл)ации, принятые во внимание при экспсртиэе

l. Авторское свидетельство C(СР

No 137311, кл. G 06 V 5/02, 1668.

2. Патент ФРГ М". 1.301.836, кл. 21 а 36/20, 1971.

Ь8® Ь29 ЬбО ов

Но тогда третьим синхроимпульсом ре гистр будет установлен в состояние

Ь, Ь 9Ь ) Ь ®" 9Ь; Ь 9...9Ь5) Ь 9...9Ь4, ЬЕ...ЕЬ, ЬЕ...ЕЬ„(,(Э.. ®Ь, 3) 2) 8 что является результирующим словом третьего шага, или, в соответствии с алгоритмом преобразования кода Грея в двоичный кол, двоичным KolloM.

0) 7) Я 1 5 ) 4 3) 2 а а а

Таким образом, предлагаемое устройство реализует алгоритм ускоренного преобразования кода Грея в лвоичный

20 код.

Так как в режиме ПРЕОБРА3ОВАНИЕ" предлагаемое устройство осуществляет преобразование

Q,(<+3)=QK(t)QiQÄÄ(t) р гдеЯ - состояние К-го триггера регистк ра, то полагая

Q (1)=Ок и Я„, f<) 1 будем иметь

К(1i - а,o c) „, >„))

30 глечик - значение К-го разряда двоичного кода, соответствующего коду Грея.

Таким образом, предлагаемое устройство может быть использовано также для преобразования двоичного кола в код Грея, 35 может осушествляться параллельный прием информации в регистр и использоваться как сдвиговый регистр с изменяемым количеством разрядов сдвига.

Предлагаемое устройство более эконо- 40 мично. По сравнению с известными преобразователями (21 оно требует при количестве разрядовл 2О в 1,5 раза меньше оборудования.

Формула иэобретени я

1. Преобразователь кода Грея в лвоичный код, содержащий регистр и первую цепь сдвига, входы которой подключены к выходам регистра, о т л и ч я ю щ и йс я тем, что, с целью упрощения устройства и расширения функциональных возл1ожностей путем обеспечения преобразования как последовательных, так н параллель)п,)х кодов, он содержит(Х-111л Eo(п гле и - количество разрядов числя цепей сдвига, группу элементов ИЛИ, ) -й вход которых соединен с пьrxoaoM i -й цепи сдвига, а выход - с информационнылл входом регистра, шина сигнала преобразования соединена с управляющими входами регистра, выходы которого соединены с первыми входами цепей сдвига, каждая иэ

К шин управления сдвигом соединена со вторым входом соответствующей цепи сдвига.

2. Преобразователь кода Грея в двоичный код по и. 1, î r л н ч я ю ш и й— с я тем, что в нем разряды регистра содержат триггер, двя элемента H-НЕ и элемент И-ИЛИ-НЕ, первый и второй входы которого соединены с выходами элементов

И-НЕ соответственно, я выход соединен с входом триггера, шина управляющего входа разряда регис ра соединена г первыми входами элементов И-1!Г и с третьим входом элемента И-HJlH-HE, шина информационного входя разряда регистра со .— динена со вторым входол1 первого злел1гпт:)

И-HE и четвертым вколол) элемента

И-ИЛ И-НЕ.

Уиа Я

Составитель М. Аршавский

Редактор Н. Веселкина ТехредА. Богдан Корректор O. Ковинская

Заказ 2058/44 Тираж 779 Подписное

ЦНИИПИ Государственного комитета СССР по делам иэобретений и открьгтий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", r. Ужгород, ул. Проектная, Ъ