Устройство для контроля на цикличность

Иллюстрации

Показать всеРеферат

О П И С А Н- И""E

ИЗОБРЕТЕН ИЯ

Фф„ % ъ

<»658562

Союз Советских

Социалистимвских

Республик (6l) Дополнительное к авт. свиа-sya (22) Заявлено 09.02.77 (21) 2450725/18-24 (53} M. Кл. с присоединением заявки № (23) Пртворитет

Е 06 К 11r00

Гвсудврственнмй квинтет

СССР кв делам нзоаретеннй н вткрмтнй

Оаубликовано25.04.79.бюллетень % 15 (53) УДК 681.327 (088.8) Дата опубликования описания 28.04.79 (72) Л втор, изобрехеиив

В. Н. Зорихин

P l) Заиввтель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ HA ЦИКЛИЧНОСТ6

Изобретение относится к области въiчислительной техники и может найти применение в цифровых вычислительных ма. шинах (UBN), осуществляющих контроль времени выполнения программ.

Известно устройство для контроля на: цикличность, содержащее блок памяти, внешний блок памяти, устройство ввода, счетчик и блок управления (1 1.

Недостатком известного устройства является низкая надежность при определении времени выполнения программы, так как программа, реагирующая на прерывание по зацикливанию, может не находится в основной памяти, а для передачи управ15 ления этой программе ее необходимо ввести в основную память, что не всегда удается при наличии зациклинивания.

Наиболее близким техническим решением к изобретению является устройство для контроля на цикличность, содержащее триггер и счетчик циклов f. 2l

Недостатком известного устройства является низкая достоверность контроля.

При обнаружении зацикливания, которое может быть следствием неисправности оборудования, происходит вызов программы, которая должна, осуществить контроль аппаратуры (программы) и проинформировать обслуживающий персонал о случившемся, организовать продолжение реШения задачи с определенного места программы.

Однако при очень многих неисправностях аппаратуры, вызывающих зацикливание программы, невозможно организовать прерывание, или сама прерывающая программа зациклится.

Целью изобретения является повыше ние достоверности контроля. Поставленная цель достигается тем, что устройство дополнительно содержит первый, второй и третий элементы И, первый и второй эле менты ИЛИ, регистр, блок вычитания, счетчик совпадений, первый и второй блок сравнения, выход первого элемента И сое динен со входом регистра, выход регистра соединен с первым входом первого блока сравнения, второй sxoa которого соединен

658562 с. выходом блока вычитания, первый выход первого блока сравнения соединен с первыми входами первого элемента ИЛИ, счетчика циклов и блока вычитаний, первый выход счетчика циклов соединен со вто- 5 рым входом блока вычитаний и с первым входом второго блока сравнения, выход которого является выходом устройства, второй выход счетчика циклов соединен соответственно с первым входом второ- 10 го элемента ИЛ 4 и со вторыми входами счетчика циклов и первого элемента ИЛИ, выход которого соединен с первым вход- . дом счетчика совпадений, второй выход первого блока сравнения соединен со вто- И рыми входами второго элемента ИЛИ и счетчика совпадений, выход которого соединен со вторым входом второго блока сравнения, выход второго элемента ИЛИ соединен с единичным входом триггера, Ф единичный и нулевой выходы которого соединены с первыми входами второго и третьего элементов И, выход второго элемента И соединен с первым входом первого элемента И, с третьим входом блока вычитания и с нулевым входом триггера, тактовый вход устройства соединен со вторыми входами второго и третьего элементов И, информационный вход устройства соединен со вторым входом первого элемента И, с третьим входом первого блока сравнения, выход третьего элемента И соединен с четвертым входом блока вычитания.

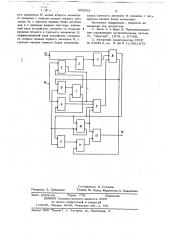

На чертеже представлена структурная

35 схема устройства. . Устройство для контроля на цикличность содержит триггер 1 первый, второй и третий элементы И 2, 3, 4, соответст40 венно первый и второй элементы ИЛИ 5-6, регистр 7, первый блок сравнения 8, блок вычитания 9, счетчик циклов 10, счетчик совпадений 11, второй блок сравнения 12, информационный 13 и тактовый 14 входы

45 и выход 15 устройства.

Устройство работает следующим образом.

На вход устройства 13 подаются данные из НВМ, подлежащие запоминанию или сравнению с ранее запомненными, которые поступают на третий вход первого блока сравнения 8 и информационный вход элемента И 2. На тактовый вход устройства 14 подаются из UBM импульсы (по одному на каждую команду), которые поступают на вторые входы элементов И

3-4, первые входы которых соединены соответственно с единичным и нулевым выхоцами триггера 1. Таким образом, в зависимости от состояния триггера 1 импульсы будут проходить по разным каналам.

При единичном состоянии триггера 1 тактовый импульс через второй элемент

И 3 попацает на управляющий вход первого элемента И 2, по этому сигналу информация со входа 13 запишется в регистр

7 и поступит на первый вход первого блока сравнения 8. Одновременно с этим, с выхода второго элемента И 3 пройдет импульс на нулевой вход триггера 1 и установит его в нулевое состояние, также поступит на третий вход блока вычитания 9, по сигналу которого через информационный вход в блок вычитания 9 будет считано содержимое счетчика цикла

10. При нулевом состоянии триггера 1 тактовые импульсы через третий элемент

И 4 будут поступать на счетный вход блока вычитания 9, уменьшая каждый раз содержимое его на единицу. При обнулении с выхода блока вычитания 9 сигнал поступит на управляющий вход первого блока сравнения 8, разрешая сравнение данных по его первому и третьему входам.

Таким образом, будут сравниваться данные по команцам, отстоящим друг от друга на величину, записанную в счетчике циклов 10. С выхода первого блока сравнения 8 сигнал совпадения попадает на счетный вход счетчика совпадений 11, увеличивая его значение на ециницу, и через второй вход второго элемента ИЛИ

6 на единичный вход триггера 1, подготавливая его к приему данных следующей команды. При попадании на цикл содержимое счетчика совпадений 11 будет увеличиваться, пока не достигнет значения, записанного в счетчике циклов 1 0; а это значит, что будут проверены все команды цикла. В этом случае второй блок сравнения 12, первый вход которого связан с информационным выходом счетчика циклов 10, а второй вход — с выходом счетчика совпадений ll, выработает сигнал обнаружение цикла" и выдаст его на выход устройства 15. Сигнал же несовпадения с выхода первого блока сравнения

8 попацет на счетный вход счетчика циклов 1 О, увеличивая его значение на один шаг, на установочный вход блока вычитания 9, присваивая ему значение шага, и через первый вход первого элемента ИЛИ

5 иа установочный вход счетчика совпадений 1 1, присваивая последнему нуле6-э 8562 вое значение„ Таким образом, при несовпадениях значение счетчика циклов

10 будет постепенно увеличиваться, пока не произойдет переполнение, сигнал о котором с выхода счет iHKa циклов 10 поступит на его установочный ехоп и приведет, счетчик циклов 10 в на !альное состояние. Кроме того, сигнал переполнения через первый вход второго элемента ИЛИ 6 поступит на единичный вход триггера 1, подготавливая его к приему новых данных, а через второй вход первого элемента ИЛИ 5 установит счетчик числа совпадений в нулевое положение.

Устройство может быть дополнено установочным входом, который следует соединить с выходом переполнения счетчика циклов 10. В этом случае, пропуская импульс через установочный вход, 26 можно будет приводить устройство в начальное состояние.

Предлагаемое устройство может быть использовано и в мультипрограммных

HBN. В этом случае требуется обеспе25 чить возможность списывания содержимого устройства при прерывании программы и возможность записи нового содержимого при загрузке следующей программы.

Зо

Для этого достаточно снабдить устройство дополнительными входами и выходами, которые следует соединить, соответственно с информационными входами и выходами триггера 1, регистра 7 блока вычита- .

35 ния 9, счетчика циклов 10 и счетчика совпадений 11.

Если встретится программа с циклическими участками, включающими операции ввода, например с телетайпа, и при

40 анализе такого участка случайно будут вводиться одни и те же данные, устройство выдает сигнал обнаружения цикла.

В то же время при вводе других данных произойдет выход из цикла. Для исключения таких специфических случаев между регистром 7 и блоком сравнения 8 можно вставить схему выделения опера» ций ввода, управляющий выход которой следует соединить с выходом переполне- р ния счетчика циклов 10.

Дополнительные элементы, ввиду очевидности их размещения, на чертеже не показаны.

Поиск цикла можно разделить на два у этапа: выход на цикл и проверка достоверности обнаружения цикла по каждой его комаде. Время по второму этапу находится в квадратичной зависимости от величин...! liHKJlB, исходя из ч с учетом быстродействия UBM и следует назначить емкость счетчика цикла. Время по первому этапу не зависит от величины цикла и может быть сокращено в соответствующее число раз путем применения в одной

ЦВМ сразу нескольких предлагаемых устройств, при этом шаг изменения счетчика цикла должен соответствовать числу примененных устройств, а начальные состоял!!я их должны быть сдвинуты последовательно на единицу. В этом случае устройства будут работать независимо друг от друга, обеспечивая в сумме полный . контроль программы.

Таким образом, предлагаемое устройство позволяет без дополнительных затрат машинного времени проиэводить 100-процентный контроль программы на цикличНость непосредственно в процессе счета.

Формула изобретения

Устройство для контроля на цикличность, содержащее триггер, счетчик циклов, о т л и ч а ю щ е е с я тем, что, с цепью повышения достоверности контроля устройстводополнительносодержит первый, второй и третий элементы И, первый и второй элементы ИЛИ, регистр, блок вычитания, счетчик совпадений, первый и второй блок сравнения, причем выход перво го элемента И соединен со входом регистра, выход регистра соединен с первым входом первого блока сравнения, второй вход которого соединен с выходом блока вычитания, первый выход первого блока сравнения соединен с первыми входами первого элемента ИЛИ, счетчика циклов и блока вычитания„ первый выход счетчика циклов соединен со вторым входом блока вычитания и с первым входом второго блока сравнения, выход которого является выходом устройства, второй выход счетчика циклов соединен соответственно с первым входом второго элемента ИЛИ, со вторыми входами счетчика циклов и первого элемента ИЛИ, выход которого соединен с первым входом счетчика совпадений, второй выход первого блока сравнения соединен со вторыми входами второго элемента ИЛИ .и счетчика совпадений, выход которого соединен со вторым входом второго блока сравнения, выход второго элемента ИЛИ соединен с единичным входом триггера, единичный и нулевой выходы которого сое динены с первыми вхоцами второго и треть62

Сог..тавитель И. Сигалов

Техред М. Петко Корректор О. Ковинская

Редактор Э. Губницкая

Заказ 2058/44 Тираж 779 . Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская ыаб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 v: „4„/,: ф % 6585 г, его элементов И; выход второго элемента

И соединен с первым входом первого элемента И, с третьим входом блока вычитания и с нулевым входом триггера, тактовый вход устройства соединен со вторыми 5 входами второго и третьего элементов И, информационный вход устройства соединен со вторым входом первого элемента И, с третьим входом первого блока сравнения, выход третьего элемента И соединен с четвертым входом блока вычитания.

Источники информации, принятые во внимание пои экспертизе

1. Беме -Г. и Бори B. Программирование управляющих вычислительных систем

М., Энергия", 1975. с. 67-68.

2. Авторское свидетельство СССР №. 439813, кл. 6 06 F 11/00,1975.