Устройство для выборки информации из блоков памяти

Иллюстрации

Показать всеРеферат

О П И С А Н И Е () 658598

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву—

Союз Советских

Социалистических

Республик (22) Заявлено 29.09.75 (21) 2176038/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М Кч

G 11 С 7/00

Государственный квинтет

СССР на делам нзоорвтвннй н открытий

Опубликовано 25.04.79. Бюллетень № 15

Дата опубликования описания 05.05.79 (53) УДК 628.327..6 (088.8) (72) Авторы изобретения

А. А. Вихров, Л. И. Лазаренков, В. Н. Тихомиров и Б. Г. Хвалько (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫБОРКИ ИНФОРМАЦИИ

ИЗ БЛОКОВ ПАМЯТИ

Изобретение относится к области приборостроения и может быть использовано в аппаратуре сбора и обработки информации, в различных устройствах автоматики, телемеханики и вычислительной техники. 5

В устройствах сбора и обработки информации различные параметры требуется опрашивать с различной частотой в зависимости от скорости изменения величины параметра.

С этой целью в устройства вводится адрес1О ная система, позволяющая распределять потоки информации во времени.

Известны устройства с последовательной выборкой слов из запоминающего устройства, где каждому значению кода управления, который является кодом адреса для запоми- 1s нающего устройства, соответствует адресное слово. Количество одинаковых адресных слов определяет частоту обращения к объекту. Обращение к объекту с повышенной частотой производится через равные промежутки времени в цикле регистрации. Код адресного слова можно условно представить в виде адресных разрядов и разрядов частоты обращения, а число нулей в старших разрядах кода адресного слова определяет частоту обращения к объекту (1).

Наиболее близким к предложенному является устройство для выборки информации из блоков памяти, содержащее ключ для элемента, входы которого соединены с соответствующими входами блока памяти, а выходы подключены к выходным шинам (2).

Известное устройство для своей реализации требует значительных аппаратурных затрат, которые определяются объемом памяти для регистрации входной и промежуточной информации, объемом памяти постоянного запоминающего устройства адресных слов, записанных на перфоленте или перфокарте, что, в конечном итоге, увеличивает габариты устройства, его вес и снижает надежность.

Целью настоящего изобретения является повышение надежности и быстродействия устройства путем снижения потери времени на ввод информации.

Поставленная цель достигается тем, что устройство содержит блок логического умножения и генератор кода множителя, один

658598 адресного слова, соответствующий адресу объекта и частоте обращения к нему. В блок ть памяти 7 записываются только те адреса. частота обращения к которым больше единицы.

Кроме того, вход генератора кода множи- 30 теля 5 соединен с входной шиной 4 младшего разряда блока памяти, а выход с управляющим входом ключей элементов 6, выхоУстройство работает следующим образом. 3s

Изменение кода управления на входных шинах 4 регистрируется в генераторе кода множителя 5,который формирует сигнал запрета, подаваемый на управляющий вход ключей элементов 6. Длительность сигнала запрета определяется временем формирования

40 кода адресного слова. Кроме того, код управления по входным шинам 4 поступает на входы элементов И вЂ” НЕ 2, элементов НЕ 3 блона вторые входы элементов И вЂ” НЕ 2 подаются с генератора кода множителя 5 параллельные коды убывающей последовательности нулей 000..., 100..., 110..., и т. д., период следования которых на несколько порядков меньше периода обращения к объекту. Эти коды изменяют разряды частоты обращения io кода управления.

Значения произведений кодов с выхода блока логического умножения 1 в прямом и инверсном виде поступают на входы блока памяти 7, где параллельно сравниваются при помощи элементов И 8 со значениями адресных слов, запрограммированных на их вход которого подключен к входной шине младшего разряда блока памяти, а выходы генератора кода множителя подключены к одним входам блока логического умножения и к управляющему входу ключевых элементов, другие входы блока логического умножения подключены к входным шинам, а выходы — к соответствующим входам блока памяти, а также тем, что блок памяти выполнен в виде программируемого дешифратора.

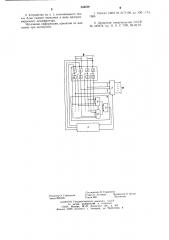

На чертеже изображена блок-схема устройства.

Устройство состоит из блока логического умножения 1, содержащего последовательно соединенные элементы И вЂ” НЕ 2 и элементы НЕ 3, ко входам которых подключены входные шины 4 и выходы генератора кода множителя 5. Выходы блока логического умножения 1 поразрядно подключены ко входам ключей элементов 6 и параллельно им ко входам блока памяти 7.

В блок памяти 7, который является программируемым дешифратором, при помощи элементов И 8, выходы которых через элемент ИЛИ 9 подключены ко входу генератора кода множителя 5, записывается код ды которых соединены с выходными шинами

10. ка логического умножения 1. Одновременно входах, до момента совпадения. В момент

15 о

4 совпадения на выходе элементов И 8 формируется сигнал, который через элемент ИЛИ 9 поступает на вход генератора кода множителя 5, в результате чего фиксируется результат логического умножения, т. е. генератор кода множителя 5 будет выдавать данное значение кода, пока его произведение на разряд кода управления, определяющее частоту обращения, будет равно адресному слову, записанному в блоке памяти.

Одновременно с управляющего входа ключей элементов 6 будет снят запрет и значение адресного слова, выраженное произведением, поступит на выходные шины 10.

Если в блоке памяти 7 не будет обнаружено кода, совпадающего со значением произведения, то в момент поступления на входы блока логического умножения 1 с выходов генератора кода множителя 5, все разряды которого будут содержать единицы, последний снимает запрет с ключей элементов и код управления как адресное слово поступит на выходные шины 10.

Использование блока логического умножения и генератора кода множителя позволило сократить объем памяти устройства, увеличив его быстродействие, так как в блоке памяти и сравнения все запрограммированные коды адреса опрашиваются параллельно.

Использование в качестве блока памяти и сравнения программируемого дешифратора позволяет исключить дополнительную схему сравнения и сократить объем памяти на

50 — 80 /р, что значительно снижает потери времени на ввод программы. В предложенном устройстве ввода адресных слов снижены аппаратурные затраты, а следовательно, повышена надежность устройства, уменьшен вес и габариты.

Формула изобретения

1. Устройство для выборки информации из блоков памяти, содержащее ключевые элементы, входы которых соединены с соответствующими входами блока памяти, а выходы подключены к выходным шинам, отличаюи1ееся тем, что, с целью повышения надежности и быстродействия устройства путем снижения потери времени на ввод информации, оно содержит блок логического умножения и генератор кода множителя, один вход которого подключен к входной шине младшего разряда блока памяти, другой к выходу блока памяти, а выходы генератора кода множителя подключены к одним входам блока логического умножения и к управляющему входу ключевых элементов, другие входы блока логического умножения подключены к входным шинам, а выходы — к соответствующим входам блока памяти.

658598

Составитель В. Гордонова

Техред О. Луговая Корректор О. Билак

Тираж 680 Подписное

Редактор Э. Губницкая

Заказ 2064/46

ЦНИИПИ Государственного комитета СССР по делам изобретений и открьпий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

2. Устройство по п. 1, отличающееся тем, что блок памяти выполнен в виде программируемого дешифратора.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3171100, кл. 430 †1, 1965.

2. Авторское свидетельство СССР № 445974, кл. G 111 1 С C 77//0000, 06.03.72.