Устройство для сравнения двух электрических сигналов по фазе

Иллюстрации

Показать всеРеферат

ОП ИСАНИ

ИЗОБРЕТЕН ИЯ

Союз Советскмз

Соцмалмстмческмх

Реснублнн (6t) Дополнительное к авт. свиа-ву (22) ЗаявлЕно 21.03.77(2l) 2465367/2 с присоединением заявки №вЂ” (23) Приоритет

Гееудврстееииый иаметет

СССР еа делам изобретений и открытий

Опубликовано25.04.79. Бюллетень №

Дата опубликования описання27.04. (72) Авторы изобретения

P. К. Контаутас и А. В. Бипявичюс (7!) Заявители (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВУХ ЭЛЕКТРИЧЕСКИХ

СИГНАЛОВ ПО ФАЗЕ

Изобретение относится к области распредепения эпектрической энергии, а именно к схемам автоматизации энергосистем, и может быть использовано дпя сравнения двух электрических сигнапов по фазе, например, в схемах релейной зашиты .

Известен фазовый детектор, содержащий подключенные к нагрузке фазоинверсные каскады на транзисторах, в цепь эмиттеров которых вкпючен транзистор, управляемый опорным напряжением. Выходное напряжение детектора получают суммированием выходных сигналов каждого попупериода входного сигала(1).

Однако известный фазовый детектор отличается малой чувствительностью и недостаточввтм быстродействием.

Наибопее близким к предлагаемому является устройство сравнения двух электрических сигналов по фазе, содержашее резисторы, подключенные к отрицатеш ному. попюсу источника постоянного напряжения, и блок совпадения, входы которого подсоединены к источникам сравниваемых сигнапов (2 J.

Недостатком известного устройства является недостаточная чувствительность и невозможность определения знака рассогласования фаз сравниваемых сигналов.

Цепью изобретения является повышение чувствительности устройства.

Поставпенная цепь достигается тем, что в устройстве дпя сравнения двух электрических сигналов по фазе, содержашем, резисторы, подключенные к отрицатепьному полюсу источника постоянного напряжения, и блок совпадения, входы которого подсоединены к источникам сравниваемых сигналов, блок coanageния выполнен в виде двух поспедоватепьно соединенных транзисторов, включенных между положительным полюсом источни20 ка постоянного напряжения и эмиттерами других двух транзисторов, причем между базами и эмиттерами последних подключены источники опорных противоположных

658645 по фазе напряжений, а их коллекторы подсоединены к упомянутым резисторам.

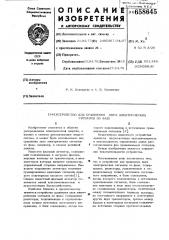

Сущность изобретения поясняется чертежами.

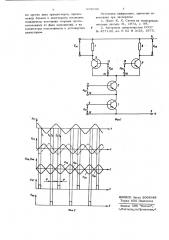

На фиг. 1 изображена схема устройства, на фиг. 2 показана временная диаграмма его работы, на которой Ц,, Ц - сравниваемые сигнапы; tJ

o — опорные противоположные по Фазе напри>кения; Ц„, ц -напряжения на выхо де ус тр ой ства.

Устройство содержит бпок совпадения,, выполненный в виде двух поспедоватепьно соединенных транзисторов 1 и 2.

Змиттер транзистора 1 подключен к по1е ложительному попюсу 3. источника постоянного напряжения, в то время как. коплектор транзистора 2 подсоединен к эмиттерам транзисторов 4 и 5. Между колпектором транзистора 4 и отрицательным попюсом 6 источника постоянного напря>кения включен резистор 7, а между коппектором транзистора 5 и упомянутым отрицательным попюсом 6 включен резистор 8. К базе и эмиттеру транзистора 1 подсоединены зажимы 9, 10 источника сравниваемого сигнапа У и,соответственно, к базе и эмиттеру транзистора 2 подкпючены зажимы 11, 12 источника сравниваемого сигнаиа U . Таким сг же образом к базам и эмиттерам транзисторов 4 и 5 подсоединены соответственно зажимы 13, 14 источника опор- ного напряжения U и зажимы 15, 16

35 источника опорного напряжения U

Напряжение U опережает по фазе на

90 сигналУ,a tJ 4 отстает по фазе о С на 90 от сигнала 0

Б случае рассогласования (опережения}

4Q сигнала %i относительно сигнапа Ц по фазе на величину (180о+ <р) устройство действует следующим образом:

Б промежуток времени t — t при отрицательной полуволне сигнала U<< (0д, < 0 + на зажиме 9) транзистор 1 закрыт и, независимо от состояния других транзисторов, выходные сигналы отсутствуют. В промежуток времени — t при отрицательной попувопие сигнала U (U С 0; "+" на сг зажиме 11) транзистор 2 закрыт и, независимо от состояния других транзисторов, выходные сигналы отсутствуют. В промежутоквремени1 -14 сигнап U«>

> Ои1> *О, вспедствие чего транзисторы

1 и 2 открыты. При этом опорное напряжение Ц > 0 (+ на зажиме 14)

ОЪ и транзистор 4 открыт (соответственно опорное напряжение U < 0 и транзистор 5 закрыт), На выходе устройства появпяется импупьс, выходного напряжения 1)„, продолжительность которого соответствует проме>кутку времени т.е cp . Йапее процесс повторяется.

В случае рассогласования (опережения) сигнапа U< относительно сигнала о

U по фазе на ве дичину (1 80 — (p ) (на чертеже показано. пунктиром) при закрытии хотя бы одного из транзисторов 1 и 2, на выходе устройства сигналы отсутствуют. В промежуток времени t г — t транзисторы 1 и 2 открыты. При этом опорное напряжение tJ04 0 ("+" на зажиме 16) и транзистор 5 открыт (соответственно опорное напряжение U>>C О и транзистор 4 закрыт). На выходе устройства появляется импульс выходного напряжения U>> продолжительность которого соответствует промежутку времени 4 — Q, T.e. - {д

llanee процесс повторяется.

Устройство работает вышеописанным образом, если диапазон рассогпасования сравниваемых сигнапов не превышает о о

90 (>С +90 ), что в практичес-, ких спучаях не ограничивает применения устройства.

Таким образом, в зависимости от знака рассогпасования фаз сравнительных электпических сигналов U и У на резисторе 7 или 8 появляются импупьсы, длитепьность которых пропорционапьна углу рассогласования.фаз.

Описываемое устройство отличается высокой чувствительностью, быстродействием, возможностью опре де пения знака рассогласования фаз, а также простотой реализации.

Формупа изобретения

Устройство дпя сравнения двух эпектрических сигналов по фазе, содержащее резисторы, подкпюченные к отрицатепьному полюсу источника постоянного напряжения, и бдок совпадения, входы кс торого подсоединены к источникам сравниваемых сигналов, о т л и ч а ю щ е е с я тем, что, с целью повышения чувствительности, блок совпадения выпопнен . в виде двух последовательно соединенных транзисторов, включенных между положитепьным пошосом источника постоянного напряжения - и эмиттерами других двух транзисторов, причем между базами и эмиттерами последних подключены источники опорных противопопожных по фазе напряжений, а их коллекторы подсоединены к упомянутым резисторам.

Источники информации, принятые во внимание при экспертизе

1. Лукес 10. Х. Схемы на попупроводниковых диодах. М., 1972, с, 98.

% 2. Авторское свидетельство СССР

)Чо 4-57 140, кп. Н 02 Н 3/26, 1975.

%ere.2

0НИИПИ Заказ 2069/49

Тираж 856 Подписное

Филиал ППП Патент, r.Óæãoð Dä,óë. Проектная,4