Цифровой управляемый генератор

Иллюстрации

Показать всеРеферат

m ЪБМ07

Союз Советских

Социалистически»

Республик

О П И С А Н И- Е -ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДВТВЛЬСТВУ (61) Дополнительное к авт. свид-ву

2 (22) Заявлено 20.02.78(21) 2583192/18-09 (51) M. Кл, с присоединением заявки №вЂ”

Н 03 В 19/00

Н 03 В 3/04 (23) Приоритет

Гооударотееинмй комитет

СССР ео делам изооретен»й и открыт»й

Опубликовано25.04.79.бюллетень № 15 (53) УДК 621.374. .4; 621.373.43 (088.8) Дата опубликования описания 28.04.79

А. Я. Стуль, Ю. И. Ващенко и А. А. Шахин (72) Авторы изобретения (7!) Заявитель (54) ЦИФРОВОЙ УПРАВЛЯЕМЫЙ ГЕНЕРАТОР

Изобретение относится к радиотехнике и может быть использовано в системах синхронизации с дискретной автоподстройкой час готы;

Известен цифровой управляемый генера тор, содержащий Ьадающий генератор, коммутатор, выходы которого подключены к счетным входам счетчика и блока задержки, последовательно соединенные регистр сдвига и цифровой компаратор, другой вход которого подключен к выходу счетчика, при этом выход блока задержки подключен к управляющему входу коммутатора, а установочные входы блока задержки и счетчика объединены и подключены к выходу цифрового компаратора, который является выходом цифрового управляемого генератора fl ).

Однако в таком цифровом управляемом генераторе необходимо вводить входную величину (управляющее воздействие) в

20 виде двоичного кода, тогда как реально существующей входной величиной является частота (период) входного сигнала.

Цель изобретения - обеспечение режима синхронизации при отсутствии входного сигнала. йля этого в цифровой управляемый генератор„содержащий задающий генератор, коммутатор, выходы которого подключены к счетным входам счетчика и блока задержки, последовательно соединенные регистр сдвига и цифровой компаратор, другой вход которого подключен к выходу счетчика, при этом выход блока задержки подключен к управляющему входу коммутатора, а установочные входы блока задержки и счетчика объединены и подключены к выходу цифрового компаратора, который является выходом цифрового управляемого генератора, введены счетный триггер и дополнительный коммутатор, при этом дополнительный коммутатор включен между выходом задающего генератора и сигнальным входом коммутатора, выход счетного триггера подключен к управляющим входам дополнительного коммутатора и регистра

658707 сдвига, другой вход которого подключен к выходу счетчика, установочный вход счетного триггера подключен к выходу цифрового компаратора, а другой вход счетного триггера является входом циф- 5 рового управляемого генератора.

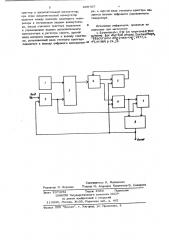

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Цифровой управляемый генератор со- 10 держит задающий генератор 1, счетный триггер 2, коммутаторы 3, 4, блок 5 задержки, счетчик 6, регистр 7 сдвига, цифровой компаратор 8.

Устройство работает следующим абра- И зом. . В присутствии входного сигнала синхронизации аппаратуры осуществляется самим входным сигналом. В отсутствие входного сигнала для синхронизации аппа- О ратуры используется предлагаемое устройство, работающее в двух режимах: режиме измерения входного сигнала и в режиме генерирования.

Рассмотрим работу устройства в ре25 жиме измерения входного сигнала. Входной сигнал попадает на счетный триггер

2. Полупериоды входного сигнала счетного триггера 2 равны периоду входного сигнала. В течение полупериода выходно:го сигнала счетного триггера 2 на выходе коммутатора 3 присутствуют импульсы с выхода задающего генератора 1. Количество импульсов за полупериод выходного сигнала счетного триггера 2 подсчитывается счетчиком блока 5 задержки и счетчиком 6. По переполнению счетчика блока 5 задержки переключается коммутатор 4 .и начинает заполняться счетчик 6.

Через период входного сигнала Т (полпериода выходного сигнала счетного триггера 2) в счетчике 6 окажется записанным число импульсов N, которое раз в период сигнала счетного триггера 2 заносится в двоичном коде в регистр 7 сдвига. При

45 этом на обоих входах цифрового компаратора 8 имеется одно и то же число

Поэтому на выходе цифрового компаратора 8 появляется сигнал, означающий

Ю конец измеряемого интервала Т и устанавливающий счетчик блока 5 задержки, счетчик 6 и счетный триггер 2 в нулевое состояние, т. е. приводящий все устройство в исходное состояние.

Рассмотрим работу устройства в режи ме генерирования (отсутствия входного сигнала). Входной сигнал не перебрасы» вает счетный триггер 2. Поэтому в этом режиме импульсы задающего генератора

1 присутствуют на выходе коммутатора 3 постоянно. Коммутатор 4, управляемый с выхода счетчика блока 5 задержки, устанавливается в положение, прН котором импульсы задающего генератора 1 попадают на счетный вход счетчика блока задержки. Если счетчик блока 5 задержки содержит К разрядов и задающий генератор 1 имеет частоту f<, то переполнение счетчика блока задержки произойдет через время т = . По переполнению

2"

Хс счетчика блока 5 задержки коммутатор 4 подключает задающий генератор 1 к счетному входу счетчика 6. Через время

N т = Koll на выход счетчика .6 совпа с дает с кодом И, записанным в регист ре 7 сдвига.

В регистре 7 сдвига записано число импульсов М, соответствующее последнему значению длительности периода 7, когда входной сигнал еще присутствовал.

Когда счетчик 6 устанавливается в состояние, соответствующее числу М, срабатывает цифровой компаратор 8, отмечая конец формирования периода т, и схема возвращается в исходное состояние. Далее процесс повторяется сначала.

С появлением входного сигнала схема автоматически переходит в режим измерения входного сигнала.

Применение предлагаемого изобретения позволяет обеспечить режим синхронизации при отсутствии входного сигнала, при этом стоимость введенных узлов незначительна и составляет менее 1% стоимости всего устройства.

Формула изобретения

Цифровой управляемый генератор, содержащий задающий генератор, коммутатор, выходы которого подключены к счетным входам счетчика и блока задержки, последовательно соединенные регистр сдвига и цифровой компаратор, другой вход. которого подключен к выходу счетчика, при этом выход блока задержки подключен к управляющему входу коммутатора, а установочные входы блока задержки и счетчика объединены и подключены K выходу цифрового компаратора, который является выходом цифрового управляемого генератора, о т л и ч а юшийся тем, что, с целью обеспечения режима синхронизации при отсутствии входного сигнала, введены счетный

658707

Составитель Н. Матвиенко

ТехРед О. Андрейко Корректор. В. Синицкая

Редактор Н. Хлудова

Заказ 2074/52 Тираж .1059 П одписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-З5, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 триггер и дополнительный коммутатор, при этом дополнительный коммутатор включен между выходом задающего генератора и сигнальным входом коммутато« ра, выход счетного триггера подключен % к управляющим входам дополнительного коммутатора и регистра сдвига, другой вход которого подключен к выходу счетчика, установочный вход счетного триггера подключен к выходу цифрового компарато ра, а другой вход счетного триггера яв ляется входом цифрового управляемого генератора.

Источники информации, принятые во внимание прн экспертизе

1.Sz>rnanski 3 %. An irnprovedIKO

scheme ог digital, phase„Rocked Ьир%

"Яес1гоМс епо 1neening, 49т7, v.

49> t4о 589 р. 24 ° 26.