Преобразователь код-фаза

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик (n 658734

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву,,(„г (22) Заявлено 150477(21) 2477016/18-24

Н 03 К 13/20 с присоединением заявки ¹â€” (23) Приоритет—

Государственный комитет

СССР но делам изобретений и открытий

Опубликовано 250479. Бюллетень ¹ 15

Дата опубликования описания 2804.79 (53) УДК 881.325 (088 . 8) (72) Авторы изобретения

A.Ê.Êëèìåíêo, Ю.A.Сергеев и В ° A.Емельянов (71) Заявитель (5 4 ) ПРЕОБ Р АЗОВА 1 ЕЛЬ КОД-ФАЗ А

Изобретение относится к области вычислительной техники и может найти применение в системах программного управления металлорежущими станками.

Известны двухкаскадные преобразователи кода в фазу, предназначенные для использования в,следящих приво— дах с высокочастотными фазовыми датчиками обратной связи (1).

Наиболее близким по техническому решению к предлагаемому являетая преобразователь код-фаза, содержащий арифметический блок, блок сравнения и йоследовательно соединенные генератор импульсов и делители частоты, тэ первый вход блока сравнения соединен с первым выходом первого делителя частоты (2).

Недостатком известного устройства является его сложность, ограниченность диапазона изменения фазы и низкая помехоустойчивость.

Целью изобретения является упрощение и повышение помехоустойчивости устройства. Это достигается тем, что 5 преобразователь содержит комбинационный сумматор и триггер, первый вход которого соединен со вторым выходом первого делителя частоты, второй вход — с выходом блока сравнения, а

2 выход — с первым входом комбинационного сумматора, второй вход которого соединен с выходом второго делителя .частоты, третий вход комбинационного сумматора соединен с выходами. группы старших разрядов арифметического блока, выхода группы младших разрядов, которого соединены со вторым входом блока сравнения °

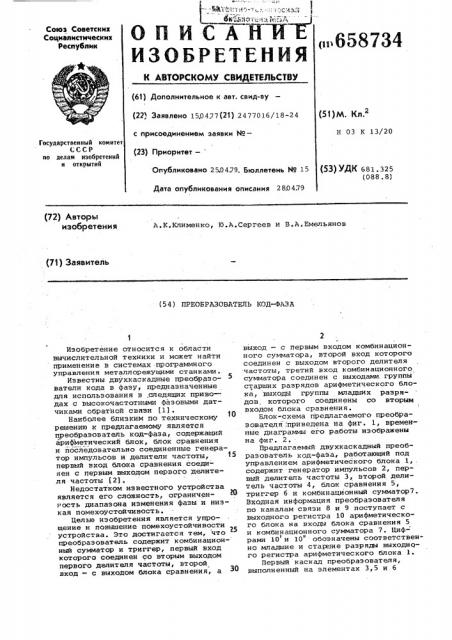

Блок-схема предлагаемого преобразователя приведена на фиг. 1, временные диаграммы его работы изображены на фиг. 2.

Предлагаемый двухкаскадный преобразователь код-фаза, работающий под управлением арифметического блока 1,. содержит генератор импульсов 2, первый делитель частоты 3, второй делитель частоты 4, блок сравнения 5, триггер б и комбинационный сумматор7.

Входная информация преобразователя по каналам связи 8 и 9 поступает с выходного регистра 10 арифметического блока на входы блока сравнения 5 и комбинационного сумматора 7. Цифрами 10 и 10 обозначены соответственно младшие и старшие разряды выходнрго регистра арифметического блока 1.

Первый каскад преобразователя, выполненный на элементах 3,5 и б

658 /34 (2) m"" гас м

М= 3+ëÓ" 26 — + — .— .

О n" л (4) Формула изобретения осуществляет преобразование кода, поступающего по каналу связи Я,в длительность импульсов на выходе триггера 6.

В качестве блока сравнения 5 могут быть использованы различные логические схемы, например комбинационный суммат ор .

Частота выходных импульсов триггера равна импульсам на выходе делителя 3, а длительность их определяется по выражению: 10

rC T (1) где Т вЂ” период следования выход-. ных импульсов делителя 3;

m — величина кода, следующего(5 по каналу связи 8;

n — объем регистра 10 и блока сравнения 5, равные коэффициенту деления делителя частоты 3.

Второй каскад преобРазователя, вы-20 пслненный на элементах 2,4 и 7, осуществляет преобразование кода, следующего по каналу связи 9, с учетом сигнала на выходе триггера б в сдвиг фаз между выходными импульсами сумматора 7 и первого делителя частоты 3 „

При состоянии триггера 0, указанный сдвиг фаз огределяется по выражению: =2л, о ц где m" — код в канале связи 9;

n — объем регистра 10 и сумматора 7 равный коэффициенту деления делителя частоты 4.

При переходе триггера в состояние 1 сдвиг фаэ получит приращение

2 )Г равное — -„- рад. и

Поскольку время нахождения триrгера в состоянии 1 определяется выражением С, то среднее за период

Т значение приращения сдвига фаз между последовательностями высокочастотных импульсов, обусловленное работой первого каскада преобразователя определяется как и в устройстве-прототипе, 5 по выражению:

ЬУ = — - — °

2К (3)

И

Выражение для среднего значения сдвига фаз между сигналами на выходах 11 и 12 преобразователя с учетом приведенных соотношений получает вид:

Иэ выражения видно, что в предлага-. емом двухкаскадном преобразователе объем одновременно вводимой и преобразуемой информации примерно в п раз больше, чем в известных устройствах. 60

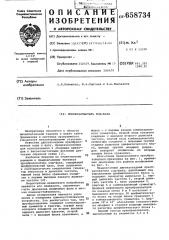

На фиг. 2, иллюстрирующей работу двухкаскадногс преобразователя, изображены:

a — временная диаграмма состояния делителя 3; б5 б — величина кода в каIIïnå связи 8; в — временная диагсамма состояния блока сравнения 5, в качестве которого используется сумматор;

r — сигнал на выходе триггера 6; д — величина кода в канале связи 9; е — временная диаграмма фазового сдвига между выходными сигналами преобразователя (выходй 11 и 12) .

Работа первого каскада (см. фиг. 2, а, б, в, r) происходит следующим образом.

В процессе работы делитель 3 периодически переполняется и возвращается в исходное состояние. В эти моменты на выходе делителя возникает импульс, устанавливающий триггер б в состояние 0 (см. фиг. 2, r) . .!а входы сумматора, используемого в качестве блока сравнения 5, одновременно подаются сигналы с ячеек делителя 3 и с регистра 10(, арифметического блока 1, поэтому он переполняется раньше делителя и устанавливает триггер в состояние 1 .

Величина опережения C, пропорциональна значению кода, поступающего по каналу связи 8 и содержащегося в сумматоре в момент переполнения делителя.

Фазовый сдвиг между выходными сигналами двухкаскадного пресбразоват ел я ймеет вид пр ямоу гол ьных импульсов (см. фиг. 2, а), скважность которых определяется содержимым младших разрядов,а уровень — содержимым старших разрядов-выходного регистра 10 арифметического блока 1. Среднее значение указанного сдвига фаз за период следования импульсов Т определяется по выражению (4) .

В сравнении с известными устройствами предлагаемый двухкаскадный преобразователь код-фаза обладает следующими преимуществаж: улучшенными техническими характеристиками, в том числе увеличенным объемом преобразуемой информации; уменьшением количества элементов преобразователя и связей между элементами; высокой помехоустойчивостью. Выходная информация однозначно соответствует входной, что автоматически устанавливается как при включении устройства, так и при наличии сбоев при наличии помех.

Преобразователь код-фаза, содержащий арифметический блок, блок сравнения и последовательно соединенные генератор импульсов, делители частоты, первый вход блока сравнения соеди нен с первым выходом первого делителя частоты, отличающийся тем, что, с целью упрощения устройст658734

Фиг.!

1 °

t тг

Составитель И. Аршавский

Редактор Н. Веселкина Техред О.Андрейко Корректор О. Ковинская

Тир аж 1059 Подписное

ЦЛИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 2077/54

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 ва и повышения помехоустойчивости, он содержит к омби н аци он ный суммат ор и триггер, первый вход которого соединен со вторым выходом первого делителя частоты, второй вход — с выходом блока сравнения, а выход— с первым входом комбинационного сумматора, второй вход которого соединен с выходом второго делителя частоты, третий вход комбинационного сумматора соединен с выходами группы старших разрядов арифметического блока, выходы группы младших разрядов

1 которого соединены со вторым входом блока сравнения.

Источники информации, принятые во внимание при экспертизе

5 1. Авторское свидетельство СССР

9 253542, кл. G 05 В 19/02, 1970.

2,. Авторское свидетельство по заявке Р 2156100/18-24, кл. G 05 В 19/18, 1975.