Преобразователь биполярного кода в однополярный

Иллюстрации

Показать всеРеферат

Союз Советскиз

Социалистических

Республик

Н 03 К 13!24 (61) Дополнительное к авт. cs a-ву

{22) Заявлено 30.12.76 (2! ) 2439499/18 — 21 с присоединением заявки № (23) Приоритет

Гкударствеинвй иматет ссср па делан наоаратений и атнрытнй

ОпублВковаио 25.04.79. Бяэллетеиь М 15 (53) УЙК 681.325, .63 (088.8) Дата опубликования описания 25.04.79 (72) Автори изобретения

Н.Н.Васерин, И.Н.Крылов, ЕА.Ноткин и В.И.Терехов

Pf Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ БИПОЛЯРНОГО КОДА

Е ОДНОПОЛЯРН 1й

Изобретение относится к импульсной технике и может быть применено в устройствах, использующих биполярный трехуровневый код для пе. редачи информации.

Известны преобразователи биполярного кода

5 в однополярный, содержащие блоки выборки и управления fт).

Недостатком этого устройства является невозмо>кпость получения синхроимпульсов.

Известны преобразователи биполярного кода в однополярный, содержащие делители, входные и выходные шины (2).

Недостатком этого устройства является низкая надежность из-за появления несинфазных импульс ных помех. т5

Целью изобретения является повышение надежности и расширение функциональных возможностей.

Для этого в преобразователь биполярного кода в однополярный, содержащий резистивные делители, соединенные с входными шинами, и выходные шины, введены усилители-ограничители, инверторы, элемент "Исключающее ИЛИ" и

ЛК-триггеры, причем выходы резистивных делителей соединены с входами соответствующих усилителей-ограннчителей, выход первого иэ которых подключен к первому входу элемента

"Исключающее ИЛИ", второй вход которого соединен с выходом другого усилителя-ограничителя, К вЂ” входом первого gK-триггера и через первый ицвертор — с > -входом этого же триггера, выход которого подключен к первой выходной шине, при этом выход элемента Исключающее

ИЛИ" соединен с Д вЂ” входами второго и третьего

".>К-триггеров и через второй инвертор — с К-входами этих же триггеров, счетные входы которых подключены к шине опорных сигналов, кроме того прямой и инверсный выходы второго JKтриггера соединены соответственно с другими

3-и К-входами третьего JK-триггера, прямой выход которого подключен к другой выходной шине, а инверсный — к счетному входу первого

J К- триггера.

Усилитель-ограничитель может быть выполнен на двух транзисторах одной проводимости, причем база первого транзистора соединена с входом

658735 усилителя-ограничителя, а эмиттер через первый резистор — с базой второго транзистора, эмиттер которого подключен к общей шине, а коллектор — к выходу усилителя-ограничителя и через второй резистор-к шине питания и коллектору з первого транзистора.

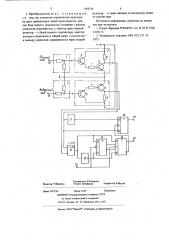

На чертеже приведена принципиальная электрическая схема устройства.

Устройство содержит резистивные делители 1,2, 1О усилители-ограничители 3 и 4, содержащие транзисторы 5, 6 и резисторы 7, 8, инверторы 9 и 10, элемент "Исключавшее ИЛИ" 11, 3К-триггеры 12, 13 и 14, входные шины (входы) 15 и 16 и выходные шины (выходы) 17 и 18.

Устройство работает следующим образом.

На входы 15 и 16 преобразователя одновременно поступают соответственно прямой и инверсный биполярные коды. Через резистивные делители 1 и 2 обе импульсные последовательности поступают на входы усилителей-ограничителей 3 и 4, которые обеспечивают усиление импульсов только положительной полярности.

Сигнал с входа усилителя-ограничителя 3 или 4 поступает иа базу транзистора 5. Нагрузкой в эмиттерной цени этого транзистора служат резистор 7 и переход база-эмиттер транзистора 6.

Транзистор 6 включен по схеме с общим эмиттером. Нагрузкой транзистора 6 служит резистор 8.

С коллектора транзистора 6 снимается выходной сигнал усилителя-ограничителя с уровнями логического "О" и логической "1", необходимыми для работы логических элементов.

На выходе усилителя-ограничителя 3 формируются отрицательные импульсы, соответствующие единицам кода, а на выходе усилителя-ограничителя — нулям кода. На выходе усилителей-ограничителей 3 и 4 могут передаваться импульсы помех. Сигналы с выходов усилителей-ограничи- 40 телей 3 и 4 подаютея на входы элемента "Исключ чающее ИЛИ 11, который обеспечивает сумми- °, рование поступающих на его входы импульсных последовательностей, причем на выходе формируется последовательность импульсов, в которой исключены совпадающие значения входных сигналов, т.е, элемент "Исключающее ИЛИ" 11 обеспечивает подавление синфазных помех.

Сигнал на выходе элемента ."Исключающее

ИЛИ" 11 запоминается JK-триггером 12 на пе-.

50 риод следования опорных импульсов. Состояние

3 К-триггера 14 будет определяться совпадением сигналов, поступающих с выходов элемента "Исключающее ИЛИ" 1.1 и JK-триггера i?. При этом, если совпадения не произошло (в случае появления несинфазной импульсной помехи длительностью меньше То), то J К-триггер 14 останется в преж- нем состоянии, т.е. на выходе 18 преобразователя формируется последовательность синхроимлульсов, причем число синхроимпульсов точно соответствует числу импульсов полезной информации во входном биполярном коде. Период следования опорных импульсов необходимо выбирать меньше половины длительности импульса входного кода с тем, чтобы иметь возможность отличить по длительности импульс кода от импульсной помехи. Для формирования однополярного кода сигнал с выхода усилителя-ограничителя 3 подается для управления JK-триггером

13. На тактовый вход этого триггера поступают синхроимпульсы с инверсного выхода 3K-триггера 14. В связи с тем, что, как показано выше, при получении синхроимпульсов обеспечена защита от импульсных помех, JK-триггер 13 может изменить свое состояние только такое число раэ, сколько импульсов полезной информации имеется во входном биполярном коде. Следовательно, на выходе 17 преобразователя формируется однополярный последовательный код, свободный от помех.

Изобретение обеспечивает надежную защиту устройства от импульсных помех как синфазных, так и несинфазных.

Преобразователь питается от одного источника питания, что повышает его надежность.

Формула изобретения

1. Преобразователь биполярного кода в однополярный, содержащий резистивные делители, соединенные с входными шинами, и выходные шины, отличающийся тем,что,сцелью повышения надежности и расширения функциональных возможностей, введены усилители-ограничители, инверторы, элемент "Исключающее

ИЛИ" и "JK-триггеры, причем выходы резистивных делителей соединены с входами еоответствующих усилителей-ограничителей, выход первого из которых подключен к первому входу элемента "Исключающее ИЛИ", второй вход которого соединен с выходом другого усилителя-ограничи-, теля, К-входом первого ЗК-триггера и через первый инвертор — с 3-входом этого же триггера, выход которого подключен к первой выходной шине, при этом выход элемента "Исключающее ИЛИ" соединен с J-входами второго и третьего J K-триггеров, и через второй инвертор — с К-входами этих же триггеров, с ктные входы которых подключены к шине опорных сигналов, кроме того. прямой и инверсный выходы второго J K-триггера соединены соответственно с другими У- и К-вхо- дами третьего JK-триггера, прямой выход которого подключен к другой выходной шине, а инверсный — к счетному входу первого JK-триггера.

658735

rr, ко

Инд ка

Составитель Л.Захарова

Техред Н.Бабурка Корректор И.Муска

Редактор Т.Иванова

Заказ 2077/54 Тираж 1059 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д.4/5

Филиал ППП Патент, г,ужгород, ул.Проектная,4

2. Преобразователь по п.1, о т л и ч а ю щ и йс я тем, что усилитель-ограничитель выполнен на двух транзисторах одной проводимости, причем база первого транзистора соединена с входом усилителя-ограничителя, а эмиттер через первый резистор — с базой второго транзистора, эмиттер которого подключен к общей шине, а коллекторк выходу усилителя-ограничителя и через второй резистор — к шине питания и коллектору первого транзистора.

Источники информации, принятые во внимание при экспертизе

1. Патент Франции У2068937, кл. Н 03 К 5/00, 13.08. 71.

2. Техническое описание 6ФЗ. 055.172 33, 1975.