Устройство для автоматического определения канала с минимальным уровнем напряжения

Иллюстрации

Показать всеРеферат

l ф хг

Союз Советских

Социалистических

Республик пт658 751

ОП ИСАНИЕ"

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6! ) Дополнительное к авт. свид-ву— (22) Заявлено 11 07.77 (21) 2508125/18-09 с присоединением заявки №вЂ” (23) Г!риоритет—

Опубликовано 25.04.79. Бюллетень № 15

Дата опубликования описания 26. ОФ. 7У (51) М. Кл.е

Н 04 В 3/46

Гооударствеинъа комитет

СССР по делам изооретенмй и открытий (53) УДК 62!.-395..664 (088.8) (72) Авторы изобретени:

H. А. Дрязгов, А. М. Староверов и П. Т. Толмачев (71) Заявитель (54) УСТРО1!СТВО ДЛЯ АВТОМАТИЧЕСКОГО ОПРЕДЕЛЕНИЯ

КАНАЛА С МИНИМАЛЪНЪ|М УРОВНЕМ НАПРЯЖЕНИЯ

Изобретение относится к связи и может использоваться в устройствах анализа частотно — разнесенных каналов систем связи.

Известно устройство для автоматического определения канала с минимальным уровнем напряжения, содержащее блок управления, первые выходы которого подключены к входам коммутатора, а также запоминающий блок j l i

Однако известное устройство имеет невысокую точность определения канала.

Цель изобретения — повышение точности определения.

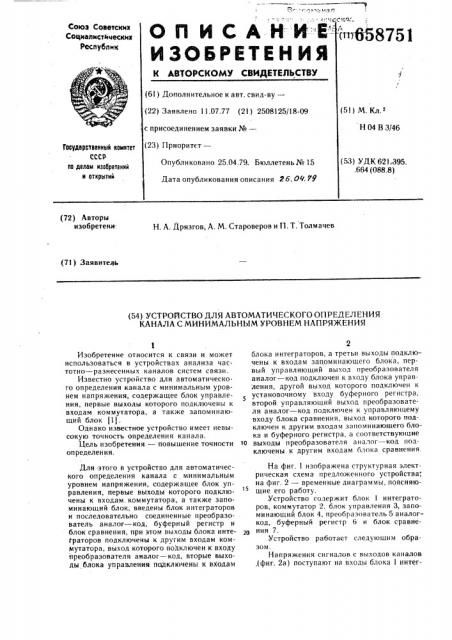

Для этого в устройство для автоматического определения канала с минимальным уровнем напряжения, содержащее блок управления, первые выходы которого подключены к входам. коммутатора, а также запоминающий блок, введены блок интеграторов и последовательно соединенные преобразователь аналог †к, буферный регистр и блок сравнения, при этом выходы блока интеГраторов подключены к другим входам комМутатора, выход которого подключен к входу преобразователя аналог — код, вторые выходы блока управления псдключены к входам

2 блока интеграторов, а третьи выходы подключены к входам запоминающего блока, первый управляющий выход преобразователя аналог — код подключен к входу блока управ ления, другой выход которого подключен к установочному входу буферного регистра, второй управляющий выход преобразователя аналог — код подключен к управляющему входу блока сравнения. выход которого подключен к другим входам запоминающего блока и буферного регистра, а соответствующие тв выходы преобразователя аналог — код подключены к другим входам блока сравнения.

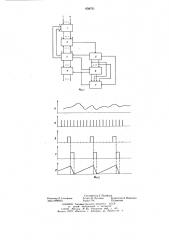

На фиг. 1 изображена структурная электрическая схема предложенного устройства, на фиг. 2 — временные диаграммы, поясняющие его работу.

Устройство содержит блок i интеграторов, коммутатор 2, блок управления 3, запоминающий блок 4, преобразователь 5 аналогкод, буферный регистр 6 и блок сравнен ния 7.

Устройство работает следующим образом.

Напряжения сигналов с выходов каналов .(фиг. 2а) поступают на входы блока 1 интег65875!

3 раторов, в котором осуществляется усреднение % ровней и ни ря жеHHH за интервалы Bpc меии. определяемые блоком управления 3.

Усредненные ио напряжениям сигналы с выхо дов блока 1 интеграторов (фиг 2д) поступают на аналоговые ключи коммутатора 2.

Блок управления 3 последовательно вырабатывает п импульсов опроса (фиг. 2в) и и импульсов разряда интеграторов (фи;. 2г), а также (n+1) — и импульс конца цикла опроса. Кроме того, блок управлении 3 вырабатывает код номера опрашиваемого канала, поступающий на входы записи запоминающего блока 4.

В исходном состоянии ключи коммутато ра 2 закрыты, а в буферный регистр 6 записа. но максимальное число. Импульс опроса ! — го канала открывает первый ключ коммутатора 2, и усредненный по напряжению сиг. нал канала поступает на вход преобразова теля 5 аналог — код. Код измеренного сигна ла поступает на входы записи буферного ре гистра 6, а также на входы блока сравнения

7, на другие входы которого поступает код числа, содержащегося в буферном регистре 6, По сигналу разрен ения, поступающему с преобразователя 5 аналог †к на блок сравнения 7, последний вырабатывает импульс, в случае, если число, поступающее с выходов преобразователя, меньше числа, содержащегося в буферном регистре 6. Этим импульсом код меньшего числа переписывается в буферный регистр 6, а в запоминающий блок 4 переписывается код номера канала, при этом предыдущая запись стирается.

По окончании цикла измерения преобразователь 5 аналог — код формирует сигнал переключения каналов (фиг. 2б), поступающий на блок управления 3. Блок управления 3 вырабатывает импульс опроса второго канала.

Блок управления 3 вырабатывает импульс опроса второго канала и импульс разряда интегратора первого канала. Рассмотренный цикл измерения повторяется и для остальных каналов.

После и опросов в запоминающем блоке 4 будет записан номер с минимальным напря4 жеиием, уровень которого записан в буферном регистре 6. Затем блок управления 3 вырабатывает (и+1) — и нмпульс. конца цикла опроса, устанавливающий буферный регистр

6 в исходное. состояние.

Таким образом, предложенное устройство позволяет повысить точность выбора канала за счет усреднения входных напряжений и устранения неоднозначности выбора канала с минимальным напряжением помех при близких по уровням или изменяющихся в процес ó се измерений напряжениях каналов.

Формула изобретения

Устройство для автоматического опреде пения канала с минимальным уровнем напряжения, содержащее блок управления, первые выходы которого подключены к входам коммутатора, а также запоминающий блок, отлича ощееся тем, что, с цельк) повышения точ>@ ности определения, введены блок интеграторов и последовательно соединенные преобразователь аналог — код, буферный регистр и блок сравнения, при этом выходы блока интеграторов подключены к другим входам коммутатора, выход которого подключен к входу и преобразователя аналог — код, вторые выходы блока управления подключены к входам блока интеграторов, а третьи выходы подключены к входам запоминающего блока, первый управляющий выход преобразователя аналог †к подключен к входу блока управления, другой выход которого подключен к установочнему входу буферного регистра, второй управляющий выход Hp îáðàçîBàòåëÿ аналог — код подключен к управляющему входу блока сравнения, выход которого иодклюзз чен к другим входам запоминающего блока и буферного регистра, а соответствующие выходы преобразователя аналог — код подключены к другим входам блока сравнения.

Источники информации, принятые во внимание ири экспертизе

1 Авторское свидетельство СССР № 325698, кл. 1-1 03 К 5/18, 1970.

Риг. t

Составитель Е. Погиблов

Редактор Л. Гельфчаи Техред О. Луговая Корректор А. Власенко

Заказ 2080/55 Тираж 774 Подписное

ПНИИПИ Государственного комитета СССР во делам изобретений и открытий

I! 3035. Мо«ква, Ж -35. Раушская наб., д. 4/5

Филиал ППП <Патентэ, г. Ужгород, ул. Г!роектиан, 4