Преобразователь двоичного кода в биполярный код

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистимесхих

Республик

Оп ИКАНИЕ 658761

ИЗОБРЕТЕНИЯ (61) Дополнительное к авт. спид-ву— (22) Заявлено 15.07.77 (21) 2508064/18-09 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 25.04.79. Бюллетень № 15 (51) М. Кл.

Н 04 1. 3/02

Гюсударстааииый комитет

СССР в делам иэоаратений и открытий (53) УДК 621 394.. 14 (088.8) Дата опубликования описания 28.04 . f2 (72) Автор изобретения

В. И. Галчихнн (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В БИПОЛЯРНЫЙ

КОД

Изобретение относится к радиотехнике и может использоваться в аппаратуре линейных трактов цифровых систем передачи по кабельным линиям.

Известен преобразователь двоичного кода в биполярный код, содержащий соединеные по одному из входов элементы ИЛИ н И, к другим входам которого подключены выходы регистра сдвига, а выход элемента И через элемент ИЛИ подключен к входу регистра сдвига, а также коммутатор, выходы которого подключены к соответствующим входам распределителя полярности единиц (11.

Однако известный преобразователь не обладает достаточным быстродействием н надежностью работы.

Цель изобретения — повышение быстродействия и надежности работы преобразователя.

Для этого в преобразователь двоичного кода в биполярный код, содержащий объединенные по одному из входов элементы ИЛИ и И, к другим входам которого подключены выходы регистра сдвига, а выход элемента И через элемент ИЛИ подключен к входу регистра сдвига, а также коммутатор, выходы которого подключены к соответствующим входам распределителя полярности единиц, введены сумматор по модулю два и два блока задержки, при этом выходы регистра сдвига подключены к счетным входам сумматора по модулю два, к раздельному входу которого подключен выход элемента И, который через первый блок задержки подключен к счетным входам коммутатора, а выход сумматора по модулю два непосредственно и через второй блок задержки подключен к соответствующим входам распределителя полярности единиц.

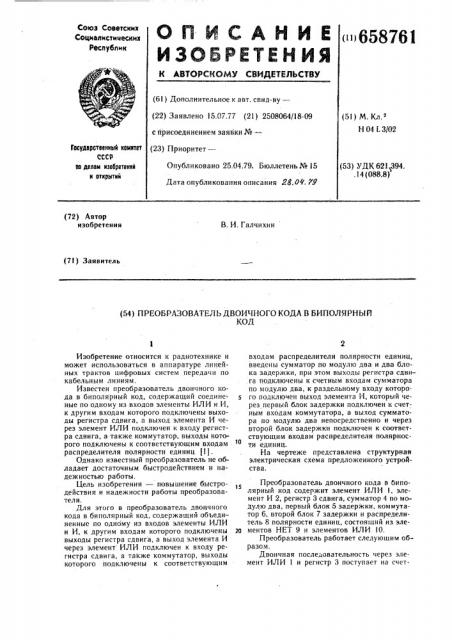

На чертеже представлена структурная электрическая схема предложенного устройства.

Преобразователь двоичного кода в биполярный код содержит элемент ИЛИ 1, элемент И 2, регистр 3 сдвига, сумматор 4 по модулю два, первый блок 5 задержки, коммутатор 6, второй блок 7 задержки и распределитель 8 полярности единиц, состоящий из элерв ментов HET 9 и элементов ИЛИ 10.

Преобразователь работает следующим образом.

Двоичная последовательность через элемент ИЛИ 1 и регистр 3 поступает на счет658761

„- « нь.и вход сумматора 4, где производится сложение двоичных символов по модулю два. В случае пояВления В дВОичной последоВательности (N+1) -- или более нулей подряд на

Выходе элемента И 2 форми13уется единица, которая, с одной стороны, через элемент ИЛИ запись3вается г, двоичную последовател3ность вместо (N+1) — -го нуля, с другой стороны, подается на раздельный вход сумматора 4 для установа (илн подтверждения) определенного его состояния, соответствующего результат2l суммн120вания, а также после задержки на тактовый интарвал подается на первый блок 5, на с четный вход коммутатора

6, формирующего управляющее напряжение.

Полученная в результате сложения по мо дулю два двоичная последовательность с выхода сумматора 4 подается на входь3 распре делителя 8, Кроме того, TB же последоВатель. ность после задержки на тактовый интервал иа ВтОрОм блОке ? подаетсЯ на другие ВхОды распределителя 8, коммутируемого попеременно управляющими напряжениями с выходов коммутатора 6. С помощью распределителя 8 в заВисимости От сОстОяния KGMÌ THтора 6 осуществляешься формирование двух последовательностей с взаимным чередованием единиц.

Формула изобретения

Применение новых функциональных узлов и связей обеспечивает повышение скорости и надежности работы преабразователя кодов, а также сущестВениое уп13ощение его функциональной схемы.

Преооразователь двоичного кода в биполярный код, срдержащий объединенные по одному из входов элементы ИЛИ и И, к другим входам которого подключены выходы регистра сдвига, а выход элемента И через элемент ИЛИ подключен к входу регистра сдвига, а также коммутатор, выходы которого подключены к соответствующим входам распределителя полярности единиц, отличаю чийся тем, что; с целью повышения быстродействия и надежности работы преобразователя, введены сумматор по модулю два и два блока задержки, при этом выходы регистра сдвига подключены к счетным входам сумматора по модулю два, к раздельному входу которого подключен выход элемента И, который через первый блок задержки подключен к счетным входам коммутатора, а выход сумматора по модулю два непосредственно и через второй блок задержки подключен к соответствующим входам распределителя полярНосТН- единиц.

Источники информации, принятые во внимание при экспертизе

1. Патент ФРГ № 2480?60, кл. Н 03 К 13/24, 19?3.

Составитель Г. Любимова

Редактор Л. Гельфман Техред О. Луговаи Корректор М. Пожо

3а кав 2080/55 Тираж 774 Подписное

ПНИИПИ Государственного комитета СССР по делам изобретеHHH и открытий

413035, Москва, Ж-35, Раусвскав наб. д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектиаи. 4