Устройство синхронизации

Иллюстрации

Показать всеРеферат

ОП И АНИЕ"

ИЗОБРЕТЕН ИЯ -(",,;-658762

Союз Советских

Социалистических

Респу6пик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 06.05.7? (21) 2483054(I 8-09 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 25.04.79 Бюллетень № 15

Дата опубликования описания Я6.04 . Р5 (5 I ) М. Кл, Н 04 1. 7/02

Государственный комитет

СССР оо делам нзооретеннй и открытий (53) УДК 621.394. .662.2 (088.8) (72 } Авторы изобретения

Е. А. Голубев, В. С. Барсуков и В. В. Машкин (7l ) Заявитель (54) УСТРОИСТВО СИНХРОНИЗАЦИИ

Изобретение относится к передаче данных у может использоваться в различных радиотехнических устройствах.

Известно устройство синхронизации, содержашее последовательно соединенные блок управления, делитель частоты, блок выделения зоны и первый усилитель, а также второй усреднитель, триггер, два ключа, фазовый дискриминатор и формирователь фронтов, выход которого подключен к другому входу блока выделения зоны 11).

Однако в известном устройстве при кратковременных пропаданиях сигнала могут появиться ошибки синхронизации типа

«вставки» и «выпадения» за счет безпорядочного переключения шага коррекции под действием шумов, что снижает помехоустойчивость устройства.

Цель изобретения — повышение помехоустойчивости.

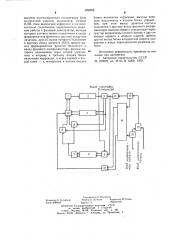

Для этого в устройство синхронизации, содержашее последовательно соединенные блок управления, делитель частоты, блок выделения зоны и первый усреднитель, а также второй усреднитель, триггер, два клю2 ча фазовый дискриминатор и формирователь фронтов, выход которого подключен к другому входу блока выделения зоны, введены последовательно соединенные блок когерентной свертки, анализатор, элемент ИЛИ, блок включения коррекции. и последовательно соединенные переключатель режимов работы и фазовый демодулятор, выходы которого соответственно подключены к входу формирователя фронтов и к другому входу анализатора, другой выход которого подключен к другому входу элемента ИЛИ, причем выход формирователя фронтов подключен к входу фазового дискриминатора, выходы которого.подключены через второй усреднитель к второму и третьему входам блока включения коррекции, а через первый и второй ключ — к четвертому и пятому входам блока включения коррекции, выходы которого подключены к входам блока управления, при этом выход делителя частоты подключен к другому входу фазового дискри2О мннатора, выходы первого усреднителя через триггер подключены соответственно к другим входам первого и второго ключей, причем другой выход блока когерентной свертки подключен к выходу переключателя режимов работы, На чертеже изобра>кена структурная электрическая схема предложенного устройства, Устройство содержит блок управления I, делитель частоты 2, фазовый дискриминатор 3, усреднитель 4, блок 5 выделения зоны, усреднитель 6, триггер 7, ключи 8 и 9, блок 10 включения коррекции формирователь фронтов Il, элемент ИЛИ 12, фазовый демодулятор 13, анализатор 14, переключатель 15 и блок 16 когерентной сверт.ки.

Устройство работает следующим образом, Сигналы с выхода делителя частоты 2 и выхода формирователя фронтов 11 сравниваются по фазе в фазовом дискриминаторе 3. В случае расхождения фаз этих сигналов импульсы, характеризующие отставание или опережение фаз, поступают на входы усреднителя 4 (например, реверсивный счетчик) .

Импульсы с выхода усреднителя 4 являются корректирующими и поступают через блок 10 включения коррекции в блок управления 1 подстройкой фазы, куда также могут поступать импульсы коррекции непосредственно с фазового дискриминатора 3 через ключи 8, 9 и блок 10 включения коррекции.

Блок 10 включения коррекции реализует два шага коррекции. Коррекция фазы производится на каждом периоде низкочастотного сигнала с помощью фазового дискриминатора 3, триггера 7 и ключей 8 и 9 при большом шаге и несколько периодов при управлении с усреднителя 4 при малом шаге коррекции. Введение переменного шага коррекции позволяет быстро входить в синхронизм при наличии хорошего сигнала. Блок 5 без элемента ИЛИ 12 и анализатора 14 при наличии шумов в отсутствии сигнала на входе фазового дискриминатора 3 будет переключать систему коррекции случайным образом с одного шага коррекции на другой, что будет уводить фазу тактовых импульсов.

Выбор нужного шага коррекции, т. е. переключение системы из режима вхождения в синхронизм в режим поддержания синхронизма, осуществляется на основе анализа в блоке 5 выделения зоны расхождения фазы взаимного поло>кения импульсов, полученных из. фронтов сигнала с выхода фазового демодулятора 13 в формирователе фронтов 11 входного сигнала и опорного напряжения с выхода делителя частоты 2. Если импульсы, полученные из фронтов сигнала, находятся вблизи фронтов меандра опорного напря>кения, то усреднитель 6 (например, реверсивный счетчик) опрокидывает триггер 7 в нулевое состояние, и ключи 8 и 9 заперты. Коррекционные импульсы в блок управления I подстройкой фазы поступают с выхода усреднителя 4. Если импульсы, полученные из фронтов сигнала, нахо5$

Форл ула изобретения

Устройство синхронизации, содержащее последовательно соединенные блок управления, делитель частоты, блок выделения зоны и первый усредпитель, а также второи усреднитель, триггер, два ключа, фазовыи дискриминатор и формирователь фронтов. выход которого подключен к другому входу блока выделения зоны, отличшо цееся тем, что, с целью повыпцнпи помехоустойчивости, 4 дятся вблизи середины полупериода опорного напря>кения, то усреднитель 6 переводит триггер 7 в единичное состояние. Ключи

8 и 9 открываются, и коррекционные импульсы в блок уяравления 1 подстройкой фазы поступают с выхода фазового дискри м инатора 3. Элемент ИЛИ 12 исключает вообще какую-либо коррекцию при отсутствии полезного сигнала. Отсутствие полезного сигнала оценивает анализатор !4 в зависимости от выбранного режима работы системы. 6 Таким образом, при плохом качестве сигнала система коррекции фазы выключается, и фаза тактовых импульсов не изменится до тех пор, пока качество сигнала не достигнет удовлетворительного уровня. Допустимое время пропадания сигнала, когда не появляются ошибки синхронизации, определяется стабильностью задающих генераторов на передающем и приемном концах линии связи. При появлении сигнала большой шаг коррекции включится лишь только тогда, щ когда расфазировка сигнала будет больше определенного уровня. Этот режим обеспечивает наибольшую помехоустойчивость приема при наличии флуктуационного шума и замирании сигнала.

2$

Включение системы коррекции осуществляется через элемент ИЛИ 12 анализатором

14.

Блок 16 когерентной свертки сигнала осуществляет приведение многочастотного фазоманипулированного сигнала к единой частоте и фазе и его свертку в одночастотный сигнал, при этом s блоке формируется напряжение, величина которого связана с качеством обрабатываемого сигнала. Величина этого напряжения вычисляется в каскаде додетекторной оценки качества сигнала анализатора !4. При достижении определенной величины вырабатывается импульс. включающий систему коррекции.

Использование новых элементов-блока включения коррекции, каскадов оценки качества сигнала, блока когерен1 ной свертки сигнала и фазового детектора выгодно отличает предложенное устройство от известного, так как уменьшается вероятность появления ошибок синхронизации типа

«вставки» и «вьц|адеппя», повышается по4«мехоустойчивость и расширяется сфера lipHменения устройства коррекции фазы.

Выяви птпкптоЯых

Составитель Е. Погиблов

Редактор Л. Гельфман Техред О. Луговая Корректор М. Пожо

Заказ 2080/55 Тираж 774 Подписное

LIH HH1lH Государственного комитета СССР по делам изобретений и открытий

113035. Москва, Ж-35, Раушская иаб., д. 4/5

Филиал ППП «Патент». г. Ужгород, ул. Проектная, 4 введены последовательно соединенные блок когерентной свертки, анализатор, элемент

ИЛИ, блок включения коррекции и последовательно соединенные переключатель режимов работы и фазовый демодулятор, выходы которого соответственно подключены к входу формирователя фронтов и другому входу анализатора, другой выход которого подключен к другому входу элемента ИЛИ, причем выход формирователя фронтов подключен к входу фазового дискриминатора, выходы которого подключены через второй усреднитель к второму и третьему входам блока включения коррекции, а через первый и второй ключ — к четвертому и пятому входам блока включения коррекции, выходы кото-. рого подключены к входам блока управления, при этом выход делителя частоты подключен к другому входу фазового дискриминатора, выходы первого усреднителя через триггер подключены соответственно к другим входам первого и второго ключей, причем другой выход блока когерентной свертки подкл1очен к входу переключателя режимов работы.

Источники информации, принятые во внимание при экспертизе

1. Лвторское свидетельство СССР № 320070, кл. Н 04 В 15/00, 1970.