Устройство циклового фазирования

Иллюстрации

Показать всеРеферат

Союз Советских

Соцмалмстнчесиии

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ »658?65 (6l) Дополнительное к авт. свид-ву— (22) Заявлено 15.07.77 (21) 2508050/18-09 с присоединением заявки №вЂ” (23) Приоритет ——

Опубликовано 25.04.79. Бюллетень№ 15

Дата опубликования описания 26.ОФ. РУ (51) M. Кл. е

Н 04 17/08

Государстеенный комитет

СССР по делам изобретений н отнрыпий (53) УДК 621.394. .662 (088.8) (72) Авторы изобретения

В. A. Емельянов, В. А, Зеленцов и И. Т. Осташов (71) Заявитель (54) УСТРОЙСТВО ЦИКЛОВОГО ФАЗИРОВАНИЯ

Изобретение относится к технике связи и может использоваться в системах связи, где требуется осуществление циклового фазнрования в условиях интенсивных помех.

Известно устройство циклового фазирования. содержащее дешифратор н последовательно соединенные первый и второй элементы И- — НЕ, счетчик, триггер н третий элемент

И вЂ” НЕ, выход которо; î подключен к другому входу триггера и входу второго элемента

И вЂ” НЕ, на другой вход которого и вход первого элемента И вЂ” HE подан синхроснгнал (1).

Однако данное устройство имеет невысокую точность синхронизации.

11ель изобретения — повышение точности синхронизации.

Для этого в устройство циклового фазирования, содержащее дешифратор и последовательно соединенные первый н второй элементы И вЂ” НЕ, счетчик, триггер и третий элемент

И вЂ” НЕ, выход которого подключен к другому входу триггера и входу второго элемента

И вЂ” НЕ, на другой вход которого и вход первого элемента И вЂ” НЕ подан синхросигнал, введены два элемента ИЛИ и два элемента

И, при этом пеовый выход дешифратора че2 рез последовательно соединенные первый элемент И и первый элемент ИЛИ подключен к другом вход первого элемента И вЂ” НЕ н к другому входу третьего элемента И--НЕ, выход которого подключен к дополнительному входу счетчика, а через последовательно соединенные второй элемент ИЛИ и второй элемент И вЂ” к другому входу первого элемента ИЛИ, причем выход триггера соединен с другим входом первого элемента И, дополнительный выход триггера подключен к другому входу второго элемента И, при этом первый выход дешифратора подключен к другому входу второго элемента ИЛИ.

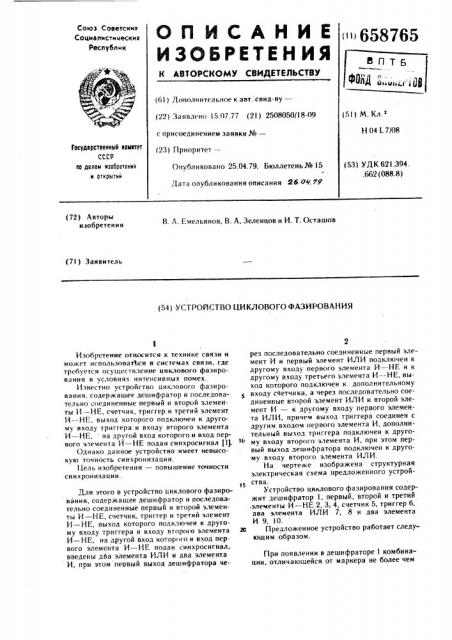

На чертеже изображена структурная электрическая схема предложенного устрой15

Устройство циклового фазирования содержит дешифратор i, первый, второи и третий .элементы И вЂ” HE 2, 3; 4, счетчик 5, триггер 6, два элемента ИЛИ 7, 8 и два элемента

И9, 10.

2с Предложенное устройство работает следующим образом.

При появлении в дешифраторе l комбинации, отличающейся от маркера не более чем е»8765

Формула изобретения

<(И ИИНИ За>(аз 2()8<)(55 Тираж 774 П(>дни(-н<>с

Филиал ППП «П((nнг», г. У>(p<>)(, ул. Пр<>ентнан, в V. 1)ff:f P >1. (f(.<, (if 1 .(. ГО в)>(х<>>(с (>()ывл >(< ) < и и м((у,. (ьс Гяк как в нй (аз(ьноч c()< т()яни и fl()gjf оганлин(>к>н(ий (f<>f< «I(((;(л с три(гера 6 подаетcsf (((I s. ((>(cI(r 11 9, (o >(M((((f < с;и п(н(1>рат»ра 1 проходиг через элемент И 9, ИЛИ 8, И НЕ 4 на выход устр(>((стив. Зтог же импульс с выхода элемента И---НЕ 4 перебрасывает триггер 6, закрывая тем самым элемент

И 9 для прохождения сигнала о наличии маркера и открывая элемент И 10. Устройство переходит из режима поиска маркера режим поддержания синхронизма, что характеризуется прежде всего работой по более грубому порогу дешнфратора 1 (допускается больп(ее число ошибок в маркере).

Импульсы, свидетельствукхщие о поступлении в дешифратор 1 комбинаций, отличающихся от маркера не более, чем в R+p разрядах, (где Ви р выбира(отся в зависимости от структуры маркера, минимального хеммингова расстояния его до любой комбинации такой же длительности в информационной последовательности, характеристик помех) про— ходят через элемент ИЛИ 7, элемент И 10, элемент ИЛИ 8 на вход элемента И вЂ” НЕ 2.

Элемент И--HE 2 выдает сигнал «верно», поступающий на вход триггера 6, устанавливая счетчик 5 в нулевое состояние. Если же дешифратор 1. не обнаружил маркера в этот момент времени, входной импульс проходит че1 ез элемент И вЂ” HE 3 как сигнал «неверно» записывает в счетчик 5 единицу. При поступлении двух подряд сигналов «неверно» счетчик 5 выдает сигнал, поступакпций на вход триггера 6 и перебрасывающий последний в исходное состояние. Таким образом, элемент

И 9 вновь открыт, а элемент И 10 — - закрыт для прохождения импульсов с дешифратора

1. Устройство возвра(пается в исходное состояние и переходит вновь в режим поиска маркера по меньшему порогу. Г1ри использовании предложенного устройства увеличивается вероятность вхождения в цикловой синхронизм в условиях интенсивных помех, когда возможны искажения отдельных элементов маркерной последовательности за счет работы дешифратора 1 в начальный момент при поиске маркера по ненулевому порогу. Уменьшается вероятность сбоя синхронизча, так как при переходе в режим поддержания синхронизма дешифратор 1 работает по более грубому порогу, чем в f(cf÷;(ë(íûff м(>м< ((I .

Возможность такой работы обус (<>(u(на тс м, что устройство в этом рс жиме осуп(ествляет опрос дешифратора 1 на наличие в нем маркера лишь в строго определенные м<>менты времени, когда появление маркера наиболее вероятно.

Кроме того, уменьшение вероятности сбоя синхронизма достигается тем, что репиние о сбое синхронизма и переход в режим поиска маркера принимается лишь при 2--х сбоях подряд. В условиях сильных помех вероятность искажения элементарного символа в маркерной последовательности очень велика, поэтому возможно возникновение числа ошибок, большего, чем порог.

Устройство циклового фазирования, содержащеее дешифратор и последовательно co2<(единенные первый и второй элементы И вЂ” НЕ, счетчик, триггер и третий элемент И вЂ” НЕ, выход которого подключен к другому входу. триггера и входу второго элемента И вЂ” НЕ, на другой вход которого и вход первого эле21 мента И вЂ” НЕ подан синхросигнал, отличаюи4ееся тем, что, с целью повышения точности синхронизации, введены два элемента ИЛИ и два элемента И, при этом первый выход дешифратора через последовательно соединенные первый элемент И и первый элемент зо ИЛИ подключен к другому входу первого элемента И вЂ” НЕ и к другому входу третьего элемента И вЂ” -НЕ, выход которого подклн>чен к дополнительному входу счетчика, а через последовательно соединенные второй элемент ИЛИ и второй элемент И вЂ” к другому входу первого элемента ИЛИ, причем выход . триггера соединен с другим входом первого элемента И, дополнительный выход триггера подключен к другому входу второго элемента И, при этом первый выход дешифратора ((4> подключен к другому входу второго элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1. Шляпоберский В. И. Основы техни(си передачи дискретных сообщений. М., «Связщ

1973. с. 297.