Устройство для декодирования самосинхронизирующихся кодограмм

Иллюстрации

Показать всеРеферат

Союз Советских

Соклеалкс тически х рес убккк (i 11658769 (б1) Дополнительное к авт. свид-ву— (22) Заявлено 06.07,77 (21) 2505б!7/18-09 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.2

Н 04 117/30

Н 03 К 13/04

Гасударстаааама ааматат ссср в делам взабретеааа в втармтав (53) УДК 621 394.14 (088.8) Опубликовано 25.04.79. Бюллетень № 15

Дата опубликования описания gg,gg 7У (72) Автор изобретения

В. Г. Бронов (71) Заявитель (54) УСТРОЙС 1 ВО ДЛЯ ДЕКОДИРОВАНИЯ

САМОСИНХРОНИЗИРУ)О1ЦИХСЯ КОДОГРЛЖМ

Изобретение относится к технике связи. и может использоваться в системах телеуправления или связи.

Известно устройство для декодирования самосинхронизирующихся кодограмм, содержащее последовательно соединенные вход ной переключатель, блок. запрета информз: ционной последовательности и последовательно соединенные блок запрета синхронизирующей последовательности, дешифратор и выходной переключатель, причем один из выходов блока запрета синхронизирующей последовательности подключен к входу счетчика, а другие выходы — к входам первого сумматора по модулю два, кроме того, первый выход блока запретз информационной последовательности подключен к входу второго сумматора по модулю два (1).

Однако известное устройство требует за= траты значительного времени декодирования принятой информации.

Цель изобретения — сокращение времени декодирования принятой информации.

Для этого в устройство для декодирования самосинхронизирующихся кодограмм, со держащее последовательно соединенные входной переключатель, блок запрета инфор. мационной последовательности и последовательно соединенные блок запрета синхронизирующей последовательности, дешифратор н выходной переключатель, причем один из выходов блока запрета синхронизирующей последовательности подключен к входу счетчика, а другие выходы — к входам первого сумматора по модулю два, кроме того, первый выход блока запрета информационной последовательности подключен к входу вто. рого сумматора по модулю двз, дополнительный выход блока запрета информационной последовательности подключен к соответствующему входу первого сумматора по модулю двз, выход которого подключен к соответствующему входу входного переключателя, к управляющему входу которого и к управляющему входу дешифрзторз подключен выход счетчика, причем соответствующие входы второго сумматора ио модулю два объединены с соответствующими входа20 ми первого сумматора ио модулю двз, выход второго сумматора ио модулю двз подключен к другому Bxo;I) выходного переключателя, а второй выход блокз эзиретз информационной иоследоизтельнисти иодклю658769

<формула изобретения

19

1$

so чен к входу блока запрета синхронизирующей последовательности.

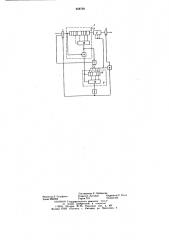

kka чертеже представлена структурная электрическая схема предложенного устройства.

Устройство для декодирования самосинхронизирующихся кодограмм содержит входной переключатель 1, блок 2 запрета информационной последовательности, блок 3 запрета синхронизирующей последовательности, дешифратор 4, выходной переключатель

5, счетчик 6, первый сумматор 7 по модулю два и второй сумматор 8 по модулю два, при этом блок 2 запрета информационной последовательности содержит регистр 9 сдвига и два сумматора 10, ) 1 по модулю два, а блок 3 запрета синхронизирующей последовательности содержит регистр 12 сдвига и.сумматор )3 по модулю два.

Устройство работает следующим образом.

Поступающая из канала кодограмма через входной переключатель 1 и последовательно соединенные блок 2 и блок 3 поступает на вход счетчика 6, подсчитывающего количество нулевых символов, поступивших подряд на его вход. При фиксации счет чиком 6 поступления на его вход нулевой кодограммы определенной длины на его выходе появляется сигнал, поступающий на входной переключатель 1 и разрешающий выдачу дешифратором 4 сигнала управления выходным переключателем 5 при поступлении на его вход комбинации циклового фазирования с учетом фазового сдвига. При этом, с выхода первого сумматора 7 через входной переключатель 1 на вход блока 2 продолжает поступать кодограмма тождественная той, которая поступала ранее из канала и. являющаяся ее непрерывным продолжением, т.к. с выхода сумматора 10 снимается кодограмма, информационная часть которой тождественна части кодограммы, поступившей ранее из канала и являющаяся ее продолжением, а для компенсации фазового сдвига синхронизирующей последовательности, снимаемой с выхода сумматора 10 относительно синхронизирующей последовательности, поступившей ранее из канала, кодограмма, снимаемая с выхода сумматора 10, подается на один из входов первого сумматора 7, другие входы которого соединены с определенными отводами регистра 12 блока 3.

При поступлении на вход дешифратора

4 комбинации циклового фаэирования с учетом фазового сдвига на его выходе появляется управляюгций сигнал, замыкающий выходной переключатель 5 для передачи на

4 выход элементного информационного кодового слова.

Информация, записанная в регистре 9, подается последовательно на выход выходного переключателя 5 через один из входов второго сумматора 8, другие входы которого подключены к определенным отводам регистра 12 таким образом, чтобы. исключить из передаваемой на выход кодограммы синхронизируюгцую последовательность, выделив тем самым, информационное кодовое слово, Использование в предлагаемом устройстве новых операций позволяет в реализованйых на его основе устройствах добиться значительного сокращения времени обработки информации, упростить алгоритм работы и схемы устройств.. Устройство для декодирования самосинхронизирующихся кодограмм, содержащее последовательно соединенные входной переключатель, блок запрета информационной последовательности и последовательно соединенные блок запрета синхронизирующей последовательности, дешифратор и выходной переключатель, причем один из выходов блока запрета синхронизирующей последо.вательности подключен к входу счетчика, а другие выходы — к входам первого сумматора по модулю два, кроме того, первый выход блока запрета информационной последовательности подключен к входу второго сумматора но модулю два, отличающееЕя. тем, что, с целью сокращения времени декодирования принятой информации, до- полнительный выход блока запрета информационной последовательности подключен к соответствующему входу первого сумматора по модулю два, выход которого подключен к соответствующему входу входного переключателя, к управляющему входу которого и к управляющему входу дешифратора подключен выход счетчика, причем соответствующие входы второго сумматора по модулю два объединены с соответствующими входами первого сумматора по модулю два, выход второго сумматора по модулю два подключен к другому входу выходного переключателя, а второй выход блока запрета информационной последовательности подключен к входу блока запрета синхронизирующей последовательности.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 365033, кл. Н 03 К 13/04, 1971.

658769

Составитель Е. Любимова

Редактор Л. Гельфман Техред О. Луговая Корректор F. 11анп

Заказ 2083/56 Тираж 774 Подннс кое

Ш1ИИПИ Государственного комитета СССР по делам изобретен и11 и от к р ьл и и

113035, Москва, Ж-35, Раушская наб., д. 4(5

Филиал ППП «Патентэ, r. Ужгород, ул. Проектная, 4