Устройство для сдвига цифровой информации

Иллюстрации

Показать всеРеферат

ОП ИСАН И Е

ИЗОБРЕТЕНИЯ (1166ОО47

Союз Советских Сооиаоистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 02.07.76 (21) 2380493/18-24 с присоединением заявки № (51) М. Кл. б 06F 7/395

G 11С 19/00 ссср (53) УДК 681.327.66 (088.8) о делам изобретений (43) Опубликовано 30.04.79. Бюллетень № 16 и открытий (45) Дата опубликования описания 30.04.79 (72) Авторы изобретения

В. В. Малый, Н. Ф. Меховский, Г. С. Иванов, В, Н. Середа, О. И. Плясов и А. Г. Щербаченко (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СДВИГА ЦИФРОВОЙ

ИНФОРМАЦИИ

Государственный комитет (23)

2 Приоритет

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах для сдвига цифровой информации.

Известны устройства для сдвига цифро- 5 вой информации, содержащие инвертор, запоминающий триггер, триггер обратной связи, элемент совпадения, регистр сдвига (1).

Наиболее близким техническим решением 10 является устройство для сдвига цифровой информации, содержащее регистры сдвига, одни из входов первого регистра сдвига соединены с первым триггером с раздельными входами, элемент ИЛИ, входы кото- 15 рого соединены со входами устройства, а выход — с первыми входами элементов И и входом счетного триггера, выходы которого соединены со вторыми входами элементов И, а также дешифратор, коммута- 20 тор, генератор тактовых импульсов, блок формирования сигнала «конец кодовой комбинации», элемент задержки (2).

Недостатком известных устройств явля- 25 ется невозможность достижения высокой надежности, так как их нельзя использовать в режиме мажоритирования при рассинхронизации входной информации каналов, 30

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что оно содержит два преобразователя кодов и второй триггер с раздельными входами, подключенный к одним из входов второго регистра сдвига, входы триггеров с раздельными входами соединены с одними из выходов преобразователей кодов, другие выходы которых соединены с регистрами сдвига, одни из входов их — с выходами элементов И, другие входы — со входами устройства, также и тем, что преобразователь кодов содержит два элемента И, входы которых подключены к соответствующим входам блока, выходы — к триггерам, подключенным к мажоритарным элементам, выходы которых подключены ко входам элемента ИЛИ, выход его — к формирователю импульсов.

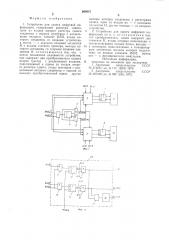

На фиг. 1 изображена блок-схема устройства для сдвига цифровой информации; на фиг. 2 — блок-схема преобразователя кодов.

Устройство для сдвига цифровой информации содержит элемент 1 ИЛИ, входы которого соответственно соединены с первым и вторым входами первого 2 и второго 3 преобразователей кодов. Входы элемента 1 ИЛИ являются также входами по660047

3 дачи в устройство парафазного кода: Вход

«1», Вход «О». Вь ход элемента 1 ИЛИ соединен со входом счетного триггера 4 и первыми входами первого 5 и второго 6 элементов И, к Вторых| Входам I QTopbl ; подключены выходы счетного триггера 4. Выход 1;epllolo элемента И 5 подключен к третьему входу первого преобразователя кодов 2 и к четвертому входу второго прсобразователя кодов 3. Выход второго элемента И 6 подключен к чствертому входу

1|срвого преобразователя кодов 2 и к третьему входу второго преобразователя кодов 3. Первый и второй выходы преобразователей кодов 2, 3 соединены со входами соответственно первого 7 н второго 8 триггеров с раздельными входами. Третьи вы«оды преобразователей кодов 2, 3 соединены с шинами синхроимпульсов первого 9 и второго 10 регистров сдвига соотвстственно. Выходы первого и второго триггезов 7, 8 с раздельными входами соединены с информационными входами первого 9 и второго 10 регистров сдвига соответственно.

Каждый преобразователь кодов содержит первый 11 и второй 12 элементы И, выходы которых подключены к первым входа|х| триггеров 13, 14. Выходы триггеров 13, 14 подключены к входам махкоригарных элементов 15, !6, выходы которых подключены к первому и второму выходам преобразователя кодов и к входам элемента

ИЛИ 17. Выход элемента ИЛИ 17 подключен к входу формирователя 18 импульсов, выход которого является третьим вы.voäoì преобразователя кодов.

Первый вход преобразователя кодов подключен Il первому входу элемента И 11; второй в.,од преобразователя кодов подключен к первому входу элемента И 12, третий вход преобразователя кодов подключен к вторым входам первого 11 и второго 12 элементов И; четвертый вход преобразователя кодов подключен к вторым входам триггеров 13, 14.

Устройство работает следующим образом. Импульсы парафазного кода «1» и «О» со входа устройства поступают на первый и второй входы преобразователя кодов 2, используемого для мажоритирования нечетных разрядов принимаемого кода, преобразователя кодов 3, используемого для мажоритирования четных разрядов принимаемого кода, и входы элемента ИЛИ 1.

При помощи элемента ИЛИ 1, счетного триггера 4 и элементов И 5, 6 входная последовательность импульсов «1», «О» преобразуется в последовательность нечетных импульсов СИ1 и последовательность четных импульсов СИ2.

Входные импульсь! «1», «О» при помощи элементов 11, 12 И и триггеров 13, 14 преобразуются в импульсы, длительность которых равна периоду следования входных импульсов. При этом в преобразователе

65 кодов 2 триггер 13 формирует все нечетные импульсы «1», триггер 14 — все нечетные импульсы «О». Аналогичнос преобразование происходит в преобразователе кодов 3, где три тср 13 формирует все четные импульсы «1», триггер 14 — — все четные импульсы «О».

В прсобразователс кодов 2 осуществляются слсду|ошне условия установки триггеров 13, 14: — установка триггера 13 в единичное состояние «1» / СИ1; — установка триггера 14 в единичное состояние «О» Л СИ1; установка триггеров 13, 14 в нулевое состояние — — наличие импульса СИ2.

В преобразователе кодов 3 осуществляются следующие условия установки триггеров 13, 14: — установка триггера 13 в единичное состояние «1» Л СИ2; — установка триггера 14 в единичное состояние «0» Л СИ2; — установка три|теров 13, 14 в нулевое состояние — наличие импульса СИ1.

Выходные сигналы триггеров 13, 14 мажоритируются при помощи мажоритарных элементов 15, 16. Промажоритированные сигналы «1» всех нечетных импульсов поступают с первого выхода преобразователя кодов 2 на первый вход триггера 7 с раздельными входами и устанавливают его в единичное состояние. Промажоритированные сигналы «0» всех нечетных импульсов поступают с второго выхода преобразователя кодов 2 на второй вход триггера 7 с раздельными входами и устанавливают его в нулевое состояние. Аналоги 1ным образом устанавливается в единичное или H)левое состояние триггер 8 с раздельными входами промажоритированными сигналами «1», «О».

С выходов триггера 7 с раздельными входами на информационные входы регистра сдвига 9 поступают потенциальные сигналы, соотвстству|ощие нечетным разрядам сдвигаемой последовательности импульсов; аналогично на информационные входы регистра сдвига 10 поступают потенциальные сигналы с выходов триггера 8 с раздельными входами, соответствующие четным разрядам сдвигаемой последовательности импульсов. Таким образом, в регистр сдвига

9 запишстся код, соответствующий нечетным разрядам входной последовательности импульсов, в регистр сдвига 10 — код, соответствующий четным разрядам входной последовательности импульсов, Импульсы сдвига формируются при помощи элемента

ИЛИ 17 и формирователя импульсов 18 и с третьих выходов преобразователей кодов 2, 3 поступают на входы синхроимпульсов регистров сдвигов 9, 10 соответственно.

660047

В .E р В

Вх.E Юк. В иг. 1

Р,3

Вх

$ t!

), 7Ф

»» хоЗ у

rave.

Формула изобретения

1. Устройство для сдвига цифровой информации, содержащее регистры сдвига, одни из входов первого регистра сдвига соединены с первым триггером с раздельными входами, элемент ИЛИ, входы которого соединены со входами устройства, а выход — с первыми входами элементов

И и входом счетного триггера, выходы которого соединены со вторыми входами элементов И, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит два преобразователя кодов и второй триггер с раздельными входами, подключенный к одним из входов второго регистра сдвига, входы триггеров с раздельными входами соединены с одними из выходов преобразователей кодов, другие выходы которы., соединены с регистрами сдвига, одни из входов их — с выходами элементов И, другие выходы — со входами устройства.

5 2. Устройство для сдвига цифровой информации по и. 1, î".л и ч а ю щ ее с я тем, что преобразователь кодов содержит два элемента И, входы которых подключены к соответствующим входам блока, выходы—

10 к триггерам, подключенным и мажоритарным элементам, выходы которых подключены ко входам элемента ИЛИ, выход

его — и формирователю импульсов.

Источники информации, 15 принятые во внимание при экспертизе

1. Авторское свидетельство СССР !

¹ 474051,,кл. G 11С 19/00, 1970.

2. Авторское свидетельство СССР

¹ 407302, кл. G 06F 5/04, 1972.