Устройство для контроля микропроцессора

Иллюстрации

Показать всеРеферат

иц660053 очзз С оTryg Сони "» н,-, тнналину

1 есч б»

»а

Ф .»-.=- - »- - 7 (61) Дополнительное к авт. свид-ву— (22) Заявлено 17.01.77 (21) 2444478/18-24 с присоединением заявки ¹â€” (23) Приоритет— (43) Опубликовано 30.04.79. Бюллетень № 16 (45) Дата опубликования описания 30.04.79 (51) M. Кл.

G 06F 11/04

Гооударстеанный комитет (53) УДК 658.562 (088.8) по делам изобретений и открытий (72) Авторы изобретения В. И. Горин, Л. А. Данилов, P. И. Рапопорт и В. М. Рязанов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МИКРОПРОЦЕССОРА

Изобретение относится к области вычислительной техники и может быть использовано для проверки работоспособности и программного обеспечения микропроцессоров.

Известны устройства для контроля систем обработки информации, содержащие блоки регистров, блок памяти, блок преобразователей кода, блоки совпадения кодов, блок адресного опроса и логический блок управления, и выполняющие функции формирования кодов адресов и данных для ввода в контрольную систему и последующего анализа правильности ее реакций (1).

Недостаток этих устройств заключен в их сложности, об. словленной большим объемом памяти, необходимой для хранения всех исполненных команд проверки.

Наиболее близким к данному по сущности технического решения является устройство для контроля, содержащее блок индикации, блок управления, первый выход которого подключен к управляющим входам блока формирования адресов и блока формирования данных, управляющие выходы которых соединены с соответствующими входами блока управления, соединенного вторым выходом с блоком ввода, выход которого и информационный выход блока формирования адресов подключены к соответствующим входам блока буферной памяти, первый выход которого подключен к первому входу блока формирования данных, второй вход и выход которого являются первым входом и выходом устройства (2).

Недостаток этого устройства состоит в том, ITQ определение неисправности требует большого интервала времени. Это обус10 ловлено тем, что индикация осуществляется только для последнего временного такта. Поскольку специфика микропроцессора требует для анализа места и характера неисправности знания состояния объекта

15 контроля на предшествующих тактах, а иногда оказывается полезным и состояние на нескольких последующих тактах, то реализация этих условий требует больших затрат времени.

20 Целью изобретения является сокращение времени определения неисправностей.

Поставленная задача достигается тем, что в устройство введены блок памяти, блок регистров условий запуска и схема

25 сравнения условий запуска, причем входы схемы сравнения условий запуска подключены соответственно к выходу блока регистров условий запуска, входом соединенного с третьим выходом блока управления, З0 и выходу блока формирования данных, выЬООО5З ход схемы сравнения условий запуск;. подключен к управляющему входу блока индикации, информационный вход которого соединен с выходом блока памяти, Входы которого подключены соответственно ко второму выходу блока буфеplioII памяти, выходу блока формирования данных и второму входу устройства.

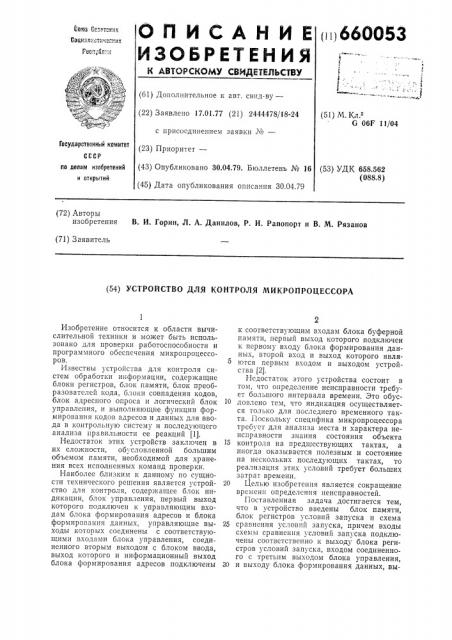

На чертеже представлена блок-схема устройства, содержащая блок 1 управления, блок 2 формирования адресов, слок 3 формирования данных, блок 4 ввода, блок

5 буферной памяти, блок б регистров условий запуска, блок 7 памяти, схема сравнения 8 условий запуска, блок индикации 9 и контролируемый микропроцессор 10.

Блок 1 управления служит для хранения и отраоотки программы испытаний и выполняет также функции синхронизации и управления по отношению к другим блокам устройства. Блок 2 формирования адресов содержит регистры и схемы сравнения и служит для формирования адреса быстродействующего блока 5 буферной памяти, где хранятся тесты и ответные реакции контролируемого микропроцессора 10.

По командам, выдаваемым из блока 1, содержимое адресного регистра блока 2 мо>кет быть уменьшено, увеличено, сдвинуто на 1 разряд или изменено другим образом.

Блок 3 формирования данных содерж1!т регистры и схемы сравнения и служит для выдачи входных последовательностей (инструкций и операндов) в контролируемый микропроцессор 10, полученных пз блока 5 и (или) модифицированных в соответствии с командами из блока 1. Блок 3, I

9, который индицируст информацию, содержащуюся в блоке 7. Эта память может быть организована, например, в виде массива сдвиговых регистров, разрядность которых соответствует максимальному числу. слов, индпцирусмых в блоке 9.

Устройство работает следующим образом.

Блок 2 формирует адрес ячейки блока о, содержимое которой через блок 3 поступает в контролируемый микропроцессор 10.

Ответные реакции поступают обратно в блок 3. Одновременно информация из блока 5, а также информация, поступающая в микропроцессор 10 и выдаваемая им, фиксируется в блоке 7 памяти и выдается на

"0

Зо

60 индикацию в блок 9. При этом, поскольку скорость выдачи сло1, в микропроцессор 10 достаточно высока, н 1 блоке 9 организуется TBK называемый «плывущий кадр», обеспсчиВа10!11ий послсдоватсльный сдвиг индицирусмых слов, например, снизу Вверх при

НОявлении на Входе каждого НОВОГО слоВа.

В регистры условий блока б из блока 1 введены условия, при кo!opiix производится блокировка ввода информации в блок 7 памяти, после чего сдвиг строк прекращается и на экране блока 9 оказывается доступным для визуального контроля все множество слов, непосредственно предшествовавших выдаче сигнала блокировки, включая слово, на котором блокировка произошла.

Аналогично, если блок 3 зафиксирует нарушение в работе микропроцессора 10, сообщит об этом в блок 1, который примет решение оо остановке испытаний. то на вход блока 7 перестанут поступать данные, а на экране блока 9 будет представлено последнее введенное слово вместе с набором предшествующих ему слов в порядке их поступления в микропроцессор.

Таким образом, устройство обеспечивает вывод заданного множества слов контрольного теста, обеспечивающих Возможность проведения анализа состояния микропроцсссора и определения характера его неисправности.

Формул а изобретения

Устройство для контроля микропроцессора, содержащее блок индикации, блок управления, первый выход которого подключен к управляющим Входам блока формирования адресов и блока формирования данных, управляющие выходы которых соединены с соответствующими входами блока управления, соединенного вторым выходом с блоком ввода, выход которого и информационный выход блока формирования адресов подключены к соответствующим входам блока буферной памяти, первый выход которого подключен и первому входу блока формирования данных. второй вход и выход которого явля!отся первым входом и выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью сокращения времени определения неисправностей, В устройство введены блок памяти, блок регистров условий запуска н схема сравнения условий запуска, причем входы схсмы сравнения условий запуска подключены соответственно к выходу блока регистров условий запуска, входом соединенного с третьим выходом блока управления и выходу блока формирования данных, выход схемы сравнения

660053

СССI

СССР с

1.Г 1 д

Составитель В. Вертлиб

Редактор С. Равве

Техред Н. Строганова

Корректор Е, Угроватова

Заказ 56879 Изд. ¹ 265 Тираж 779 Подписное

НПО Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )К-35, Раушская паб., д. 4/5

Типография, пр. Сапунова, 2 условий запуска подключен к управляющему входу блока индикации, информационный вход которого соединен с выходом блока памяти, входы которого подклю.ены соответственно ко второму выходу блока буферной памяти, выходу блока формирования данных и второму входу устройства.

Источники информации, ; ринятыс во вннман :е при "-кспсртизс

1. Авторское свидетельство

5 № 347739, кл. С 05В 23/02, 1970.

2. Авторское свидетельство

¹ 49S6I9, кл. G 06F 11/00, 1974.