Преобразователь отношения двух частот в код

Иллюстрации

Показать всеРеферат

О П И С А H И Е пщ66О231

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (б1) Дополнительное к авт. свид-ву (22) Заявлено 22.04.76 (21) 2351123/18-21 с присоединением заявки № (23) Приоритет (43) Опубликовано 30.04.79. Бюллетень № 16 (45) Дата опубликования описания 30.04.79 (51) М, Кл.

Н ОЗК 13/00

Государственный комитет (53) УДК 621.374.3 (088.8) ло делам изобретений и открытий (72) Автор изобретения

П. В. Соловов,(71) Заявитель

Рязанский радиотехнический институт (54) ПРЕОБРАЗОВАТЕЛЬ. ОТНОШЕНИЯ ДВУХ ЧАСТОТ

В КОД

Изобретение относится к импульсной технике.

Известен преобразователь частоты в код, содержащий сдвигающий регистр, на синхронизирующий вход которого поступает входной сигнал, а на управляющий вход— сигналы запуска, блок логических элементов, управляющее устройство, генератор опорной частоты, формирователь, синхрони:з а тор (1) .

Данный преобразователь не может производить преобразование отношения двух частот в код.

Наиболее близким по технической сущности к заявленному является преобразователь отношения двух частот в код, содержащий управляемый делитель частоты, входы разрядов которого соединены с выходами разрядов счетчика, выходы разрядов управляемого делителя частоты подключены к входам блока логических элементов И, выходы которого соединены с входами разрядов счетчика, информационным входом связанного с выходом первого логического элемента И, один вход которого подключен к шине опорной частоты, второй логический элемент И, один вход которого подключен к шине первого входного сигнала, а его выход соединен с входом триггера и первым входом третьего логического элемента И. Выход триггера соединен через элемент задержки с вторым входом третьего логического элемента И и непосредственно с первым входом четверто5 го логического элемента И, выход третьего логического элемента И вЂ” с входом управления блока логических элементов И, а выход четвертого логического элемента И— с первым управляющим входом управляе10 мого делителя частоты (2).

Данный преобразователь не обеспечивает достаточной точности.

Целью изобретения является повышение точности.

15 Поставленная цель достигается тем, что в преобразователь отношения двух частот в код, содержащий управляемый делитель частоты, входы разрядов которого соединеIbl с выходами разрядов счетчика, BhlxojIы

20 разрядов управляемого делителя частоты подключсны к входам блока логических элементов И, выходы которого соединены с входамп разрядов счетчика, информационным входом связанного с выходом IlcpBQI О

25 логического элемента И, один вход которого подключсн к шине опорной частоты, второй логический элемент И, один вход которого подключен к шине первого входного сигнала, а его выход сосдинен с входом

31 триггера и первым входом третьего логичс060231

15 0

2" F»

)I

N,= т„ где

Т„=

Tx ——

3 ского элемента И, причем выход триггера соединен через элемент задержки с вторым входом третьего логического элемента И и непосредственно с первым входом четвертого логического элемента И, выход третьего логического элемента И вЂ” с входом управления блока логических элементов И, а выход четвертого логического элемента И— с первым управляющим входом управляемого делителя частоты, дополнительно введены счетчик, коммутатор, блок вычитания, регистр и блок выделения периода. Вход блока выделения периода соединен с шиной второго входного сигнала, первый выход подключен к второму входу псрвого логического элемента И, а второй выход — к второму управляющему входу управляемого делителя частоты и второму входу второго логического элемента И. При этом один вход регистра соединен с выходом у»равляемого делителя частоты и одним входом блока вычитания, второй вход которого подключен к входу триггера, а выход блока вычитания соединен с входом дополнительного счетчика, выходом подключенного к управляющему входу коммутатора, информационные входы которого соединены с шинами опорной частоты и ее гармоник, а выход — с вторым входом четвертого логичсского элемента И, причем второй вход регистра соединен с выходом третьего логического элемента И.

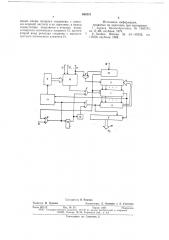

Структурная электрическая схема описываемого преобразователя приведена на чертеже.

Преобразователь содержит управляемый делитель 1 частоты, счетчики 2, 3, блок 4 логических элементов И, регистр 5, логические элементы И 6 — 9, коммутатор 10, блок

11 вычитания, триггер 12, элемент 13 задержки, блок 14 выделения периода, На входные шины 15, 16 поданы входные сигналы, на шины 17, 18, 19 — опорная частота и ее гармоники.

Выходной код снимается с выхода 20.

Принцип работы устройства заключается в следующем.

Модулирующая зависимость устройства имеет вид где N- — выходной двоичный код;

F„, Р, — входные частоты; и — разрядность тока N,.

Реально в устройстве вместо деления частот Р„на Р„производится деление их периодов, т. е.

1IF„, — период частоты F„,;

1/F,. — псриод частоты F.„.

4

Для нормальной работы устройства должно выполняться условие

Tó макс 2Т с мин

В работе устройства можно выделить два этапа: преобразование периода Т„ в двоичный код NT, деление Т„на T„, в резульg тате чего определяется выходной код N„.

В исходном состоянии счетчики 2, 3 и управляемый делитель 1 частоты установлены в «О», а в регистр 5 записана «1» во второй разряд. Кодирование периода Т„производится путем его заполнения высокой опорной частотой F с помощью блока 14 выделения периода Т„, логического элемента И 8 и счетчика 2. Блок выделения периода, основу которого составляет двухразрядный суммирующий счетчик (не показан), функционирует таким образом, что на первом его выходе высокий потенциал появляется в течение отрезка времени между первым и вторым импульсами частоты

Р, (т. е. в течение периода частоты), а на втором его выходе — после окончания первого периода той же частоты. Поэтому с приходом первого импульса частоты F îòкрывается логический элемент И 8 и в счетчике 2 накапливается код Л „, пропорциональный периоду T„ от 0 до величины — Ра.

С приходом второго импульса частоты

Р„логический элемент И 8 закрывается, прекращая поступление импульсов частоты

F, в счетчик 2. На этом заканчивается процесс кодирования периода T

Далее начинается второй этап: деление

Т„на T„. Второй импульс частоты Р„, вызывая появление высокого потенциала на втором выходе блока 14 выделения периода, производит перепись кода 1Чг из счетчика 2 в управляемый делитель 1 частоты и, кроме того, открывает логический элемент И 9, Процесс деления состоит из повторяющихся одинаковых шагов: вычитание из делимого делителя и удвоение полученного остатка.

В предлагаемом устройстве деление реализуется следующим образом.

Первый (после открывания логического элемента И 9) импульс частоты F„óñòàíàâливает триггер 12 в «1». При этом опорная частота F, с коммутатора 10 через логический элемент И 6 начинает поступать на счетный вход управляемого делителя 1 частоты, списывая его содержимое от величины,VT до «О». К моменту прихода следуи ющего (второго) импульса частоты F„содержимое управляемого делителя 1 частоты V „, уменьшается на величину F,Ò„è становится равным

Н,г, -- NT — T „F,;-- F, (Т, — т»), где NzT, — код остатка AT — — ҄— Т„ после первого шага деления.

660231

Второй импульс частоты F, пройдя логический элемент И 7, открывает блок 4 логических элементов И, через который код

N<т, переписывается в счетчик 2. Кроме того, этот же импульс записывает «1» в младший разряд регистра 5. Итак, на первом шаге деления уже реализовано вычитание из делимого Т„делителя Т„и получен остаток ХТь Так как делимое оказалось больше делителя, старшей цифре частного присвоено значение «1». Далее должно производиться вычитание Т„из удвоенного первого остатка 2АТь Делается это так. После переноса кода остатка Ж т, из управляемого делителя 1 частоты в счетчик

2 код Л у-„продолжает описываться импульсами частоты F, от величины N

1 частоты в счетчик 2 очередного (второго) остатка N ix, равного

A ò, — 2Н т, — Т,Р,.

Третий импульс частоты F„, как и второй импульс, записывает «1» в первый разряд регистра 5. Записанная ранее «1» к этому времени уже сдвигается во второй разряд регистра 5 с помощью импульса выходной частоты (F,), образовавшегося в момент обнуления управляемого делителя частоты.

В рассмотренных двух шагах деления делимое (Т„и 2ЛТ1) больше делителя Т„, поэтому на каждом шаге очередной цифре частного присваивается значение «1» и проводится сдвиг кода частного влево.

Пример выбран так, что удвоенный второй остаток меньше делителя, т. е.

2АТ, Т .

Поэтому после второго обнуления управляемого делителя частоты в третьем периоде частоты Р„(т. е. после пришедших подряд двух импульсов Р,) на выходе блока

11 вычитания появляется импульс, который записывается в счетчик 3. С коммутатора

10 поступает уже частота F,/2, и поэтому следующий импульс частоты Р „, появляетМДтг ся спустя время, равное

Р о/2 т. е. 2АТ2. Так как в данном примере

AT, + AT, + 2дТ, (Т,, то на выходе блока 11 вычитания оказывается еще один импульс, который, изменив

30 б код в счетчике 3, переключает коммутатор на выдачу частоты F,/22.

В соответствии с этим следующий период частоты F,- будет в два раза больше предыдущего. Если теперь AT> + AT> +

+ 2ATg + 4ATg (Т„, то процесс повторится. Иначе, как в данном примере, повторится ситуация, аналогичная первым двум шагам деления.

Предлагаемое устройство позволяет за счет небольшого усложнения схемы одновременно с выполнением операции деления произвести преобразование частоты в код.

Использование его в качестве устройства сопряжения частотных датчиков в ЦВМ дает возможность разгрузить последнюю от наиболее трудоемкой для нее операции деления.

Формула изобретения

Преобразователь отношения двух частот в код, содержащий управляемый делитель частоты, входы разрядов которого соединены с выходами разрядов счетчика, выходы разрядов управляемого делителя частоты соединены с входами блока логических элементов И, выходы которого соединены с входами разрядов счетчика, информационный вход которого соединен с выходом первого логического элемента И, один вход которого подключен к шине опорной частоты, второй логический элемент И, один вход которого подключен к шине первого входного сигнала, а выход второго логического элемента И соединен с входом триггера и первым входом третьего логического элемента И, выход триггера соединен через элемент задержки с вторым входом третьего логического элемента И и непосредственно с первым входом четвертого логического элемента И, причем выход третьего логического элемента И соединен с входом управления блока логических элементов И, а выход четвертого логического элемента И соединен с первым управляющим входом управляемого делителя частоты, о т л и ч а юшийся тем, что, с целью повышения точности, в него дополнительно введены счетчик, коммутатор, блок вычитания, регистр и блок выделения периода, вход которого соединен с шиной второго входного сигнала, первый выход блока выделения периода подключен к второму входу первого логического элемента И, а второй выход блока выделения периода соединен с вторым управляющим входом управляемого делителя частоты и вторым входом второго логического элемента И, при этом один вход регистра соединен с выходом управляемого делителя частоты и одним входом блока вычитания, второй вход которого подключен к входу триггера, а выход блока вычитания соединен с входом дополнительного счетчика, выход которого соединен с управляющим входом коммутатора, информационные входы которого соединены с шинами опорной частоты и ее гармоник, а выход коммутатора подключен к второму входу четвертого логического элемента И, причем второй вход регистра соединен с выходом третьего логического элемента И.

660231

Источники информации, принятые во внимание при экспертизе

1. Заявка Великобритании № 1365761, кл. G 4Н, опублик. 1974.

5 2. Заявка Японии № 43 †303, кл.

110ДО, опублик. 1968.

Составитель В. Егорова

Редактор И. Грузова Корректоры: Е. Осипова и А. Галахова

Заказ 687/15 Изд. № 271 Тираж 1059 Подписное

НПО Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Я(-35, Раушская наб., д. 4,5

Типография, пр. Сапунова, 2