Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

(11) 2

ОП ИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 08.12.75 (21) 2309809 18-21 с присоединением заявки № (23) Приоритет (51) М. Кл. -

Н ОЗК 13/18

Государственный комитет (43) Опубликовано 30.04.79. Бюллетень № 16 (53) УДК 681.325 (088.8) по делам изобретений и открытий (45) Дата опубликования описания 30.04.79 (72) Автор изобретения

А. И. Лаврушев (71) Заявитель (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к вычислительной технике и может быть использовано для преобразования мгновенного значения переменного напряжения в цифровой код.

Известен аналого-цифровой преобразователь, содержащий резисторный делитель напряжения, пороговые схемы, дешифратор, в котором процесс преобразования напряжения в код с погрешностью, равной шагу квантования, выполняется в течение одного такта (1).

Недостатком устройства является сравнительно низкая точность преобразования.

Известен аналого-цифровой преобразователь, содержащий шесть последовательно соединенных резисторов, подключенных к входным шинам источника эталонного напряжения, пять компараторов, причем пер вый вход первого компаратора соединен с входной шиной источника эталонного напряжения, первый вход второго компаратора — с первым и вторым резисторами, первый вход третьего компаратора — с вторым и третьим резисторами, первый вход четвертого компаратора — с третьим и четвертым резисторами, а первый вход пятого компаратора — с четвертым и пятым резисторами, шифратор, выход которого соединен с входом регистра, осуществляющий преобразование посредством сравнения аналоговой величины с напряжениями резисторного делителя эталонного напряжения (2).

Недостатком устройства является боль5 шая погрешность квантования.

Целью изобретения является уменьшение погрешности квантования.

Это достигается тем, что в аналого-цифровой преобразователь, содержащий шесть

10 резисторов, пять компараторов, шифратор и регистр, введены усилитель, три ключа, два элемента И вЂ” НЕ, элемент И, два элемента И вЂ” ИЛИ вЂ” НЕ, два триггера и логическое устройство. Первый вход уси15 лителя соединен с вторыми входами первого и пятого компараторов, а выход соединен с вторыми входами второго, третьего и четвертого компараторов. Второй вход усилителя соединен с выходами трех ключей, вход первого ключа соединен с шиной «Земля» источника эталонного напряжения, вход второго ключа соединен с первым входом пятого компаратора, первый входтретьего ключа — с пятым и шестым резисторами, управляющий вход первого ключа— через элемент И вЂ” НЕ с первым входом элемента И, с выходом первого элемента И—

ИЛИ вЂ” HE и с первым входом первого триггера. Управляющий вход второго ключа

30 соединен через элемент И вЂ” НЕ с вторым

660242 входом элемента И, с выходом второго элемента И вЂ” ИЛИ вЂ” HE и с первым входом второго триггера. Вторые входы триггеров соединены с входной шиной генератора тактовых импульсов. Два выхода каждого триггера соединены с четырьмя входами логического устройства. Четыре входа первого элемента И вЂ” ИЛИ вЂ” НЕ соединены соответственно с первыми выходами первого, второго, третьего и четвертого компараторов и с пятым, шестым, седьмым и восьмым входами логического устройства, четыре входа второго элемента И вЂ” ИЛИ вЂ” НЕ соединены соответственно с вторыми выходами второго, третьего, четвертого и пятого компараторов и с девятым, десятым, одиннадцатым и двенадцатым входами логического устройства. Второй выход первого компаратора и первый выход пятого компаратора соединены соответственно с тринадцатым и четырнадцатым входами логического устройства, а его выход соединен с входом шифратора, а выход элемента И соединен с вторым входом третьего ключа.

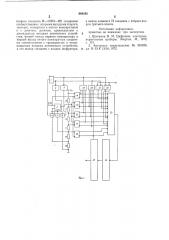

Структурная схема аналого-цифрового преобразователя приведена на фиг. 1. Временные диаграммы, поясняющие принцип работы устройства, приведены на фиг. 2.

Аналого-цифровой преобразователь содержит элемент 1 И, элемент 2 И вЂ” НЕ, усилитель 3, ключи 4 — 6, элемент 7 И вЂ” HE, резисторы 8 — 13, компараторы 14 — 18, элементы 19, 20 И вЂ” ИЛИ вЂ” НЕ, триггеры 21, 22, логическое устройство 23, шифратор 24, регистр 25.

Входной сигнал У„ совместно с добавочной постоянной составляющей ЛУ подается на первый вход усилителя 3, имеющий коэффициент усиления, равный единице. На второй вход усилителя 3 с помощью ключей 4 — 6 подается одно из напряжений ЛУ, 2ЛУ или нулевой потенциал. Каждый такт преобразования состоит из двух этапов.

На первом этапе определяется положение мгновенного значения входного напряжения У„ относительно грубых уровней квантования. Элементы 19, 20 фиксируют зону между уровнями, в которой лежит напряжение. Элементы 19, 20 при помощи ключей 4 — 6 воздействуют на один из входов усилителя 3 и либо уменьшают, либо уве1 личивают на ЛУ (ЛУ= — кванта грубого

3 отсчета) уровень сигнала íà его выходе.

Уровни срабатывания компараторов 14 — 18 сместятся на ЛУ в глубь зоны, где находится напряжение U . Таким образом, квант грубого отсчета делится на три более мелких. К выходам элементов 19, 20 подключены два триггера 21, 22. Выходы триггеров 21, 22, как и выходы всех компараторов, подключены к логическому устройству

23, формирующему на выходе единичный код. С выхода устройства 23 единичный код поступает на вход шифратора 24, образу:о5

5О

65 щего на выходе двоичный позиционный код, записываемый в регистр 25. Уровни эталонного напряжения 1/„„необходимые для компараторов и напряжения, подключаемые ключами 4 — 6 к одному из входов усилителя 3, поданы с резисторов 8 — 13 делителя эталонного напряжения. Сопротивления резисторов 11 — 13 составляют одну треть от сопротивлений резисторов 8 — 10.

Устройство позволяет, не увеличивая количество компараторов, втрое увеличить число уровней квантования и, следовательно, втрое уменьшить погрешность квантования, Формула изобретения

Аналого-цифровой преобразователь, содержащий шесть последовательно соединенных резисторов, подключенных к входным шинам источника эталонного напряжения, шифратор, выход которого соединен с входом регистра, пять компараторов, первый вход первого компаратора соединен с шиной источника эталонного напряжения, первый вход второго компаратора соединен с первым и вторым резисторами, первый вход третьего компаратора соединен с вторым и третьим резисторами, первый вход четвертого компаратора соединен с третьим и четвертым резисторами, первый вход пятого компаратора соединен с четвертым и пятым резисторами, отличающийся тем, что, с целью уменьшения погрешности квантования в него, введены усилитель, три ключа, два элемента И вЂ” НЕ, элемент И, два элемента И вЂ” ИЛИ вЂ” HE, два триггера и логическое устройство, первый вход усилителя соединен с вторыми входами первого и пятого компараторов, а выход соединен с вторыми входами компараторов, второй вход усилителя соединен с выходами трех ключей, вход первого ключа соединен с общей шиной, вход второго ключа соединен с первым входом пятого компаратора, первый вход третьего ключа соединен с пятым и шестым резисторами, управляющий вход первого ключа соединен через первый элемент И вЂ” HE с первым входом элемента И, с выходом первого элемента И—

ИЛИ вЂ” НЕ и с первым входом первого триггера, управляющий вход второго ключа соединен через второй элемент И вЂ” НЕ с вторым входом элемента И, с выходом второго элемента И вЂ” ИЛИ вЂ” НЕ и с первым входом второго триггера, вторые входы триггеров соединены с входной шиной генератора тактовых импульсов, два выхода даждого триггера соединены с четырьмя входами логического устройства, четыре входа первого элемента И вЂ” ИЛИ вЂ” НЕ соединены соответственно с первыми выходами первого, второго, третьего и четвертого компараторов и с пятым, шестым, седьмым и восьмым входамп логического устройства, четыре входа второго элемента И вЂ” ИЛИ вЂ” НЕ соединены соответственно с вторыми выходами второго, третьего, четвертого и пятого компараторов и с девятым, десятым, одиннадцатым и двенадцатым входами логического устройства, второй выход первого компаратора и первый выход пятого компаратора соединены соответственно с тринадцатым и четырнадцатым входами логического устройства, а его выход соединен с входом шифратора, 660242

6 а выход элемента И соединен с вторым входом третьего ключа.

Источники информации, принятые во внимание при экспертизе

1. Шлянлин В. М. Цифровые электроизмерительные приборы, Энергия, М., 1972, с. 191.

2. Авторское свидетельство Х 394936, 10 кл. Н 03 К 13/18, 1972.

660242

Редактор А. Шмелькин

Корректоры: Е. Осипова и А. Степанова

Составитель А. Титов

Типография, пр. Сапунова, 2

Заказ 826/10 Изд. № 280 Тираж 1059 Подписное

НПО Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5