Преобразователь средней частоты в код

Иллюстрации

Показать всеРеферат

ОП ИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 ц660245

Союз ьоьетскнх

Социалистических

Республнк

I (61) Дополнительное к авт. свид-ву (22) Заявлено 07.02,77 (21) 2450268/18-21 с присоединением заявки Л" (51) М. Кл.-"

Н 03К 13/20

G 06F 7/00 (43) Опубликовано 30.04.79. Бюллетень № 16 (53) УДК 621.317.681. .3 (088.8) ло делам изобретений н открытий (45) Дата опубликования описания 30.04.79 (72) Авторы изобретения

В. Ф. Бахмутский, Р. 3. Шептабань, В. И. Черепака и В. С. Якушев

Специальное конструкторское бюро микроэлектроники в приборостроении (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЪ СРЕДНЕЙ ЧАСТОТЫ В КОД

ГосУдарстеенный комитет (23) 11риоритет

Изобретение относится к области аналого-цифрового преобразования средней частоты и может быть использовано в технике преобразования низких и инфранизких частот с повышенной точностью и быстро- 5 действием.

Известен преобразователь средней частоты в код, содержащий устройство измерения отклонения частоты путем формирования временных интервалов обратно про- 10 порциональных известной и разностной частотам (1).

Недостаток такого преобразователя частот — зависимость погрешности от величины рассогласования. 15

Наиболее. близким по технической сущности к данному изобретению является преобразователь средней частоты в код, содержащий формирователь основной последовательности импульсов и формирователь основного измерительного интервала, выходы которых через ключ соединены с входами счетного регистра старших разрядов выходного кода, генератор опорной частоты, выход которого подключен к первому входу формирователя дополнительных последовательностей импульсов и к входу формирователя основного измерительного интервала, источник опорного напряжения, счетные регистры, выходы кото- Зо рых подключены к входам управления преобразователей проводимости в напряжение постоянного тока, реализованных, например, на операционном усилителе с обратной связью через образцовый резистор, к входу которого подключен кодоуправляемый резистор и преобразователь напряжения в число-импульсный код, на выходе которого включен счетный регистр младших разрядов выходного кода (2).

Недостатками такого преобразователя являются недостаточная точность и быстродействие.

Цель изобретения — повышение точности и быстродействия преобразования.

Указанная цель достигается тем, что в предлагаемый преобразователь средней частоты в код введены элемент антисовпадений, элемент равнозначности, счетчикраспределитель импульсов, коммутатор, сумматор напряжений, причем выходы формирователя основной последовательности импульсов и формирователя основного измерительного интервала через элемент антисовпадений соединены с входом счетчика-распределителя импульсов и первым входом элемента равнозначности, второй вход которого подключен к выходу формирователя основного измерительного интервала и первому входу

660245

3 управления формирователя дополнительных последовательностей импульсов, второй вход управления и вход «сброс» которого соединены соответственно с выходами элемента равнозначности и ключа, а выход подключен ко входам счетных регистров через коммутатор, причем входы управления коммутатора соединены с выходами счетчика-распределителя импульсов, а выход источника опорного напряжения через последовательно соединенные преобразователи проводимости в напряжение постоянного тока подключен к одному из входов сумматора напряжений, другие входы которого соединены порознь с выходами отдельных преобразователей проводимости в напряжение постоянного тока, а выход сумматора напряжений подключен ко входу преобразователя напряжения в число-импульсный код.

Кроме того, указанная цель достигается также и тем, что в преобразователе средней частоты в код формирователь дополнительных последовательностей импульсов содержит последовательно соединенные реверсивный счетчик, регистр памяти и блок сравнения кодов, соединенный с оперативным счетчиком, ключ и элемент равнозначности, причем первый вход реверсивного счетчика является входом «сброс» формирователя, а второй вход реверсивного счетчика соединен с выходом элемента равнозначности, являющегося выходом формирователя, первый вход элемента равнозначности является первым управляющим входом формирователя, а второй вход соединен с выходом блока сравнения кодов и входом «сброс» оперативного счетчика, первый вход которого является первым входом формирователя и подключен к первому входу ключа, а второй вход оперативного счетчика подключен к выходу ключа, второй вход которого является вторым управляющим входом формирователя и соединен со входом «перепись» регистра памяти.

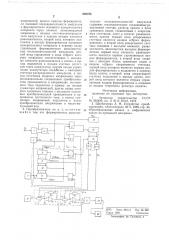

На чертеже показана функциональная электрическая схема преобразователя среди ей ч а стоты в код.

Преобразователь средней частоты в код содержит формирователь 1 основной последовательности импульсов (из периодов Т,, преобразуемой частоты f„) формирователь

2 основного измерительного интервала Т„ (из опорной частоты /О); формирователь 3 дополнительных последовательностей импульсов N> ... N из периодов Т„, ... Т„,. преобразуемой частоты, следующих за Т„; ключи 4-1, 4-2 (схемы совпадений); элемент 5 антисовпадений (НЕ-И); элементы равнозначности (ИЛИ) 6-1, 6-2, генератор 7 опорной частоты; реверсивный счет чик 8; регистр памяти 9; блок 10 сравнения кодов; оперативный счетчик 11; счетный регистр 12 старших разрядов выходного кода; счетчик-распределитель 13 импульсов, соотвст5

1О

25 зо

4О

55 оо

4 ствующих периодам Т,, ... Т,,; коммутатор

14; дополнительные счетные регистры

15-1 — 15-к импульсных последовательностей Л > ... N„„; источник 16 опорного напряжения U,; преобразователи 17-1 — 17-к проводимости в напряжение постоянного тока; кодоуправляемые резисторы (R> — R, )

18-1 — 18-к; образцовые резисторы (Ro)

19-1 — 19-к; операционные усилители 20-1—

20-к; сумматор 21 напряжений; преобразователь 22 напряжения в число-импульсный код; счетный регистр 23 младших разрядов выходного кода.

Преобразователь работает следующим образом.

В первом такте преобразования формируется основная последовательность импульсов N,-, — целое число периодов Т,-, за измерительный интервал Т„, накопленное в регистре 12. При этом каждым импульсом последовательности У,, сбрасывается накопленное в реверсивном счетчике 8 количество импульсов fo Т,, Второй такт начинается с поступления заднего фронта

Т„. При этом снимается сброс счетчика 8 и происходит (через элемент равнозначности

6-2) его реверсирование; одновременно через элемент равнозначности 6-1 поступает команда на перепись кода, соответствующего первому остаточному временному интервалу /,= T« — Х,., Т,-, из реверсивного счетчика 8 в регистр памяти 9. Далее код

/О сравнивается с кодом, накапливаемым в оперативном счетчике 11, и в момент их равенства блок 10 сравнения кодов выдает импульс, сбрасывающий оперативный счетчик 11 и выполняющий (через элемент равнозначности 6-2) очередное реверсирование счетчика 8. Тем самым, в пределах первого периода Т„., примыкающего к интервалу T„„, через элемент равнозначности

6-2 и коммутатор 14 на вход первого дополнительного регистра 15-1 поступают импульсы, соответствующие количеству интервалов to, укладывающихся в T„,, и в регистре 15-1 накапливается код Ni, определяемый из условия Т„, =У /о+1ь где / в второй остаточный временной интервал, выделенный по заднему фронту периода

Т„ или переднему фронту периода Т»,.

Соответствующий импульс поступает с выхода элемента антисовпадений 5 на вход счетчика-распределителя 13, переводя его из исходного состояния «1», в состояние

«2». При этом управляющий сигнал появляется на втором входе коммутатора 14, и следовательно, выход формирователя 3 дополнительных импульсных последовательностей подключается к дополнительному регистру 15-2. Тот же импульс через элемент равнозначности 6-1 выдает команду на перепись из реверсивного счетчика 8 в регистр памяти 9 кода второго остатка

Далее аналогично подсчитывается количество интервалов 1ь укладывающихся во

060245 втором после Т„периоде Т,„, причем соот1107 С !11 ;01711! li Ч ПС 70-11М Г1УЛЬСНЫ11 КОД ПОСТУliacT Ha вход дополнительного регистра 15-2 через элемент равнозначности 6-2; в момент оконча11ия периода Т,, в дополнительном 5 регистре 15-2 формируется код У2, соответствующий числу интервалов tl, укладывающихся в T,: T,, =N2tl+t2, где третий остаточный временный интервал.

В течение k следующих за Т„периодов вы- 10 рабатываются коды Ni ...,V„, соответствующис последовательным итерациям:

Т„= N,te+t, Т, Н1,+t2

Т< = — N,

Отсюда ясно, что в предлагаемом преобразователе общее время преобразования составляет Т„= Т„+кТ, тогда»ai, в известных преобразователях при том же ко20 л .гчестве итераций k и десятичном представлении общее время преобразования составляет Т„= Т„+10аТ, Факт«.ческий выигрыш в точности и быстродействии определяется сходимостью последовательных итераций. Если принять (в пренсбреженип быстрыми флуктуациями периода

Т,.) Т,,-, Т,.=... =T„„= Т... то из приведенных выше соотношений 110;Iучим рсзултат k-го приближения средней частоты f„.

N N,,+AN<< N<,+ где t

Nl ... N„a код ЛХ„выполняется следующим образом. Сопротивления кодоуправляемых резистров 18-1 — 18-к пропорциональным кодам Nl ... У„. соответственно, а выходные напряжения преобразователей

17-1 ... 17-к, благодаря их последовательному соединению, обратно пропорциональны произведениям Nl ...

U, =- — U, = i,U /<, 1V

U U О i2U R2 U

1< 1

2 1 О (1)«i,< U,I|2« 50

1 1 1 2 +<< где Х вЂ” коэффициент преобразования У1 в R;. При i

Анализ приведенного итерационного алгоритма показывает, что он сходится как

1/(к+2)!, где к — число итераций. В согоставлении со сходимостью известных итера- 60 ционных способов и устройств, которая составляет (при десятичном представлении)

l0 ", ясно, что для получения сравнимой точности в предложенном устройстве необходимо использовать большее количество 65

6 итераций. Например, в нониусном способе или способе умножения остаточных време;".ныx интервалов для получения точности

10 — - требуется две итерации, а в предложенном варианте — три итерации (1/5! =

= 1/120), соответственно для получения точности 10 †в известных устройствах необходимо выполнить три итерации, а в предложенном — четыре (1/б! = 1/720).

Б связи с более медленной сходимостью выигрыш в быстродействии при сравнимой точности несколько уменьшается. Например, если минимальной измеряемой частоте (/„) mii7 соответствует максимальный период

Т(Т,.) max, то выбирая Т„=10 (Т) max u принимая результирующую точность измерения (f,)miII разной 10 — "" получим общее время преобразования для известных устройств

T„== 10 (T „) гпах+20 (Т,.) max =30 (T„) max, а для предлагаемого устройства Т„=

=10(T«) max+3(T„) max=13(T„) max. Если (Т) max= lc(f„)min) =1 Тц, то указанный вь<игрыш в быстродействии (13с вместо

30с) оказывается весьма существенным.

При результирующей точности около 0,01% быстродействие предложенного и известных устройств составят (при тех же условиях) 14 с и 40 с соответственно.

В приведенном примере требованиякточности определения ЛУ„невысоки (порядка

1",о) и могут быть дополнительно снижены при увеличении Л „, однако при этом уменьшается и выигрыш в быстродействии.

Формула изобретения

1. Преобразователь средней частоты в код, содержащий формирователь основной последовательности импульсов и формирователь основного измерительного интервала, выходы которых через ключ соединены с входом счетного регистра старших разрядов выходного кода, генератор опорной частоты, выход которого подключен к первому входу формирователя дополнительных последовательностей импульсов и к входу формирователя основного измерительного интервала, источник опорного напряжения, счетные регистры, выходы которых подключены к входам управления преобразователей проводимости в напря>1 ение постоянного тока, реализованных, например, на операционном усилителе собратной связью чсрсз образцовый резистор, к входу которого подключен кодоуправлясмый резистор, и преобразователь напряжения в число-импульсный код, на выходе которого включен счетный регистр младш:x разрядов выходного кода, отл ич а ющи i;с,я тем, что, с целью повышения точбь1строде11ствня, B нег0 дополн11тсльно введены 3.70менты антнсовпадений, элемент равнозначности, счетчик-распределитель импульсов, коммутатор, сумматор

660245 тельных последовательностей импульсов содержит последовательно соединенные реверсивный счетчик, регистр памяти и блок сравнения кодов, соединенный с оперативным счетчиком, ключ и элемент равнозначности, причем первый вход реверсивного счетчика является входом «сброс» формирователя, а второй вход реверсивного счетчика соединен с выходом элемента равно1п значности, являющегося выходом формирователя, первый вход элемента равнозначности является первым управляющим входом формирователя, а второй вход соединен с выходом блока сравнения кодов и

15 входом «сброс» оперативного счетчика, первый вход которого является первым входом формирователя и подключен к первому входу ключа, а второй вход оперативного счетчика подключен к выходу ключа, второй вход которого является вторым управляющим входом формирователя и соединен со входом «перепись» регистра памяти>.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 392420, кл. G 01 К 23/10, 1973.

2. Щербаченко А. М. Устройство преобразования, «Автометрия» № 2, 1969, стр. 44, «Преобразование низких и инфранизких частот во временной интервал».

+so у ". г (п1- 1 ) напряхкепий, причем выходы формирователя основной последовательности импульсов и формирователя основного измерительного интервала чсрез элемент антисовпаденпй соединены с входом счетчика-распределителя импульсов и первым входом элемента равнозначности, второй вход которого подключен к выходу формирователя основного измерительного интервала и первому входу управления формирователя дополнительных последовательностей импульсов, второй вход управления и вход «сброс» которого соединены соответственно с выходами элемента равнозначности и ключа, а выход подключен к входам счетных рсгистров через коммутатор, причем входы управления коммутатора соединены с выходамч счетчика-распределителя импульсов, а выход источника опорного напряжения через последовательно соединенные преобразователи проводимости в напряжение постоянного тока подключен к одному из входов сумматора напряжений, другие входы которого соединены порознь с выходами отдельных преобразователей проводимости в напряжение постоянного тока, а выход сумматора напряжений подключен к входу преобразователя напряжения в число-импульсный код.

2. Преобразователь по п. 1, отл ич а юшийся тем, что формирователь дополниНПО Заказ 826, 13 Изд. № 280

Тираж 1059 Подписное

Типография, пр. Сапунова, 2