Многопороговый логический элемент четности

Иллюстрации

Показать всеРеферат

1, ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву В838490

Союз Советскнк

Соцнапнстнческнк

РЕСНИУбннК

<>660261 (51) М. Кл. (22) Заявлено 220377 (21) 2464919/18-21 с присоединением заявки №вЂ” (23) Приоритет

Н 03 К 19/12

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано3004.79. Бюллетень № 16 (53) УДК 621.374. (088.8) Дата опубликования описания 300479 (72) Авторы

ИЗОбрЕтЕНИя И. A Пальянов, В. И. Потапов и А. A. Дейлов (71) ЗаяянтЕЛЬ Омский политехнический институт (54 ) МНОГОПОРОГОВЫИ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

ЧЕТНОСТИ

Изобретение относится к области автоматики и вычислительной техники.

Известен многопороговый логичес- . кии элемент четности, содержащий линеиный сумматор из входных диодов и резисторнои матрицы, подключенный через разделительные диоды к резисторному делителю и многопороговому дискриминатору, выполненному в виде нескольких взаимосвязанных однопороговых дискриминаторов на двухвходовых элементах И-НЕ. В цепь обратной связи многопорогового элемента включен R-S-триггер и диодный токовый переключатель из двух последовательно включенных полупроводниковых диодов (1).

Недостатком известного многопорогового логического элемента является невысокая надежность.

Целью изобретения является повышение надежности.

Поставленная цель достигается тем, что в многопороговый логический элемент четности, содержащий линейный сумматор, состоящий из входных диодов и резисторной матрицы, подключенныи через разделительные диоды к резисторному делителю, соединенному с одними входами логических элементов И-НЕ, образующих многопороговый дискриминатор, второй вход каждого из которых соединен с выходом последующего логического элемента

И-НЕ, один вход R-S òðèããåðà соединен с выходом последнего логического элемента И-НК, а второй вход с источником стробирующего сигнала, а выход триггера подключен к одному из входов линейного сумматора, в него введен логический элемент И-НЕ, входы которого подключены к выходам однопороговых дискриминаторов, а выход через резистор соединен с катодами разделительных диодов.

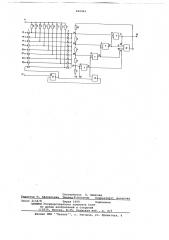

На чертеже приведена принципиальная схема многопорогового логического элемента четности.

Многопороговый логический элемент четности состоит из линейного сумматора, имеющего и основных и один,дополнительный вход, многопорогового дискриминатора, R-S-триггера и логического элемента И-НЕ. Линейный сумматор для каждого входа содержит попарно соединенные кремневые диоды

1 и 2. Каждая пара диодов в точках, объединяющих их аноды, через резисторы 3, управляющие весовыми коэффи660261 циентами по соответствующему входу, подключена к положительному полюсу источника питания 4.Катоды диодов 2 объединены и подсоединены через цепь последовательно roединенных суммирующих резисторов 5 к отрицательному полюсу источника питания б. Иноголороговый дискриминатор представляет собой несколько соединенных однопороговых дискриминаторов, выполненных на двухвходовых логических элементах И-НЕ 7. Вход 8 каждого однопо- l0 рогового дискриминатора соединен с соответствующим суммирующим резистором 5, развязывая ТеМ самым каждыи последующий однопороговый дискриминатор с большим значением порога )8 от предыдущего, а другой вход 9 элемента И-НЕ 7 подключен к выходу 10 элемента И-НЕ 7 последующего однопорогового дискриминатора.

Многопороговая логическая функ- 20 ция четности реализуется на выходе

11 элемента И-НЕ 7 однопорогового дискриминатора с минимальным порогом срабатывания. Вход 9 элемента H-HE 7 с максимальным порогом срабатывания соединен с положительным полюсом источника питания 12, а выход 10 подключен к единичному входу R-S-òðèãгера, выполненного на логических элементах И- 1Е 13. R-S80 триггера соединен с клеммой 14 стробирующих импульсов, а нулевой выход триггера подключен к катоду диода

1 дополнительного входа линейного сумматора. Выходы 10 и 11 однопороговых дискриминаторов соединены со входами 15 логического элемента 16, реализующего функцию И-НЕ. Выход 17 логического элемента 16 через резистор 18 подсоединен к отрицательному полюсу источника питания 6 через 40 цепь последовательно соединенных суммирующих резисторов 5. Клеммы 19 являются входами, а клемма — 20 выходом многопорогового логического элемента. 45

Рассмотрим работу, например, восьмивходового многопорогового логического элемента четности.

Значения весовых коэффициентов основных диодов линейного сумматора 80 равны единице, весовой коэффициент дополнительного входа равен 4, а значения порогов — 5, б, 7 и 8, Значение сопротивления резистора 18 выбрано таким образом, что при появлении на выходе логического элемента -16 высокого потенциала в цепи последовательно включенных суммирующих резисторов 5 составляет (0,25

0,3) I,,где I — ток, протекающий через весовой резистор 3, соответствующей весовому коэффициенту 1.

В исходном состоянии диоды Т, связанные- с входными клеммами 19, проводят ток от источника питания 4 через соответствующие резисторы 3.

Ток через резистор 3 от положительного полюса источника питания 4 и диод 2 дополнительного входа линейного сумматора поступает в цепь последовательно соединенных суммирующих резисторов 5 и далее к отрицательному полюсу источника питания б. На выходе 20 многопорогового логического элемента и выходах 10 элементов И-НЕ 7 в этом случае присутствует уровень логической единицы.

Входные сигналы в форме положительных потенциалов напряжения запирают в любых комбинациях диоды

Одновременно с поступлением входных сигналов в клемму 14 поступает стробирующий импульс напряжения с амплитудои, эквивалентной логической единице, и длительностью, равной длительности входных сигналов. Если положительный сигнал присутствует только на одном из входов 19 линейного сумматора, то соответствующий диод 4 запирается, а ток от источника питания 4 через резистор 3 и диод 2 переключается в цепь суммирующих резисторов 5, при этом потенциал точки 21 становится достаточным для появления на выходе 20 низкого уровня напряжения, соответствующего логическому нулю.

При наличии положительных потенциалов на двух входах 15 линейного сумматора соответствующие диоды 4 запираются, и ток через резистор

3 и диод 2 от источника питания 4 переключается в цепь суммирующих резисторов 5, при этом потенциал точки 22 становится достаточным для появления на выходе 10 элемента 7, связанного с точкой 22 соединения резисторов 5, низкого уровня напряжения. На выходе 20 многопорогового логического элемента в этом случае появляется высокий уровень напряжения.

При наличии положительных потенциалов на трех входах 19 линейного сумматора срабатывает однопороговый дискриминатор, имеющии значение порога Т = 7, вход которого связан с точкой 23 соединения суммирующих резисторов 5, при этом на выходе

20 многопорогового логического элемента устанавливается низкий уровень напряжения.

Из принципиальной схемы многопорогового логического элемента для реализации функции четности следует, что ток от источника питания 4 через резистор 3 и диод 2 дополнительного входа линеиного сумматора, в логическом отношении эквивалентный прибавлению к входному воздействию в

Х: х;ы, величины 4, протекает через суммирующие резисторы 5 до тех пор, пока R-S-триггер на элементах .

13 не изменит своего состояния на противоположное, т. е. когда на вхо660261 на е сигналы логиэлементов после ния переходных

i=1 на в

1 роцессов

ЭЗ 34 Э5 36

Формула изобретения ды 19 линейного сумматора поступит четыре или более положительных сигна— лов (когда сработает однопороговый дискриминатор, имеющий значение пороra T — 8, вход 8 которого связан с точкой 24 соединения суммирующих резисторов 5).

При этом на выходе однопорогового дискриминатора, имеющего значение порога Т вЂ” 8, устанавливается низкий потенциал, R-S-триггер изменяет свое состояние на противоположное. После этого ток через резистор 3 от источника питания 4 переключается в цепь диода 1 дополнительного входа линейного сумматора, При срабатывании любого из однопороговых дискриминаторов потенциал соответствующего входа 15 логического элемента 16 начинает понижаться, что приводит к повышению потенциала на выходе 17 логического элемента 16, а следовательно, к увеличению тока в цепи последовательно Соединенных суммирующих резисторов, что, в свою очередь, вызывает дальнейшее понижение потенциала на выходе срабатывающего однопорогового дискриминатора

7 и повышение потенциала на выходе

17 логического элемента 16.

Описанный процесс лавинообразно продолжается до тех пор, пока на выходе сработавшего однопорогового дискриминатора не установится потенциал логического нуля, а на выходе логического элемента 16 — потенциал логической единицы.

Таким образом, при срабатывании любого однопорогового дискриминатора в цепь последовательно соединенных сум- 65 а на выходе 20 многопорогового логического элемента для реализации функции четности устанавливается значение сигнала, опре еляемое входным воздействием X

;н >.

В целом функционированйе предлагаемого многопорогового логического элемента описывается следующей таблицеи.

Через 31, Э2, 33, Э4 в таблице обозначены выходы однопороговых дискриминаторов, имеющих значение Т = 5, Т = 6, Т = 7, Т = 8 соответственно, а через Э5, Э6 — единичный и нулевой выходы В-S-триггера.

1 1 1 1 1 0

0 1 1 1 1 О

1 0 1 1 1 О

О 1 О 1 1 0

1 1 1 1 0 1

0 1 1 1 О 1

1 О 1 1 О 1

О 1 О 1 0 1

1 0 1 О О 1 мирующих резисторов помимо тока из линейного сумматора поступает выходной ток логического элемента И-НЕ, приводящий к возникновению положительной обратнои связи и тем сажпл сужающии область неопределенности релейного элемента.

Иногопороговый логический элемент по авт. св. Р 538490, о т л и ч а юшийся тем, что, с целью повышения.надежности, в него введен логический элемент И-НЕ,,входы которого подключены к выходам однопороговых дискриминаторов, а выход через резистор соединен с катодами раздели-. тельньв; диодов.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

Р 538490, кл. Н 03 К 19/12, 24.11.75.

660261 !

Составитель 3. Мишкова

Ре акто И. A анасьева Техр И.Асталош Ко екто Г. Назарова

Заказ 2134/8 Тираж i059 Подписное

ЦНИИПИ ГосУдарственного комитета СССР . по делам изобретений и открытий

113035 Москва E-35 Ра шская наб. д. 4 5 филиал ППП Патент, r. Ужгород, ул. Проектная, 4