Устройство для автоматического измерения характеристик дискретного канала

Иллюстрации

Показать всеРеферат

lpga

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз. Советскнк

Соцыалыстыческнк

Реслублнк р11660276 (61) Дополнительное к авт, свид-Bge535743 (22) Заявлено 22,11,76(21) 2422130!18 09 с присоединением заявки № (5l) M. Кл.

Н 04 В 3/46

Государственный комитет

СС C P по делам изобретений и открытий (23) Приоритет

Опубликовано 3004,79. Бюллетень ¹ 16 (53) УДК 621. 391 .833 (088.8) Дата опубликования описания 300479 (72) Авторы изобретения

О.C. Когновицкий и A.Â. Чулкин (71) Заявитель. Ленинградский электротехнический институт связи им. проф.М.A. Бонч-Бруевича (54) УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ИЗМЕРЕНИЯ

ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА

Изобретение относится к радиотехнике и может использоваться для выявления потоков ошибок и сбоев синхронизации в дискретных каналах связи, а также для измерения величины фазового рассогласования между прошедшей канал связи испытательной псевдослучайной последовательностью сигналов и эталонной последовательностью.

По основному авт.св. Р 535743 известно устройство для автоматического измерения характеристик дискретного канала, содержащее на входе основную и дополнительную схемы сравнения, причем к выходу основной схемы сравнения подключен основной регистр сдвига с первым сумматором в цепи обратной связи, выходы разрядов основного регистра сдвига подключены к входам соответствующих схем совпадения через сумматоры, к вторым входам которых и к входам дешифратора подключены выходы соответствующих разрядов дополнительного регистра сдвига, в цепи обратной связи которого включен второй сумматор, выход которого через дополнительную схему сравнения и выход дешифратора непос. редственно подключены к входу счетчика, к другому входу которого под- ЗО ключен выход дополнительной схемы сравнения через первый инвертор, а также элемент ИЛИ с вторым инвертором на выходе, две дополнительные схемы совпадения и динамический триггер, при этом выход счетчика подключен к одному из входов первой дополнительной схемы совпадения, к другому входу которой подключены выходы сумматоров через элемент ИЛИ, а выход первой дополнительной схемы совпадения подключен через схемы совпадения к входам установки первых m разрядов дополнительного регистра сдвига, где т — число разрядов основного регистра сдвига, и непосредственно к входу запуска динамического триггера, к входу сброса которого подключен выход второго инвертора, а выход динамического триггера подключен к цепи тактовых импульсов ос— новного регистра сдвига, кроме того, выходы счетчика и второго инвертора через вторую дополнительную схему совпадения подключен - к цепи сброса . дополнительного регистра сдвига.

Однако известное устройство под воздействием помех, действjioLlHx в канале связи, может ложно определять

660276 потоки сбоев фазы и измерять величину фазового рассогласования. (ель изобретения — повышение достоверности измерения.

25 бО

Для этого в устройство для авто- 5 матического измерения характеристик дискретного канала, содержащее на входе основную и дополнительную схемы сравнения, причем к выходу основной схемы сравнения подключен основ в 10 ной регистр сдвига с первым сумматором в цепи обратной связи, выходы разрядов основного регистра сдвига . подключены к входам соответствующих схем совпадения через сумматоры, к вторым входам которых и к входам дешифратора подключены выходы соответствующих разрядов дополнительного регистра сдвига, в цепи обратной связи которого включен второй сумматор, выход которого через дополнительную схему сравнения и выход дешифратора непосредственно подключены к входу счетчика, к другому входу которого подключен выход дополнительной схемы сравнения через первый инвертор, а также элемент ИЛИ с вторым инвертором на выходе, две дополнительные схемы совпадения и динамический триггер, при этом выход счетчика подключен к одному из входов первой до- ЗО полнительной схемы совладения, к другому входу. которой подключены выходы сумматоров через элемент ИЛИ, а выход первой дополнительной схемы совпадения подключен через схемы совпаде- 35 ния к входам установки первых m разрядов дополнительного регистра сдвига, где m — число разрядов основного регистра сдвига, и непосредственно к входу запуска динамического триг- 40 гера, к входу сброса которого подключен выход второго инвертора, а выход динамического триггера подключен к цепи тактовых импульсов основного регистра сдвига, кроме того, выходы счетчика и второго инвертора через вторую дополнительную схему совпадения подключены к цепи сброса дополнительного регистра сдвига, введен блок запрета счета, при этом выход блока запрета счета подключен к входу счетчика, на вход Стирание блока запрета счета подан сигнал с выхода дискретного канала, с которого подан сигнал и на вход Обнуление блока запрета счета, кроме 55 того, блок запрета счета выполнен из последовательно соединенных ждущего мультивибратора и дополнительного элемента ИЛИ, при этом вход ждущего мультивибратора является входом Стирание блока запрета счета, входом Обнуление которого является другой вход дополнительного элемента ИЛИ, выход которого является выходом блока запрета счета.

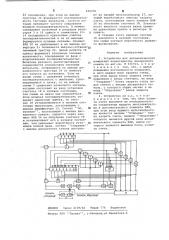

Па чертеже приведена структурная электрическая схема лредложенного устройства.

Устройство для автоматического измерения характеристик дискретного канала содержит основную 1 и дополнительную 2 схемы сравнения, основной регистр 3 сдвига, первый сумматор

4 схемы 5-9 совпадения, сумматоры

10-14, 15, дополнительный регистр 16 сдвига, второй сумматор 17, счетчик 18, первый инвертбр

19, элемент ИЛИ 20, второй инвертор

21, дополнительные схемы 22 и 23 совпадения, динамический триггер 24, блок 25 запрета счета, который состоит из элемента ИЛИ 26 и ждущего мультивибратора 27.

Устройство работает следующим образом.

Двоичная последовательность с информационного выхода дискретного ка— нала поступает на вход схемы 1 сравнения, на второй вход которой через сумматор 4 поступает эталонная последовательность, формируемая регистром 3 сдвига. Если ошибки в двоичной последовательности отсутствуют, а сравниваемые с выхода канала и эталонная последовательности находятся не в фазе по циклу, то двоичная последовательность с выхода схемы 1 сравнения продвигается по разрядам регистра 16 сдвига, сигналы с разрядов обратной связи поступают на входы сумматора 17 и c его выхода — на вход дополнительной схемы 2 сравнения.

Так как последовательности, поступающие при этом на входы схемы 2 сравнения, совпадают по виду и фазе, то на ее выходе имеются нулевые сигналы, которые далее поступают на вход счетчика 18 через инвертор 19.

При заполнении счетчика 18 сигнал с его выхода поступает одновременно на входы дополнительных схем 22 и 23 совпадения. Па входы сумматоров 10-14 поступают участки последовательностей, которые не совпадают по фазе, вследствие чего на выходе хотя бы одного из сумматоров 10 — 14 появляется единичный сигнал, который через элемент ИЛИ 20 поступает одновременно на входы инвертора 21 и схемы 22 совпадения.

Таким образом, в момент срабатывания счетчика 18 на выходе схемы 22 совпадения появляется сигнал, поступающий на первые входы схем 5-9 совпадения, следовательно, результат поэлементного сложения последовательностей с выхода сумматоров 10-14 через схемы 5-9 совпадения поступает на входы установки первых ю разрядов регистра 16 сдвига. Автоматическое устранение сбоя фазы по циклу производится динамическим триггером 24, запускаемым выходным сигналом схемы

660

Формула изобретения

ЦНИИПИ Заказ 2139/10 Тираж 774 Подписное

Филиал ППП Патент, г.ужгород, ул. Проектная, 4

22 совпадения, при этом на выходе триггера 24 формируется последовательность тактовых импульсов, частота которых превышает частоту следования входной последовательности. В момент совпадения состояний m разрядов регистров 3 и 16 сдвига в сумматорах 1014 складываются одинаковые участки последовательностей и на их выходах формируются нулевые сигналы. Элемент

ИЛИ 20 не срабатывает и на выходе инвертора 21 появляется импульс,останав-10 ливающий триггер 24. Далее регистр 16 сдвига формирует эталонную последовательность, совпадающую по фазе с испытательной последовательностью.

Величина фазового рассогласования 15 определяется количеством тактовых импульсов, появившихся на выходе динамического триггера 24 от момента его запуска до остановки. Если на входе схемы 1 сравнения появилась последовательность с ошибками, группирующимися в пачки, то на выходе схемы 2 сравнения появляются сигналы, которые поступают на вход установки счетчика 18 в нулевое состояние, тем самым не давая ему заполняться.

Если входная последовательность содержит одиночные ошибки, то счетчик 18 устанавливается в нулевое состояние импульсами, поступающими с выхода дешифратора 15. Сигнал Об- 30 нуление, поступающий с выхода дискретного канала, подается через элемент ИЛИ 26 на обнуление счетчика 18 и устанавливает его в нулевое состояние, чем уменьшает вероятность уста- 35 новки ложной фазы. Сигнал Стирание с выхода дискретного канала поступа276 6 ет на ждущий мультивибратор 27, который вырабатывает импульс запрета счета, поступающий через элемент ИЛИ

26 на обнуление счетчика 18. Длительность импульса запрета равна времени циркуляции ошибок в регистре 16 сдвига.

В течение этого времени счетчик

18 находится в нулевом состоянии, тем самым улучшая вероятность должного фазирования.

1. Устройство для автоматического измерения характеристик дискретного канала по авт.св. Р 535743, о т л ич а ю щ е е с я тем, что, с целью повышения достоверности измерения, в него введен блок запрета счета, при этом выход блока запрета счета подключен к входу счетчика, на вход Стирание блока запрета счета подан сигнал с выхода дискретного канала, с которого подан сигнал и на вход Обнуление блока запрета счета.

2. Устройство по п.1, о т л ич а ю щ е е с я тем, что блок запре-та счета выполнен из последовательно соединенных ждущего мультивибратора и дополнительного элемента ИЛИ, при этом вход ждущего мультивибратора является входом Стирание блока запрета счета, входом Обнуление которого является другой вход дополнительного элемента ИЛИ, выход которого является выходом блока запрета счета.