Устройство селективного вызова

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советским

Социалистических

Республик («) 660302 Ж . ь (61) Дополнительное к авт. свид-ву— (22) Заявлено 1409.77 (21) 2526186/18-09 с присоединением заявки №вЂ” (23) Приоритет(61) М. Кл.

Н 04 С4 5/20

Государственный комитет

СССР но делам изобретений и открытий

Опубликовано 30.04.79. Бюллетень №16 (53) УДК621. 395..632 (088.8) Дата опубликования описания 30.04.79 (72) Авторы изобретения

Г.И.Азаров, A.A.Ìàëþ÷êîâ, A.À.Oñoêèí, Ф.М.Коробейников и Ю.Н.Манякин

Pl) Заявитель (54) УСТРОЙСТВО СЕЛЕКТИВНОГО ВЫЗОВА

Изобретение относится к радиосвязи и может использоваться для обеспечения избирательного вызова корреспондентов,работающих в одной радиосети.

Известно устройство сепективного вызова, содержащее преобразователь сигнала, синхрогенератор, первый и второй делители частоты, шифратор, управляющий блок, блок сравнения, интегратор, элемент И и блок индикации о вызова, причем выход преобразователя сигнала соединен с первым входом блока сравнения, первый и второй выходы синхрогенератора соединены соответствейно с первым входом первого делителя частоты и с входом второго делителя частоты, а выход интегратора соединен с первым входом блока индикации вызова (1).

Однако при наличии в радиосети нескольких корреспондентов и одновременной передаче ими вызывных сигналов из-за наложения последних вероятность сбоя вызова оказывается сравнительно большой. Я5

Целью изобретения является уменьшение вероятности сбоя вызова. для этого в устройство селективного вызова, содержащее преобразователь сигнала, синхрогенератор, первый и второй делители частоты, шифратор, управляющий блок, блок сравнения, интегратор, элемент И и блок индикации вызова, причем выход преобразователя сигнала соединен с первым входом блока сравнения, первый и второй выходы синхрогенератора соединены соответственно с первым входом .первого делителя частоты и с входом второго делителя частоты, а выход интегратора соединен с первым входом блока индикации вызова, введены согласующий блок, блок син-. хронизации, ограничитель амплитуды, первый и второй нелинейные цифровые фильтры, первый и второй формирователи импульсов и первый и второй блоки выравнивания амплитуды, причем выход согласующего блока соединен с первым входом преобразователя сигнала и входом ограничителя амплитуды, первый и второй выходы которого соединены соответственно с информационными входами первого и второго нелинейных цифровых фильтров, причем управляющие входы первого и второго нелинейных цифровых фильтров соединены соответственно с выходами первого и второго формирователей импульсов, входы которых соединены с третьим

660302 выходом генератора синхроимпульсов, при этом выходы первого и второго нелинейных цифровых фильтров соединены соответственно с ийформационными входами первого и второго выравнивателей амплитуды, управляющие входы которых соединены соответственно с первым и вторым выходами второго делителя частоты, а выходы первого и второго выравнивателей амплитуды соединены соответственно с первым и вторым входами элемента И, выход 10 которого соединен с входом интегратора, выход которого соединен с первым входом управляющего блока, второй вход которого соединен с выходом шифратора, вход которого соеди- 15 нен с выходом первого делителя частоты, второй вход которого соединен с выходом блока синхронизации, вход которого соединен с выходом преобразователя сигнала, второй выход которого 0 соединен с первым выходом управляющего блока, второй вход которого соединен с вторым входом блока сравнения, а выход блока сравнения соединен с вторым входом блока индикации вызова.

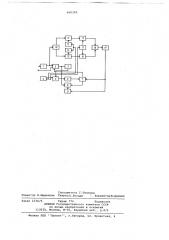

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство селективного вызова содержит согласующий блок 1, преобразователь 2 сигнала, блок 3 синхронизации, синхрогенератор 4, первый делитель 5 частоты, шифратор б, управляющий блок 7, блок 8 сравнения, блок

9 индикации вызова, ограничитель 10 амплитуды, первый 11 и второй 12 нелинейные цифровые фильтры, первый 13 и второй 14 формирователи импульсов, первый 15 и второй 16 блоки выравнивания амплитуды, второй делитель 17 40 частоты, элемент И 18 и интегратор 19.

Устройство работает следующим образом.

Устройство работает как в режиме приема, так и в режиме передачи. 45

Управление режимами работы осуществляется с помощью управляющего блока 7.

В режиме приема сигналы с выхода радиостанции в виде последовательнос- 50 тей двух тональных частот, одна из которых соответствует нулевой посылке, а вторая — единичной, поступают через согласующий блок 1 одновременно на вход преобразователя 2 сигнала и ограничителя 10. Преобразователь 2 формирует из них прямоугольные импульсы. Из импульсов в соответствии с, поступающей информацией образуются определенные последовательности импульсов, которые поступают на входы блока 8 сравнения и блока 3 синхронизации. Последний выделяет из всего потока информации моменты смены полярности рабочих импульсов и формирует в указанные моменты однополярные ймпульсы, которые подаются на второй вход делителя 5 частоты, на первый вход которого поступают управляющие импульсы с первого выхода синхрогенератора 4.Этим самым производится подстройка фазы управляющих импульсов на выходе делителя 5 частоты.

Управляющие импульсы с выхода делителя 5 частоты подаются на вход шифратора б (который в режиме приема работает как дешифратор) и обеспечивают продвижение информации в его регистре. Импульсные последовательности с выхода шифратора б через управляющий блок 7 поступают на второй вход блока 8 сравнения, который производит сравнение принятого кода с кодом, соответствующим данной радиостанции. В случае совпадения этих кодов с выхода блока 8 сравнения подается сигнал в блок 9 индикации о вызове данной радиостанции.

В режиме передачи кодовая последовательность импульсов, соответствующая адресу вызываемой радиостанции, с выхода шифратора б через управляющий .блок / поступает в преобразователь 2.

Управляющий блок 7 в этом случае обеспечивает перевод преобразователя 2 в режим манипуляции и подключение к нему выхода шифратора 6. С выхода преобразователя 2 сигналы в виде последовательности двух тональных частот подаются на вход радиостанции.

При этом устройство одновременно с анализом принимаемой информации на соответствие адресу данной радиостанции обеспечивает анализ радиоканала На занятость следующим образом.

Ограниченные по амплитуде сигналы с выхода ограничителя 10 поступают на входы нелинейных цифровых фильтров 11, 12, каждый из которых представляет собой логическую цепь, отклик которой на входной сигнал принимает два значения: 1, если длительность текущего периода входного сигнала находится в определенных, обусловленных параметрами этой цепи пределах, и 0, если длительность текущего периода входного сигнала выходит за эти пределы.

Напряжение синхрогенератора 4 с третьего его выхода поступает в формирователи 13, 14, которые формируют импульсы подставок. Положение импульсов подставок строго фиксировано относительно импульсов опроса и определяет максимальную частотуГ,,полосы пропускания фильтров 11, 12,длительность их определяет минимальную частоту Г „„полосы пропускания фильтров

11, 12.

При заданной длительности импульсов подставок и их определенном фиксированном временном положении относительно импульсов опроса данному конкретному значению частоты на входах фильтров 11, 12 Р„ (обозначающей едибб 0302

Формула изобретения ничную посылку) и F (обозначающей нулевую посылку) соответствует наличие импульсов на выходе одного из нелинейных цифровых фильтров 11, 12 и отсутствие их на выходе другого.

Ввиду различия средних частот (F, F ) T o 11, 12 временной вес импульсов на .их выходах различен. Блоки 15, 1б, управляемые через делитель 17 частоты синхрогенератором 4, выравнивают результат воздействия выходных импульсов фильтров

11, 12 на интегратор 19,на который они поступают через элемент И 18.

Постоянная времени Г интегратора

19 выбирается из условия c.(с где, — время, необходимое для полного декодирования адреса. В случае Занятости радиосети (передачи вызова каким-либо корреспондентом) с выхода интегратора 19 через интервалы времени, равные, в управляющий блок 7 выдается сигнал запрета, блокирующий работу устройства в режиме передачи, и в блок 9 индикации выдается сигнал Занятости . Если по истечении времени ; в управляющий блок 7 с выхода интегратора 19 не поступает сигнал запрета, то происходит автоматическая разблокировка устройства и оно может работать в режиме передачи.

Вероятность сбоя при использовании предложенного устройства на два порядка ниже, чем при использовании известного устройства.

Устройство селективного вызова, содержащее преобразователь сигнала, синхрогенератор, первый и второй делители частоты, шифратор, управляющий блок, блок сравнения, интегратор, элемент И и блок индикации вызова, причем выход преобразователя сигнала соединен с первым входом блока сравнения, первый и второй выходы синхрогенератора соединены соответственно с первым входом первого делителя частоты и с входом второго делителя частоты, а выход интегратора соединен с первым входом блока индика5

l0

50 ции вызова, о т л и ч а ю щ е е с я тем, что, с целью уменьшения вероят- ности сбоя вызова, в него введены согласующий блок, блок синхронизации, ограничитель амплитуды, первый и второй нелинейные цифровые фильтры, первый и второй формирователи импульсов и первый и второй блоки выравнивания амплитуды, причем выход согласующего блока соединен с первым входом преобразователя сигнала и входом ограничителя амплитуды, первый и второй выходы которого соединены соответственно с информационными входами первого и второго нелинейных цифровых фильтров, причем управляющие входы первого и второго нелинейных цифровых фильтров соединены соответственно с выходами первого и второго формирователей импульсов, входы которых соединены с третьим выходом генератора синхроимпульсов, при этом выходы первого и второго нелинейных цифровых фильтров соединены соответственно с информационными входами первого и второго выравнивателей амплитуды, управляющие входы которых соединены соответственно с первым и вторым выходами второго делителя частоты,а выходы первого и второго выравнивателей амплитуды соединены соответственно с первым и вторым входами элемента И, выход которого соединен с входом интегратора, выход которого соединен с первым входом управляющего блока, второй вход которого соединен с выходом шифратора, вход которого соединен с выходом первого делителя частоты, второй вход которого соединен с выходом блока синхронизации, вход которого соединен с выходом преобразователя сигнала, второй выход которого соединен с первым выходом управляющего блока, второй вход которого соединен с вторым входом блока сравнения, а выход блока сравнения соединен с вторым входом бло1 а индикации вызова.

Источники информации, принятые во внимание при экспертизе

1. Заявка Р 2409146/09, кл. Н 04 Q 5/00, 1977, по которой принято решение о выдаче авторского свидетельства.

660302

Составитель Г.Теплова

Редактор К.Щадилова ТехредЛ.Богдан КорректорМ.Демчик

Заказ 2136/9 Тираж 774 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, r.Óæãoðoä, ул. Проектная, 4