Стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

т

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ («) 661528

Союз Советских

Социалистмцеских

Республик

«Ьу »

4 1 Pô 1Н р, (61) Дополнительное к авт. свид-ву— (22) Заявлено 24.05.77 (21) 2489270/24-07 с присоединением заявки №вЂ” (23) Приоритет— (51) М.К .

G05 F 1/56

Н 02 М 3/335

Государственный комитет

СССР по делам изобретений и открытий (53) УДК621.316. .722.1 (088.8) Опубликовано 05.05.79. Бюллетень № 17

Дата опубликования описания 15.05.79 (72) Авторы изобретения

М. В. Колоколов, Л. М. Зарецкий и Н. П. Изакова (71) Заявитель (54) СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ

Изобретение относится к электротехнике и предназначено для использования в ка= честве вторичного источника электропитания аппаратуры различного назначения, Известен стабилизатор напряжения, содержащий силовую часть (переключающие 5 транзисторы, выходной трансформатор, выпрямитель, фильтр), узел управления, датчики тока и регулятор напряжения с узлом вольт-секундного выравнивания (1).

Недостатком известного стабилизатора является низкий КПД и сложность схемы.

Наиболее близким техническим решением к изобретению является стабилизатор постоянного напряжения, содержащий силовой блок, выполненный на базе полупроводникового инвертора с переключающими транзисторами и выходным трансформатором, датчик тока, выполненный в виде трансформатора тока, через одну часть первичной цепи которого, выполненной в виде отдельной обмотки, вторичная обмотка выходного трансформатора подключена к входу выпрямителя с фильтром, выходом подсоединенного к выходам для подключения нагрузки, через другую часть первичной цепи трансформатора тока первичная цепь выходного транс2 форматора включена между коллекторами переключающих транзисторов полупроводникового инвертора, а вторичная. цепь трансформатора тока соединена с нагрузочным резистором, управляющий блок, состоящий из задающего генератора, выход которого соединен с входом счетного триггера, выходами подключенного к первым входам двух схем совпадения, выходы которых соединены с базами переключающих транзисторов, и регулятор напряжения с блоком вольт-секундного выравнивания, с усилителем сигнала ошибки, входом, подключенным к одному из выводов для подключения нагрузки, делителем напряжения на резисторах, двумя пиковыми детекторами, входы которых соединены с нагрузочным резистором, а выходы подсоединены к суммирующему резистору, и широтно-импульсный модулятор, первым входом соединенный с выходом задающего генератора (2) .

Недостатком такого стабилизатора постоянного напряжения является низкая точность вольт-секундного выравнивания из-за инерционности схемы.

Целью изобретения является повышение

661528

5О

55 точности вольт-секундного выравнивания стабилизатора постоянного напряжения.

Для этого в стабилизаторе постоянного напряжения, содержащем силовой блок, выполненный на базе полупроводникового инвертора с переключающими транзисторами и выходным трансформатором, датчик тока, выполненный в виде трансформатора тока, через одну часть первичной цепи которого, выполненной в виде отдельной обмотки, вторичная обмотка выходного трансформатора подключена к входу выпрямителя с фильтром, выходом подсоединенного к выходам для подключения нагрузки, через другую часть первичной цепи трансформатора тока первичная цепь выходного трансформатора включена между коллекторами . переключающих транзисторов полупроводникового инвертора, а вторичная цепь трансформатора тока соединена с нагрузочным резистором, управляющий блок, состоящий из задающего генератора, выход которого соединен с входом счетного триггера, выходами подключенного к первым входам двух схем совпадения, выходы которых соединены с базами переключающих транзисторов, и регулятор напряжения с блоком вольт-секундного выравнивания, с усилителем сигнала ошибки, выходом подключенным к одному из выводов для подключения нагрузки, делителем напряжения на резисторах, двумя пиковыми детекторами, входы которых соединены с нагрузочным резистором, а выходы подсоединены к суммирующему резистору, и широтно-импульсный модулятор, первым входом соединенный с выходом задающего генератора, в регулятор напряжения введен делитель из четырех резисторов и дополнительный широтно-импульсный модулятор, выход которого соединен со вторым входом одной из схем совпадения, первый вход соединен с выходом задающего генератора и первым входом основного широтно-импульсного модулятора, а второй вход соединен.с первым выводом первого резистора делителя напряжения, вторым выводом подсоединенного к общей точке схемы стабилизатора и вторым выводом второго резистора делителя напряжения, первый вывод которого соединен с выходом усилителя сигнала ошибки и вторым выводом третьего резистора делителя напряжения, первый вывод которого соединен со вторым входом основного широтно-импульсного модулятора, выходом подсоединенного ко второму входу второй схемы совпадения, и вторым выводом четвертого резистора делителя напряжения, первый вывод которого соединен со средней точкой суммирующего резистора.

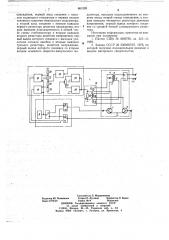

На чертеже представлена функциональная схема стабилизатора постоянного напряжения.

Стабилизатор постоянного найряжения содержит силовой блок, выполненный на базе полупроводникового инвертора с переклю15

40 чающими транзисторами 1, 2 и выходным трансформатором 3 с первичными обмотками

4, 5 и вторичной обмоткой 6,.один вывод которой соединен с первым выходным выводом выпрямителя 7 с фильтром, выходом подсоединенного к выводам для подключения нагрузки; управляющий блок, состоящий из задающего .генератора 8, выход которого соединен с входом счетного триггера 9, выходами подсоединенного к первым входам схем совпадения 10 и 11; датчик тока, выполненный в виде трансформатора тока 12 с первичными обмотками 13 и 14, компенсирующей обмоткой 15 и выходной обмоткой 16 с нагрузочным резистором 17; регулятор напряжения, состоящий из двух широтно-импульсных модуляторов 18 и 19, первые входы которых соединены с выходом задающего генератора 8, а выходы подсоединены ко вторым входам схем совпадения 11 и 10 соответственно, делителя напряжения из четырех резисторов 20, 21, 22, 23, усилителя сигнала 24 ошибки, пиковых детекторов 25 и 26 разной полярности, входы которых соединены с нагрузочным резистором 17, а между выходами включен суммирующий резистор 27, средняя точка которого соединена с одним из выводов резистора 23, второй вывод резистора

23 соединен со вторым входом широтно-импульсного модулятора 19 и одним из выводов резистора 22, второй вывод резистора 22 соединен с выходом усилителя сигнала ошибки

24 и одним из выводов резистора 21, второй вывод резистора 21 соединен со вторым входом широтно-импульсного модулятора 18 и одним из выводов резистора 20, второй вывод которого соединен с общей точкой схемы.

Стабилизатор напряжения работает следующим образом.

При включении стабилизатора импульсы с удвоенной частотой преобразования с задающего генератора 8 поступают на вход счетного триггера 9 и на первые входы широтноимпульсных модуляторов 18 и 19. С выходов счетного триггера 9 прямоугольные импульсы со скважностью g =2 поступают на входы схемы 10 и 11 совпадения, которые управляют переключающими транзисторами 1 и 2.

Выходное напряжение стабилизатора сравнивается с опорным и усиливается усилителем сигнала 24 ошибки. Усиленный сигнал ошибки поступает в точку соединения резисторов 22 и 21. Резисторы 20, 21 и 22, 23 образуют два идентичных делителя напряжения.

При увеличении (уменьшении) выходного напряжения на выходе стабилизатора увеличивается (уменьшается) напряжение сигнала ошибки на выходе усилителя сигнала ошибки. Это напряжение, поделенное двумя идентичными делителями на резисторах 20, 21 и 22, 23, подается на входы двух идентичных широтно-импульсных модуляторов

18 и 19. Соответственно уменьшается (увели661528 увеличивается. Таким образом происходит выравнивание -по длительности импульсов напряжения, прикладываемых к первичным обмоткам 4 и 5 силового трансформатора 3, 5. т. е. вольт-секундное выравнивание.

- --Повышение точности вольт-секундного выравнивания позволяет повысить надежность стабилизатора и расширить диапазон регулирования. Это позволяет использовать данный стабилизатор в условиях больших по сравнению с прототипом изменений входных напряжений и токов нагрузки, что расширяет функциональные возможности стабилизатора.

Данный стабилизатор может быть с ус15 пехом использован в аппаратуре дальней связи с частотным или временным уплотнением и другой аппаратуре, требующей высоконадежного источника электропитания, работающего в условиях значительных изменений входного напряжения и токов нагруз20

Формула изобретения чивается) длительность импульсов на выходах широтно-импульсных модуляторов, а также импульсов, подаваемых со схем 10 и 11 совпадения на переключающие транзисторы

1 и 2, что приводит к уменьшению (увеличению) уровня выходного напряжения стабилизатора и приведению его до номинала. Таким образом осуществляется стабилизация выходного напряжения стабилизатора.

В случае возникновения вольт-секундной асимметрии, вызванной, например, различным временем рассасывания неосновных носителей в переключающих транзисторах и 2, происходит увеличение тока намагничивания выходного трансформатора, возрастание коллекторного тока одного из переключающих транзисторов 1 или 2, появление на выходах пиковых детекторов 25 и 26 разных по абсолютчому значению напряжений. При этом напряжение в средней точке суммирующего резистора 27 становится отличным от нуля, а полярность этого напряжения указывает., в каком из полупериодов происходит увеличение амплитуды тока намагничивания, Благодаря тому, что выходное сопротивление усилителя сигнала ошибки мало и может быть доведено до сколь угодно малой величины, напряжение на резисторе 20, пропорциональное величине сигнала ошибки, не зависит от величины напряжения на средней точке суммируюшего резистора 27, являющегося сигналом асимметрии. В свою очередь, напряжение в точке соединения резисторов

22 14 23 оказывается равным сумме двух напряжений: напряжения сигнала ошибки, равного напряжению в точке соединения резисторов 20 и 2! и напряжению сигнала асимметрии. Это напряжение складывается с напряжением сигнала ошибки на делителе, состоящем из резисторов 22 и 23 таким образом, что напряжение в точке соединения этих резисторов становится меньше или больше напряжения в точке соединения резисторов 21 и 22 на величину, пропорциональную сигналу асимметрии. При этом на вход широтно-импульсного модулятора 18 подается напряжение, пропорциональное только сигналу ошибки, а на вход широтно-импульсного модулятора 19 подается напряжение, пропорциональное алгебраической сумме сигналов ошибки и асимметрии. На выходе широтноимпульсного модулятора 18 длительность импульса остается такой же, как до возникновения вольт-секундной асимметрии, а на выходе широтно-импульсного модулятора 19 длительность импульса уменьшается или увеличивается, в зависимости от того, в каком из полупериодов произошло увеличение тока намагничивания трансформатора 3, вызыванное, например, разным временем рассасывания неосновных носителей в переключающих транзисторах 1 и 2. Длительность импульса на выходе схемы 10 совпадения, вход которой соединен с выходом широтно-импульсного модулятора 19, тоже уменьшается или

4О

Стабилизатор постоянного напряжения, содержащий силовой блок, выполненный на, базе полупроводникового инвертора с переключающими транзисторами и выходным трансформатором, датчик тока, выполненный в виде трансформатора тока, через одну часть первичной цепи которого, выполненной в виде отдельной обмотки, вторичная обмотка выходного трансформатора подключена к входу выпрямителя с фильтром, выходом подсоединенного к выводам для подключения нагрузки, через другую часть первичной цепи трансформатора тока первичная цепь выходного трансформатора включена между коллекторами переключающих транзисторов полупроводникового инвертора, а вторичная цепь трансформатора тока соединена с нагрузочным резистором, управляюший блок, состоящий из задающего генератора, выход которого соединен с входом счетного триггера, выходами подключенного к первым входам и двух схем совпадения, выходы которых соединены с базами переключаюших транзисторов,. и регулятор напряжения с блоком вольт-секундного выравнивания, с усилителем сигнала ошибки, входом, подключенным к одному из выводов для подключения нагрузки, делителем напряжения на резисторах, двумя пиковыми детекторами, входы которых соединены с нагрузочным резистором, а выходы подсоединены к суммируюшему резистору, и широтно-импульсный модулятор, первым входом соединенный с выходом задающего генератора, отличающийся тем, что, с целью повышения точности вольт-секундного выравнивания, в регулятор напряжения введен делитель из четырех резисторов и дополнительный широтно-импульсный модулятор, выход которого соединен со вторым входом одной из схем

661528

7 совпадения, первый вход соединен с выхо. дом задающего генератора и первым входом основного широтно-импульсного модулятора, а второй вход соединен с первым выводом первого резистора делителя напряжения, вторым выводом подсоединенного к общей точке схемы стабилизатора и вторым выводом второго резистора делителя напряжения, первый вывод которого соединен с выходом усилителя сигнала ошибки и вторым выводом третьего резистора, делителя напряжения, первый выход которого соедийен со вторым входом основного широтно-импульсного мо8 дулятора, выходом подсоединенного ко второму входу второй схемы совпадения, и вторым выводом четвертого резистора делителя напряжения, первый вывод которого соединен со средней точкой суммирующего резистора.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3660750, кл. 321 вЂ, 10 1969

2. Заявка СССР № 2362607/07, 1976, по которой получено положительное решение о выдаче авторского свидетельства.

Редактор Ю. Челюканов

Заказ 2474/50!

Составитель Л. Мордвинкина

Техред О. Луговая Корректор О, Билак

Тираж 1014 Подписное

ЦН И И П И Государственного комитета СССР по, делам изобретений и открытий

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Филиал ПП П «Патент», г. Ужгород, ул. Проектная, 4