Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИ

ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВ (б1) Дополнительное к авт. свид-ву (22) Заявлено 180577(21) 2486281/18с присоединением заявки Мо (23) Приоритет"

Опубликовано 050579. Бюллетень И

Дата опубликования описания 05.05.7

Союз Советским

Социалистическим

Республик

1)м Кл 2

8 11 С 27/00

Государственный комитет СССР по делам нзобретеннй н открытий

53) УДК 628. 327..6 (088.8) Ь (72) Автор изобретения

В. Г. Чернов

p)) . вяВИтЕЛЬ Владимирский политехнический институт (54) ЗАПОМИНМОЩЕЕ УСТРОЙСТВО

Изобретение относится к аналоговой вычислительной и измерительной технике и мажет быть использовано. в многоканальных аналоговых и цифровых информационно-измерительных системах.

Известно аналоговое запоминающее устройство (ЗУ), содержащее, накопители на кондейсаторах и узлы коррекции для многоуровневой стабилизации напряжения на конденсаторах. Конденсаторы поочередно подсоединяются к узлам коррекции с помощью ключей .tl).

Недостатком такого устройства является малое быстродействие, так как необходима большая емкость накопительных конденсаторов, поскольку компараторы узлов коррекции подключаются непосредственно к накопитель-. ным конденсаторам и входной ток компараторов оказывает дестабилизирующее действие на напряжение конденсаторов.

Наиболее близким по технической сущности к изобретению является многоканальное ЗУ, содержащее запоминающие емкости, ключи, аналогоцифровой преобразователь (АЦП), управляемый источник тока и блок управления, состоящий иэ счетчика и дешифратора (2), Недостатками этого устройства. являются сложность конструкции, обусловленная применением АЦП и управляемого источника тока, и малое быстродействие.

Целью изобретения является повышение быстродействия ЗУ.

Поставленная цель достигается тем, что в ЗУ, содержащее основные ячейки памяти, состоящие из последовательно соединенных ключа записи, запоминающей емкости и ключа считывания, элемент ИЛИ, подключенный к блоку управления, соответствующие выходы которого соединены с управляющими входами ключей записи и считывания, источник напряжения, введены дополнительная ячейка памяти, состоящая иэ последовательно соединенных ключа записи, запоминающей емкости и ключа считывания, и блок задания масштаба, входы которого соединены с выходом ключей считывания основных и дополнительной ячеек памяти. Один вход ключа считывания дополнительной ячейки памяти соединен с выходом элемента ИЛИ, а соответствующие входы ключа записи подключены к йсточнику о

661610 4 нающую емкость, а функциональным преобразованием выходных сигналов основных и дополнительных ячеек памяти.

Абсолютное уменьшение ошибки запоминания равно

5 1."

Д» Й

Тр где эюу время запоминания, а относительное

19 р Ъ т

Формула изобретения

3 напряжения и одному из входов блока управления.

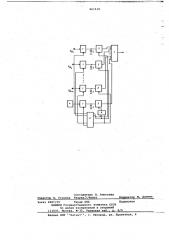

На-чертеже представлена структурная схема Зу.

3У состоит из нескольких основных ячеек памяти, содержащих ключи записи 1, запоминающие емкости 2 и ключи считывания 3, дополнительной ячейки памяти, содержащей аналогичные элементы, источника стабильного напряжения (тока) 4, блока управления

5; элемента ИЛИ 6 и блока задания масштаба 7.

Устройство работает следующим образом.

По сигналу блока управления в основную и дополнительную ячейки памяти записывается значение запоминаемого входного сигнала ЦВ „ и вспомогательного стабильного напряжения Уо

B процессе хранения напряжения в ячейках памяти изменяются согласно уравнениям

U„"- ОВЛ

- ь /т

- (т

U=U e о

В момент считывания информации блок управления 5 открывает соответст вующие ключи считывания 3 основных ячеек и через элемент ИЛИ и клЮч считывания 3 дополнительной ячейки напряжения U è Ц@подаются на блок

7, выходной сигнал которого описывается соотношением

-Итр.

О„. ив е

u = — "=% " 1 ),2, -,П. вь " 09 ц е-ttTÐ о,е

ПРи Tp ° =,, 1=1, 2,..., n, 1 т. е. при равенстве постоянных времени разряда основных и дополнительной ячеек

11ВЛ, о если можно выполнить условие - 1, Ug iq U z.. Необходимо отметить, что даже, если строго не Йиполняется равенство Tp. Tpg, то и в этом случае точность хранейия информации и быстродействие, повышаются, так как повышение точности осуществляется не путем воздействия на запомиВ связи с тем, что напряжения, запомненные в ячейках памяти, изменяются в небольших пределах, влияние погрешности делительного устройства на результирующую погрешность

ЗУ незначительно.

Запоминающее устройство, содержащее основные ячейки памяти, состоящие из последовательно соединенных ключа записи, запоминающей емкости и ключа считывания, элемент ИЛИ, подключенный к блоку управления, соответствующие выходы которого соедине30 йы .с управляющими входами ключей записи и считывания, источник напряжения, о т.л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит

36 дополнительную ячейку памяти, состоящую из последовательно соединенных ключа записи, запоминающей емкости и ключа считывания„ и блок задания масШтаба, входы которого соединены

40 с выходами ключей считывания основных и дополнительной ячеек памяти, один вход ключа считывания дополнительной ячейки памяти соединен с выходом элемента ИЛИ, а соответствующие входы ключа записи подключены к источнику напряжения и одному из входов блока управления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

60 Р 476604, кл. 8 11 С 27/00, 020 1.73.

2 Авторское свидетельство СССР

9 325634, кл. 8 1 1 С 27/00, 0904.70.

661610

Составитель Л. ймусьева

P акто Л. Утехина Тех е З.Фанта

Ко екто М, Демчик

Подписное

Заказ 2487/55 Т ираж 680

ЦНИИПИ государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж-35 Ра ская наб. д. 4 5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4