Устройство промежуточной памяти разравнивающего типа

Иллюстрации

Показать всеРеферат

l., т тон ;н : „-,-;,; а:.-:..,: и 66Т748

ОПИСАН И

И ЗОБРЕТЕ Н И

К АВТОРСКОМУ СВИДЕТЕЛЬСТВ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 18.01.77 (21) 2442776/18-25 (51) М. Кл.

НОЗ К5/13

G 01 V 5/00 с присоединением заявки К-— (23) Приоритет—

Государственный нюметет

СССР ао делам нзобретеннй н открытий

Опубликовано 05.05.79. Бюллетень №

Дата опубликования описания 15.05.79 (53) УДК550. .839 (088. 8) (72) Авторы изобретения

Г. И. Ильканаев, В. Г. Искендеров и Г. Л. Меликов

Всесоюзный научно-исследовательский институт нефтепром ысловой геофизики (71) Заявитель

""- «сЮЖЫЮМа . ° -:р" -« .(-: — =,. ц:.—..ль =::. л « друууу@ .„«у -« у" м,. а

1 (54) УСТРОЙСТВО ПРОМЕЖУТОЧНОЙ ПАМЯТИ

РАЗРАВНИВА1ОЩЕГО ТИПА

Изобретение относится к радиотехническим устройствам и может быть использовано для измерения характеристик поля ионизирующих излучений, в частности, при радиоактивном каротаже скважин.

В известных устройствах радиоактивно- 5

ro каротажа для согласования полосы частот случайно распределенных импульсов, представляющих собой измеряемый сигнал с полосой пропускания канала связи — каротажного кабеля, применяются пересчетные схемы или устройства преобразования случайно распределенных импульсов в квазиравномерное распределение (1), (2).

Наиболее близким к заявленному по технической сущности является устройство (3).

Это устройство включает первый и второй 15 накопительные регистры, состоящие из п триггеров, компаратор, выполненный на ячейках И-НЕ, и генератор синхроимпульсов.

Регистрируемые случайные импульсы заносятся в первый регистр, а выходные импульсы устройства — во второй регистр.

Выходной сигнал вырабатывается компаратором, когда количество хранимых в первом и втором регистрах импульсов находятся в определенном соотношении между собой. Частота синхроимпульсов находится в полосе пропускания канала связи и управляет выходными сигналами компаратора в соответствии с частотой поступления импульсов таким образом, чтобы сигналы в канале связи были равномерно распределены с частотой в пределах полосы пропускания канала связи.

Недостатком устройства является то, что при положительном флуктуационном выбросе регистрируемых случайных импульсов возможно переполнение первого регистра, в результате чего число пропущенных и не зарегистрированных импульсов кратно емкости упомянутого регистра. В то же время схема устройства достаточно сложна.

Целью настоящего изобретения является повышение точности преобразования и упрощение устройства.

Поставленная цель достигается тем, что в предлагаемом устройстве, асинхронный вход первого триггера соединен с инверсным выходом второго триггера, прямой выход каждого триггера соединен с управляющим входом того же триггера через ячейку И-НЕ, второй вход каждой ячейки И-НЕ соединен с инверсным выходом каждого последующего

661748 триггера, а выход генератора синхроимпульсов соединен со вторым входом и-ой ячейки

И-НЕ, выход которой является выходом устройства.

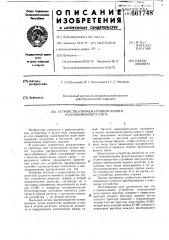

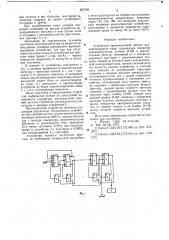

На фиг. 1 представлена принципиальная 5 схема устройства на триггерах R-S типа, а первого e-k типа; на фиг. 2 в временные диаграммы.

Устройство содержит накопительный регистр состоящий из и синхронизируемых

1О триггеров 1 — 4, причем триггер 1 имеет дополнительный асинхронный вход т, ячейки

И-НЕ 5 — 8, генератор 9 синхроимпульсов.

Временные диаграммы, представленные на фиг. 2, соответствуют следующим точкам устройства. 10 — на входе устройства, 11, 13, 15, 17 — на прямых выходах триггеров 1 — 4 соответственно, 12, 14, 16 — на выходах ячеек И-НЕ 5 — 7 соответственно, 18 — на выходе генератора синхроимпульсов 9 и 19— на выходе устройства.

Устройство работает следующим образом.

Пусть в начальный момент триггерь! 1 — 4 регистра находятся в состоянии О, т. е. на их прямых выходах установлен логический О, а на инверсных — логическая 1.

При указанном состоянии триггеров на выходах ячеек 5 — 8 устанавливается логическая 1. Наличие логического О на прямом выходе триггера 4 является запретом прохождению на выход ячейки И-НЕ 8, являющегося выходом устройства, и импульсов генера- 30 тора 9.

При поступлении первого импульса из потока случайно распределенных на счетный вход триггера 1, последний через время г, равное времени перехода триггера 1 из одного устойчивого состояния во второе, перейдет в состояние 1, вследствие чего на выходе ячейки И-НЕ 5 через время el, равное времени распространения сигнала в ячейке И-НЕ 5, появится логический О. Это в свою очередь обуславливает через время возврат триггера 1 в исходное состояние.

При возврате в исходное состояние триггера 1 установится в состояние 1 триггер 2, вследствие чего на выходе ячейки И-НЕ 6 через время появится логический О, а это в свою очередь аналогично первому обуславливает возврат через время триггера

2 в исходное состояние. При этом перейдет в состояние 1 следующий триггер 3 и т. д. все последующие. Процесс продолжается до тех пор, пока не перейдет в состояние 1 п-ый триггер 4. Наличие логического О на выходе генератора 9 в интервалах между двумя выходными импульсами генератора является запретом для возврата п-ro триггера

4 в исходное состояние.

Если на вход устройства поступит вто- 55 рой импульс, то этот импульс, дважды изменяя состояние триггеров от 1-го до n — 2-го (на фиг. 1 не показан), приведет в состояние 1 п — 1-й триггер 3. Наличие логического

О на инверсном выходе и-ro триггера 4 является запретом для возврата триггера 3 в исходное состояние. Таким образом, каждый из последующих поступающих на вход устройства импульсов будет поочередно переводить в состояние 1 триггеры от п — 2-го до 1-ro, зарегистрировав и импульсов.

Поступление и + 1-ro импульса не изменит состояния 1-го и последующих триггеров, т. к. наличие логического О на асинхронном входе триггера является достаточным условием нахождения его лишь в состоянии l.

С поступлением импульса с выхода генератора 9 на выход и-ой ячейки И вЂ” НЕ 8 через время т появится логический О, что обуславливает через время т возврат и-го триггера 4 в исходное состояние, а это в свою очередь вновь прекращение действия логического О на выходе ячейки И-НЕ 8. На выходе ячейки И-HE 8 очевидно будет получен отрицательный импульс длительностью

+ sa, совпадающий по времени с выходным импульсом генератора 9 и являющийся выходным импульсом устройства.

Появление логической 1 на инверсном выходе п-го триггера 4 (при возврате его в исходное состояние) обуславливает появление через время т логического О на выходе и — 1-ой ячейки И-НЕ 7 и возврат через время т в исходное состояние и — 1-го триггера 3. При этом вновь устанавливается в состояние 1 и-ый триггер 4, а логическая 1 на инверсном выходе триггера 3 обуславливает возврат через время e = ri + с в исходное состояние n — 2-го триггера.

При этом вновь перейдет в состояние 1 и†1-й триггер 3. Затем перейдет в исходное состояние и обратно в состояние 1 и — 2-ой триггер и т. д.

Вызванный поступившим с выхода генератор 9 импульсом процесс поочередного перехода триггеров в исходное состояние и обратно будет продолжаться до тех пор, пока установятся в состояние 1 триггеры от 2-ro до и-ro и примет исходное состояние триггер 1, т. е. с приходом первого импульса генератора 9, после завершения переходных процессов, в исходное состояние вернется лишь 1-й триггер 1.

С приходом следующего импульса с выхода генератора 9 на выход устройства пройдет второй импульс, а в исходное состояние вернется уже 2-й триггер 2. Процесс будет продолжаться до момента, когда в исходное состояние вернутся все и триггеров, а число импульсов на выходе устройства станет равным числу импульсов, поступивших на вход.

Особенностью предлагаемого устройства является необходимость выполнения условий тз <2(i + т ) и si )га, где гз — длительность импульсов генератора 9.

Второе условие выполняется применением ячеек И-НЕ с временем с распростране661748

Формула изобретения

Рыло ния сигнала в них большим, чем время перехода три гера из одного устойчивого состояния в другое.

При несоблюдении этого условия возможно появление на выходе устройства неразравненного импульса в том случае, если в состоянии 1 находятся хотя бы два последних триггера 3 и 4.

Допущение об определенном исходном состоянии триггеров регистра не является необходимым условием нормального функционирования устройства, так как при отсутствии сигналов на входе устройства все триггеры через время t (пЬ, где t3 — период импульсов генератора 9, окажутся в исходном состоянии.

В отличие от устройства, описанного в (3), в котором применяются накопительные регистры с емкостью памяти п-l, где с приходом n-ro входного импульса в интервале между двумя импульсами генератора синхроимпульсов может быть не зарегистрировано сразу и-1 импульсов, в предлагаемом устройстве не будут зарегистрированы лишь и + 1-й и последующие импульсы.

Число триггеров в предлагаемом устройстве выбирается исходя из допустимой погрешности устройства, максимальной средней частоты статически распределенных импульсов и времени усреднения t.

При испытании устройства получены следующие результаты. Погрешность устройства при средней частоте статистически распределенных импульсов 1500 Гц, периоде импульсов с выхода генератора синхроимпульсов

200 мксек и длительности этих импульсов

0,12 мксек составила 0,72 /О при использовании в устройстве 3-х триггеров и 0,045 /о при использовании 4-х триггеров.

Устройство является достаточно простым, не требующим специальной настройки и легко реализуется на серийно выпускаемых промышленностью микросхемах, например серии 133, 134, 155, что позволяет реализовать надежное малогабаритное устройство, 5 работающее в диапазоне температур окружающей среды от минус 60 до плюс 125 С.

Устройство промежуточной памяти разравнивающего типа, содержащее генератор синхроимпульсов, п-ячеек И-НЕ и накопительный регистр, состоящий из п синхронизируемых триггеров с управляющими входами, первый из которых имеет дополнительный асинхронный вход, причем счетный вход его является входом устройства, а счетный вход каждого из последующих триггеров соединен с прямым выходом предыдущего, отличающееся тем, что, с целью повышения точности преобразования и упрощения устройства, асинхронный вход первого триггера соединен с инверсным выходом второго триггера, прямой выход каждого триггера соединен с управляющим входом того же 5 триггера через ячейку И-НЕ, второй вход каждой ячейки И-НЕ соединен с инверсным выходом каждого последующего триггера, а выход генератора синхроимпульсов соединен со вторым входом и-ой ячейки И-НЕ, выход которой является выходом устройЗ0 ства.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3745.346, кл. 250 — 83.3R, 1973.

2. Патент США Ио 3.752.988, кл. 250 — 270, 1973.

3. Патент США № 3.720.910, кл. 340 — 18R, 1973. л л

661748

11

12

1О

Составитель В. Трофимов

Редактор А. Абрамов Техред О. Луговая Корректор А. Власенко

Заказ 2508/62 Тираж 1059 Подписное

ЦН И И ПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4