Инвертор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистииеских

Республик

«i) 661804 (61) Дополнительное к авт. свид-ву— (22) Заявлено 20.07.76 (21) 2387348/18-21 с присоединением заявки №вЂ” (51) М..Кл .

Н03 К19/08

Государстеенний квинтет,СССР не делам изобретений и аткрвтнй (23) Приоритет—

Опубликовано 05.05.79. Бюллетень № 17

Дата опубликования описания 07.05.79. (53) УДК 621.374 (088.8) (72) Авторы изобретения

A. Я, Гаршин, Б. М. Герш, А. Д. Торопов и Л. П. Удовик (71) Заявитель (54) ИНВЕРТОР

Изобретение относится к импульсной технике, предназначено для использования во входных схемах оперативных запоминающих устройств.

Известен инвертор, содержащий транзисторы прямого и инверсного выходов, токозадающий транзистор и ряд диодов. При 5 этом базы выходных транзисторов объединены через диод и через резисторы соединены с положительным полюсом источника питания, объединенные эмиттеры подключены к коллектору токозадающего транзистора

<о эмиттер которого через резистор соединен с шиной нулевого потенциала. Катод входного диода подключен ко входу инвертора, а анод — к базе транзистора инверсного выхода (1) .

Недостатки этого устройства — высокое

)5 значение минимального выходного -напряжения «нуля» и несимметричность прямого и инверсного выходов по минимальному выходному напряжению «нуля».

Наиболее близок к предлагаемому токовый инвертор, содержащий входной транзистор, эмиттер которого соединен со входом устройства, а база подключена через резистор к положительному полюсу источника питания, транзисторы прямого и инверсного выхода, эмиттеры которых соединены, базы объединены через диод, катод которого через резистор подключен к положительному полюсу источника питания, а анод соединен с коллектором входного транзистора.

При этом к катоду упомянутого диода подсоединен также коллектор дополнительного транзистора, база которого объединена с эмиттерами выходных транзисторов и через резистор соединена с шиной нулевого потенциала, к которой также подключен эмиттер дополнительного транзистора 12) .

У этого устройства ограниченные функ. циональные возможности при построении логических блоков из-за больших уровней выходных напряжений.

С целью расширения функциональных возможностей при построении логических блоков путем уменьшения уровней выходных напряжений, в инвертор, содержащий входной транзистор, эмиттер которого соединен со входом устройства, база — через первый резистор с шиной положительного потенциала источника питания, транзисторы прямого и инверсного выхода, первый и второй дополнительные транзисторы, коллектор вход661804

Фор,иула изобретения

40

3 ного транзистора соединен с базой транзистора прямого выхода, коллектор которого соединен с шиной положительного потенциала, а эмиттер — с базой первого допол нительного транзистора и прямым выходом устройства, через второй резистор с шиной нулевого потенциала, коллектор первого дополнительного транзистора соединен с базой транзистора инверсного выхода, через третий резистор — с шиной положительного потенциала, с катодом диода, анод которого соединен с коллектором входного транзистора, эмиттер первого дополнительного транзистора соединен с шиной нулевого потенциала, коллектор транзистора инверсного выхода соединен с шиной положительного потенциала, а эмиттер — с инверсным выходом устройства и через четвертый резистор — с шиной нулевого потенциала, введен второй дополнительный транзистор, коллектор и эмиттер когорого соединены соответственно с коллектором и эмиттером первого дополнительного транзистора, а база — с эмиттером *транзисто) а инверсного выхода.

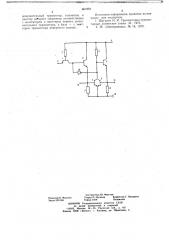

На чертеже представлена принципиальная схема устройства.

Эмиттер входного транзистора соединен со входом 2 устройства, а база через резистор 3 соединена с шиной положительного потенциала 4, транзистора инверсного выхода 5,транзистора 6 прямого выхода, первого дополнительного транзистора 7 и второго дополнительного транзистора 8. Коллектор транзистора 1 соединен с базой транзистора 5, эмиттер которого соединен с базой транзистора 7 и через резистор 9 с шиной нулевого потенциала 10. Эмиттер транзистора 7 соединен с шиной нулевого потенциала 10, а коллектор — с базой транзистора 6 и через резистор 11 — с шиной 4.

Коллектор и эмиттер транзистора 8 соединены соответственно с коллектором и эмиттером транзистора 7, база транзистора 8 соединена с эмиттером транзистора 6 и через резистор 12 — с шиной 10. Коллекторы транзисторов 5 и 6 соединены с шиной 4, а "их эмиттеры собтветствеййо с инверсным 13 и прямым 14 выходами устройства.

Анод диода 15 соедйнен с коллектором транзистора 1, а катод — с коллекторами транзисторов 7 и 8.

Работает устройство следуюшим образом

Если на вход 2 инвертора подана логическая единица (Ulx>+Us = 1,4), переход база-эмиттер транзистора 1 закрыт. Ток через резистор 3 и через переход база-коллектор транзистора 1 течет в базу транзистора 5 и открывает его. Эмиттерный ток транзистора 5 создает- падение напряжения на резисторе 9. Номинал резистора 3 выбирают таким, чтобы 1абК!! >>! !э = 0,7 в. При этом открывается транзистор 8, акт йонижается до 0,7 в, диод 15 открывается, и часть тока протекающего через резистор 3 в базу транзистора 5, ответвляется через диод 15 в

4 коллектор транзистора 7. На эмиттере транзистора 5 поддерживается постоянный потенциал 0,7 в. При этом транзистор 6 закрыт.

Если на вход инвертора подан логический

«нуль» (U4x

На эмиттере транзистора 6 поддерживается потенциал Уэе = 0,7 в. На эмиттере тран.—. зистора 5 при этом потенциал 145= 0 в.

Таким образом, при подаче на вход 2 логической единицы (U4x !,4 в), на выхоI де 14 имеется напряжение U gay = 0,7 в.

На выходе 13 при этом имеется напряжение

U Csrx = 0 в. При подаче на вход 2 логического нуля (U!1x = 0,7 в) на выходе l4 име О

20 ется напряжение ()йюх = 0 в, на выходе !3 при этом имеется напряжение Бйк= 0,7 в.

Инвертор по сравнению с прототипом обладает большими функциональными возможностями при построении логических блоков за счет снижения уровней выходных

25 напряжений логического нуля U8ar с 1,4 в до 0 в и логического нуля 14и с + Еп до 0,7 в.

Инвертор, содержащий входной транзистор, эмиттер которого соединен со входом устройства, база через первый резистор— с шиной положительного потенциала источника питания; транзисторы прямого и инверсного выходов и первый дополнительный транзистор, коллектор входного транзистора соединен с базой транзистора прямого выхода, коллектор которого соединен с шиной положительного потенциала, а эмиттер с базой первого дополнительного транзистора и прямым выходом устройства, а через второй резистор — шиной нулевого потенциала, коллектор первого дополнительного

45 транзистора соединен с базой транзистора прямого выхода, через третий резистор с шиной положительного потенциала, с катодом диода, анод которого соединен с коллектором входного транзистора, эмиттер первого дополнительного транзистора соединен

50 с шиной нулевого потенциала, коллектор транзистора инверсного выхода соединен с шиной положительного потенциала, а эмиттер — с инверсным выходом устройства и через четвертый резистор — с шиной нуле55 вого потенциала, отличающийся тем, что, с целью расширения функциональных возможностей при построении логических блоблоков путем уменьшения значений уровней выходных напряжений, в него введен второй

661804

Составитель Ю. Фирстов

Техред О. Луговая Корректор Г. Назарова

Тираж 1050 Подписное

ЦН И И ПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Филиал lI IIII «Патент», г. Ужгород, ул. Проектная, 4

Редактор Б. Федотов

Заказ 2513/66

5 дополнительный транзистор, коллектор и эмиттер которого соединены соответственно с коллектором и эмиттером первого дополнительного транзистора, а база — с эмиттером транзистора инверсного выхода.

Источники информации, принятые во внимание при экспертизе!. Шагурин И. И. Транзисторно-транзисторные логические схемы. M., 1975.

S 2. Ж. «Электроника», № 18, 1972.