Устройство для вычисления функции

Иллюстрации

Показать всеРеферат

Ceios Советник

Сещвалистнческик

Васлублил

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 160876(21) 2398563/18-24 с присоединением заявки М(23) Приоритет

Опубликовано 1505,79. Бюллетень М:18

Дата опубликоввиия описания 1505,79 (51)М. Кл.2

G 06 F 7/38

Государственный комитет

СССР

R0 делам изобретений и открытий (53) УДК 681. 325 (088,8) (72) Авторы изобретения

В. И. Жабин, В.И. КОрнейчук, В. B.Ìàêàðîâ и В. П. Тарас ен ко (Киевский ордена Ленина политехнический институт

71) аязитеAb им.50-летия Великой Октябрьской социалистической революции (54) устРОЙстВО для Вычисления Функции у= т.

Предлагаемое изобретение относится к области цифровой вычислительной техники И может быть использовано в цифровых вычислительных машинах н устройствах, построенных на основе больших интегральных схем.

Известно устройство для вычислейня функции Y--7. содержащее два сумматора, регистры и счетчики (1) . Недостат-. ком этого устройства является. относительно низкое быстродействие.

Наиболее близким к изобретению по своей технической сущности является устройство, содержащее входной и выходной регистры, первый и второй сум-)5 маторы, регистр сдвига, блок сдвига и шифратор, вход которого соединен с выходом регистра сдвига, выход входного регистра соединен с первым входом первого сумматора, выход которого соединен с первым входом входного регистра, первый и второй входы второго сумматора соединены.с выходами блока сдвига и выходного регистра соответственно, а выход соединен с первым входом выходного регистра (2).

Недостатком известного устройства является невозможность выполнения вычислений, когда в устройство йоступили еще не все разряды входного сло2 ва, например, когда входная информация поступает последовательно разряд эа разрядом с цифровых измерительных приборов пбразрядного уравновешивания или преобразователей аналог-код.

Это снижает быстродействие системы. другим недостатком известного устройства является сложность его интегрального исполнения, связанная с болБшим числом вйешних выводов.

Предлагаемое" устройство отличается.от известного тем, что оно содер.жит первый коммутатор, первый и вто- . рой входы которого соединены с выходами шифратора и регистра сдвига соответственно, а выход соединен со вторым входом первого сумматора, первый и второй элементы И, первый и второй элементы запрета, элемент задержки, триггер и второй коммутатор, входы которого соединены с выходами регистра сдвига и выходногб регистра соответственно, первый выход второго коммутатора соединен с первым входом первого элемента И и с запрещающим входом первого элемента запрета, первый вход которого соединен с выходом триггера,.первый вход которого соединен со вторым выходом второго коммутатора, а второй вход — со вторыми

66293 входами Первых элементов И запрета и через элемент задержки - со входом региСтра сдвига. Третий вход первого коммутатора соединен с первым входом второго элемента И, выход которого соединен со вторым входом выходного регистра, а второй вход - со вторым входом входного регистра и с выходом второго элемента запрета, запрещающий вход которого соединен с выходом . знакового. разряда первого сумматора, входы блока сдвига соединены с выхо- ® дами регистра сдвига и выходного регистра соответственно.

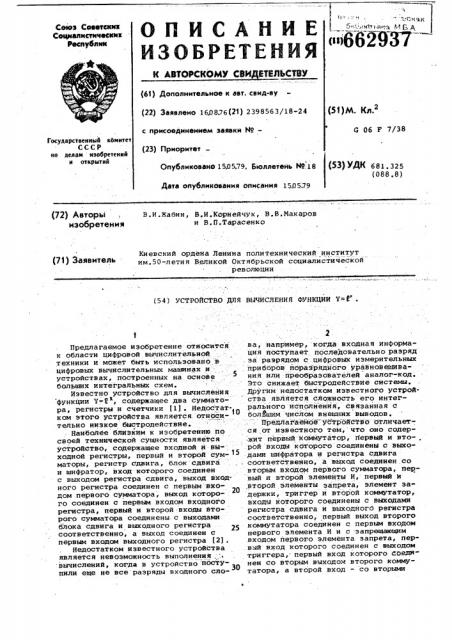

На чертеже изображена структурная схема устройства для вычисления функции Y=Z". l5

В сосТав устройства входят входной регистр 1, первый сумматор 2, регистр сцвига 3, шифратор 4 и первый коммутатор 5. Выходы входного регистра 1 связаны с п рвыми входами р0 первого сумматора 2, вторые входы которого подключены к выходам коммутатора 5. Выходы сумматора 2 соеди "йены "co входами" регистра 1. "

Регистр сдвига 3 содержит (и+3) разрядов. Выходы первых и его разрядов связаны со входами шифратора 4 и коммутатора 5. Выходы шйфратора 4 подключены ко вторым входам коммутатора 5.

В состав устройства входят также выходной регистр 6, второй сумматор

7, блок сдвига 8 и второй коммутатор

9. Выходы выходного регистра 6 подключены к первым входам второго сумматора 7, к информационным входам блока сдвига 8 и ко входам второго коммутатора 9. Выходы регистра сдвига 8 связаны со вторыми входами сумматора

7, выходы которого подключены ко входам выходного регистра 6. Выходы ре-. 40 гистра сдвига 3 подключены к управляющим входам блока сдвига 8 и коммута оре 9-. Выход каждого i-го разряда регистра сдвига 3 связан с управляющим входом сдвига на i разрядов бло- 45 ка сдвига 8, который предназначен для сдвига кода от одного до и разрядов.

Поэтому к его управляющим входам подключены первые и разрядов регистра сдвига 3. 50

В состав устройства также входят элементы запрета 10, 11, элементы И

12,13, триггер 14 и элемент задержки

15. Выход элемента задержки 15 связан

ñé цепью сдвига регистра сдвига 3.

Знаковый разряд сумматора 2 связан с инверсным входом элемента запрета 10, выход которого подключен к цепи приема кода входного регистра l и к первому Входу элемента И 12. Вы сод элемента И 12 связан с цепью приема ко- @) да выходйого регистра 6. Первый выход коммутатора 9 подключен ко входу эле.мента И 13 и к инверсному входу эле- мента запрета 11. Второй выход коммутатора 9 подключен,к информационному !

7 входу триггера 14, выход которого связан со входом элемента запрета 13.

Устройство также содержит информационные входы 16,17, управляющие входы 18-20 и выходы 21,22. Информационные входы 16,17 подключены к управляющим входам коммутатора 5. Управляющий вход 18 связан со входом элемента запрета 10. Управляющий вход 19 подключен к третьему управляющему входу комМутатора 5 и ко второму входу элемента И 12.

Управляющий вход 20 связан с управляющим входом триггера 14 и входами элемента запрета 11 и элемента И 13, выходы которых соединены с выходами

21,22. Кроме того, управляющий вход

20 соединен со входом элемента за,держки 15.

Сумматоры 2,7 могут быть комбинационными. Входной и выходной регистры могут быть построены на основе триггеров с внутренней задержкой.

Входной регистр 1 содержит и разрядов, а выходной регистр 6 содержит (n+2) разряда, причем два старших разряда предназначены для хранения целой части результата.

-.В шифраторе 4 записаны в дополнительном коде константы Ы(1+2 ), где i, = 1,2...;n.

Коммутатор 5 содержит и групп элементов И, по три элемента в каждой группе. Первый вход первого элемента

И i-й группы подключен к выходу (i.-l)-го разряда регистра сдвига 3.

Первый вхоф второго элемента И каждой . i-й группы связан с выходом

i-го разряда регистра сдвига 3. Первый вход третьего элемента,И каждой

i-й группы подключен к i-му выходу шифратора. Вторые входы элементов

И всех трех групп связаны соответственно с информационными вхо,",ами

16,17 и управляющим входом 19. Выходы элементов И каждой группы объединяются с помощью элементов ИЛИ.

Коммутатор 9 построен из (и+2) групп элементов И. Каждая группа состоит из двух элементов И. Первый вход первого элемента И каждой i-й группы связан с выходом i-го разряда выходного регистра 6. Первый вход второго элемента И каждой 1-й группы связан с выходом (1+1)-ro разряда .выходного регистра 6 (предполагается, что старшие разряды выходного регистра 6 имеют меньшие номера). Вторые входы элементов И каждой i-й группы связаны с выходом (i+1)-го разряда регистра сдвига 3. Выходы первых элементов И всех групп объединены с помощью элемента ИЛИ, выход которого

Пбдключен ко входу элемента И 13.

Выходы вторых элементов И всех групп объединяются с помощью элемента ИЛИ, выход которого соединен с входом триггера 14

5 6629

Предлагаемое устройство работает следующим образом.

В начальном состоянии в первом разряде регистра сдвига 3 записана единица, в остальных разрядах - нули.

В выходном регистре 6 записано число, равное единице, т.е. во втором разряде записана единица. Входной .регистр 1 установлен в нулевое состояние. Вычисление функции Y-Я" осуществляется в (n+3) циклах, каждый из 10 которых состоит из шести тактов.

К началу первого такта каждого

1-ro цикла на информационные входы

16,17 поступают сигналы, значения которых характеризуют значение очередно .5

ro разряда операнда (операнд поступает, начиная .со старших разрядов).

Если единичный сигнал поступает на информационный вход 16, то очередной разряд "операнда численно равен 2. 20

Если единичный сигнал поступает на информационный вход 17, то очередной разряд операнда численно равен 1. В случае, если единичный разряд не по= ступает ни на один из информационных входов 16,17, очередной разряд операнда численно равен О. Значение операнда ограничено О х<1.

В первом такте по управляющему сигналу, поступающему на управляющий вход 18, производится прием в регистр 1 кода с выхода сумматора 2.

Этот код численно равен сумме кода, записанного в регистре 1 к началу первого такта,и кода, записанного в регистре сдвига 3. В этом случае, если единичный сигнал поступает на информационный вход 16, в (i-1)-й разряд содержимого входного регистра l прибавляется единица. Если единичный сигнал поступает на информаци- 40 онный вход 18, единица прибавляется в i-й разряд содержимого входного регистра 1. Если же на информационных входах 16,17 присутствуют нули, содержимое регистра 1 не меняется.

К началу второго такта сигналы с информационных, входов 16,17 снима,ются, а на управляющем входе 19 уста навливается единичный сигнал, который присутствует до конца i-го Цикла вычислений.

Во втором, третьем, четвертом и пятом тактах управляющий сигнал поступает также на управляющий вход 18. По бб этому сигналу в регистр 1 производит.ся прием кода, значение которого равно алгебраической сумме кода, находившегося в регистре 1 к. началу такта и константы -0п (1+2 ), которая выбирается из шифратора 4 единичным сигналом с выхода i-го разряда регистра сдвига. Если же значение этого кода оказывается отрицательным (о чем свидетельствует единица в знаковом

-разряде сумматора 2), элемент запре- 65

37 6 та 10 запрещает прохождение сигналов на прием кода в регистр 1.

В результате, по -окончании пятого такта в регистре 1 входного слова образуется минимальный,положительный остаток от вычитания из содержимого регистра 1 от орной до четырех констант — 8n (1+2 " ) .

Сигналы с выхода .элемента запрета

10 через элемент И 12 разрешают прием кода с выходов второго сумматора

7 в выходной регйстр 6.

В выходном регистре 6 осуществляется прием кода, значение которого равно сумме кода, который был записан в выходном регистре б к началу такта, и этого же кода, сдвинутого вправо на.

i разрядов.

В шестом такте по управляющему сигналу, поступающему на управляющий вход 20, производится выдача информации на выходы 21,22. При этом на один вход элемента И 13 и инверсный вход элемента запрета 11 поступает значение (i-1)-ro разряда выходного регистра 6 (выход информации производится, начиная с 2-го цикла). В триггере 14 к этому времени зафиксировано, значение этого же разряда результата, которое было записано в выходном регистре б к началу i-го цикла.

Если единичный сигнал присутствует на выходе 21, это свидетельствует о том, что очередной разряд требуемого значения функции Y=t численно ранен

2. В случае, если единичный сигнал появится на выходе 22, очередной разряд требуемого значения функции численно равен 1. Если же единичный сигнал не появится ни на одном из викодов 21,22, это свидетельствует о том, что очередной разряд требуемого значения функции численно равен О.

По окончании управляющего сигнала, поступающего на управляющий вход 20, содержимое i-го разряда выходного регистра б записывается в триггер 14.

Epode того, производится сдвиг информации в регистре:сдвига 3. вправо на один разряд. На этом оканчивается один цикл вычислений.

В результате выполнения (n+3) цик" лов на выходах 21,22 формируется последовательно разряд за разрядом требуемое Значение функции У=Я»,представленное избыточным двоичным кодом с цифрами 0,1.,2 в каждом разряде.

Рассмотрим работу устройства на примере.

Пусть необходимо вычислить функ« цию 7=8" в точке х = 0,022102. Разрядность представления операнда и результата n=á.

В табл. 1 показаны значения коне» таит — fn .(1+2 ), где 1=1,2,3,4,5,6, значения которых выражены s дополнительном коде.

Таблица 1 1ОООООООО

Иск.сост.

0,000000

1 1

2 г

I о,aooooo o,aîoîîî

L0.100000

1 110010 о,oaooao o,о1оо1о — 00,010010

+1 1ОО1О

o,îîîa0o — о,ооо1оо

1 1

О,О1О1ОΠ— О,О1О1ОО

I 0. 010 100 .

1 lll001

О,001101 О,ОО11О1

« 0,001101

1,111001

О,ООО11Π— О,ООО110

О,ОО1О1О -О,ОО101О

I +0,0D1D10

1 111100

О,ОО HÎ Î,OOO11O

О,ООО11О

O,аООО1Π— 0,000010

Вычисление требуемого значения

662937 в ункции иллюстрируется в табл.2, 3 в каждом цикле вычислений.

В табл.2 показаны состояния регистра сдвига 3, входного регистра 1, сложение двух чисел на сумматоре 2 в первых шести циклах вычислений, так как n=6 и операнд поступает на входы устройства только в первых шести циклах. Процесс преобразования аргумента в каждом цикле показан до тех пор, пока остаток от алгебраического сложе10 ния содержимого регистра 1 и констант не становится отрицательным и прием кода в регистр 1 не производится.

Таблица 2

О,ОООО1О

1.11" 0 ОООО1ОООО ф

662937

Проложение таОлицн 3

О,ОООО1О

1 О,ОООО1О

1 111110

5 1 О 0

0,000000 0,000000

О,ОООО1О О,ОООО1О

l — +o; оооо10

1 111111

0,000001 — 0,000001

iO,ООООО1

1 111111

О ОООООО О 000000 o,оооооо

1 llllll

lillllll

000000100

100000000 01 i 000000

О10ООООО0 — О1,0ООО00

00 010000

01,010000 01,010000

1,010000

00 010100

01, 100100 01, 100100

Исх. сост.

2 2 1

3 1

+00 001100

01,110000-01,110000

01,110000

+00 001110

3 1

000

4 2 1

1 llll

+00 0OOlll

Номер Номер Вход Вход Регистр l цикла такта 16 17

В табл. 3 показаны состояния выходного регистра 6, три ггера 14 процесс суммирования на сумматоре, причем такт, когда прием кода в выходной регистр 6 не производится, не показан и введено следующее обозначение: А;—

Сумматор 2 Регистр сдвига 9 единичный сигнал на выходе элемента

И 12 в 1-м цикле вычислений. Он означает, что суммирование содержимого выходного perHc a 6 производится с этим же числом, сдвинутым на l разрядов вправо.

662937

12

П о олжение табл. 3

Номер такта

Номер цик ла дви"г«а»ю«щит регистр

Ц о„„

x <., Jl

Ц о х гч

CA

Выходной регистр СумматоР

A(10,000101-10,000101

L10,000101

00 001000

».«» «1«

3 1

10, О 01101-10,001101

1 1 0 2

000010000

5 2 1

00 000100

10,0

1 1

0 0

000001000

1 1

+00 000010

10,01001 1-:.-10, 010011 — -10,010011

+00 000010

10,010101 10,010101

0000000100

3 1

0 О

0 О

О 1 1 О

1 1

000000003 10 010101

8 б

9 6

10;010101

0 1 1 О необходимое для формирования и отработки этого управляющего воздействия.

В предлагаемом устройстве старший разряд требуемого значения функции вычисляется во втором цикле и исполнительный орган системы управления начинает отрабатывать полученное управляющее воздействие. Для определенности полагаем, что время отработки управляющего воздействия исполнительным органом системы управления

t >(и+3)t, где t — период поступления цифр операнда. Тогда время формирования и отработки Управляющего воздействия Т1 =2t+tu.

Предположим, что при п 30t =40t

Тогда для известного устройства (2) получим T=60t+tl,=100t, à T1=2t+40t

=42t. Таким образом, в данйом случае, предлагаемое устройство позволит уменьшить время формирования и отработки исполнительным органом системы управления в 2,5 раза. Кроме того, предлагаемое устройство позволит увеличить быстродействие при работе в вычислительной среде. Пусть последовательно соединены К устройств, время вычислеиия в каждом иэ которых

7 б 00000001() 10,010101

В результате выполнения 9 циклов вычислений на выходах устройства последовательно разряд эа разрядом сформировался код 01,210101=

=/20 010101/2=2 328/1О

Значение аргумента х=0,022102= =/0 110110 /Ою845/ц> ° 45

Табличное значение 2,32798.

Из рассмотренного примера видно, что значение функции в предлагаемом устройстве вычисляется в (n+3) цик- 50 лах, причем, благодаря совмещению so времени процессов поразрядного ввода операнда и вычисления очередных цифр результата, старшие разряды требуемох о "значения функции, котор е н ут 56 большую информацию о нем, вычислаются в первых циклах. Это позволяет эффективно испольэовать предлагаемое .Устройство в системах управления процессами в реальном масштабе времени, кохфа процесс формирования цифр операнда ограничен внешними факторами, а управляющее воэд .йствие для исполнительного органа системы управления формируется непосредственно по резуль татам вычислений. Определим время, 1 0 0 0 0 0

13 6629 равно t>< (и+3)t. В этом случае на выходе, например, первого устройства в третьем цикле появится старшая цифра результата и второе устройство начинает вычисления, начиная с четвертого цикла. Тогда время вычислений К функций равно Т (п+Зк)t,÷òî 5 при K=10, à n=30 составляет Т =60 .

Для известного устройства (2)

Т =300 t. Таким образом s данном случае.предлагаемое устройство позволит повысить быстродействие при работе в 0 вычислительной среде s 5 раз. Кроме того, поразрядный ввод операнда и вывод результата. позволяет значительнс уменьшить количество внешних связей.

Зто обусловливает возможность реализации предлагаемого устройства в виде большой интегральной схемы.

Формула изобретения

Устройство для вычисления функции

Y=Ã, содержащее входной и выходной регистры, первый и второй сумматоры, регистр сдвига, блок сдвига и шифратор, вход которого соединен с выходом регистра сдвига, выход входного регистра соединен с первым входом первого сумматора, выход которого соединен с первым входом входного ре-ЗО гистра, первый и второй входы второ- го сумматора соединены с выходами блока сдвига и выходного регистра соответственно, а выход соединен с первым входом выходного регистра, о т- 35 л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия, уменьшения числа внешних выводов, 37,14 ьно содержит первы коммутатор, первый и второй входы которого соей нены с выходами шифратора и регистра сдвига соответственно, а выход соединен со вторым входом первого сумматора, первый и второй элементы И, первый и второй элемейты запрета, элемент задержки, триггер и второй коммутатор, входы которого соединены с выходами регистра сдвига и выходного регистра соответственно, первый выход второго коммутатора соединен с первым входом первого элемента И и с запрещающим входом первого элемента запрета, первый вход которого соединен с выходом триггера, первый вход .которого соединен со вторым выходом второго коммутатора, а второй вход — со вторыми входами первых элементов И запрета и через элемент задержки — со входом ре" гистра сдвига, третий вход первого коммутатора соединен с первым входом второго элемента И, выход которого соединен со вторым входом выходного регистра, а второй вход — со вторым входом входного регистра и с выходом второго элемента запрета, запрещающий вход которого соединен с выходом знакового разряда первого сумматора, входы блока сдвига соединены с выходами регистра сдвига и выходного регистра соответственно.

Источники информации, принятые во. внимание при экспертизе

1. Авторское свидетельство СССР

9 378864, кл. G 06 F 7/38, 1972.

2. Байков В.Д., Смолов В.Б. Аппаратурная реализация элементарных функций в ЦВМ. Из-во Ленинградского университета, 1975.

ЦНИИПИ Заказ 2701/50

Тираж 779 Подписное

Филиал ППП Патент

r.Ужгород,ул.Проектная,4