Устройство для умножения

Иллюстрации

Показать всеРеферат

Саюз Советских

Социалистических

Республик (ji®//gal{) {6I) Дополнительное к авт. сеид-ву

{22) Заявлено 0407.77(21) 2495751/18-24 (51 М 2 с присоединением заявки ¹

G 06 F 7/39

Государственный Ониитет.СССР по делам изобретений и открытий

{23) Приоритет(53) УДК 681. 325 (088.8)

Опубл ковано 15„05.79. Бюллетень ¹ 18

Дата опубликования описания 1505.79 (72) Автор

- изобретения

С.И. Скрипицына (71) 3аявитель иосковский ордена трудового красного, Знамени инженерно-фи зи ческий институт (54 ) УСТРОЙСТВО ДЛЯ УИНОЖЕНИЯ

Изобретение относится к вычислительной технике и может быть применено в арифметических устройствах цифровых вычислительных машин, особенно в случаях повышенных требований по быстродействию.

Известно устройство, состоящее иэ сдвиговых регистров множителя и сумматора, в которых операция умно. жения реализуется путем сдвига регистров множимого и множителя и многократных сложений в сумматоре множимого, сдвинутого на определенное число разрядов, определяемое положением единиц в разрядах множителя, с частными произведениями, хранящимися в сумматоре (1), Недостатком известного устройства является низкое быстродействие. 20

Наиболее близким по технической сущности к данному изобретению является устройство, содержащее блок управления, регистр множителя, сумматор, блоки произведений множимого на 25 константы, блоки выдачи в сумматор произведения множимого на константы со сдвигом влево и без сдвига, причем выходы регистра множителя соединены со входами блока управления (2) . 30

Недостатком известного устройства является низкое быстродействие.

Целью изобретения является поВыще" ние быстродейСтвия.

С этой целью s устройство введены

2 блоков выдачи в сумматор произведения множимого на константы, 2 1 (Х З) блоков произведений множимого на еконстанты 2 р +1 (р "- О, 1,..., (2 -1), коммутатор сдвига кода, (2 -1) выходов первой и второй групп выходов блока управления соединены со входами управления блоков выдачи в сумматор произведения множимого на константы со сдвигом на 2

Ъ разрядов влево и без сдвига соответственно, информационные входы которых соединены с выходами блока произведения множимого на константу (2р„+1), выходы блоков выдачи в сумматор произведения множимого на константы со сдвигом на 2 разрядов влево и беэ сдвига соединены с информационными входами коммутатора сдвига кода, (2-1)-е выходы третьей и четвертой групп выходов блока управления соединены соответственно с (е.-1)-ми входа- . ми первой и второй групп управляющих входов коммутатора сдвига кода, выхо3

662940 4 ды которого соединены со входами сум- входы íà 2с разрядов влево, где

12с3 =10,1, .. ° целая часть (.И- ж

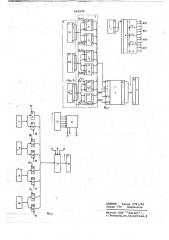

На фиг.l представлена структурная . 42ртп+1) )-1). Блоки выдачи в сумматор схема устройства умножения, на фиг.2 -. произведения множимого на константы пример выполнения устройства для, выполняет выдачу результата со сдвиумножения при п=б. гом на 2 разрядов влево. Сумматор е

Устройство (см.фиг. l ) содержит: 5 и регистр множителя содержат схемы коммутатор сдвига кода 1, сумматор 2, сдвига на п=2 разрядов вправо.

Регистр множителя 3, блок управления Работа устройства Разбирается на

4„ блоки выдачи в сумматор произве- . примере устройства для умножения дения множимого на константы со сразу на 6 разрядов множителя (п=б), сдвигом на 2 разрядов влево и беэ !О для которого С= =3 > pm >=f0,1,..., Q сдвига 5. 2 блоков б произведений 2 -1) =)0,1,2,1$ промежуточные промножимого на константы 2р +1, В (m), изведения. множимого на числа 1,3, I (5

В (с), А (m), А (с) - группы выходов и 7). На фиг.2 изображены блоки проблока управления. А (m). и А (c) - изведения множимого на константы выходы блока управления, соответст- . l5 7,8,9,10; блоки выдачи произведения вующие определяемым и младшими разря- множимого на константы в сумматор дами регистра множителя числам,. яв-, 6es сдвига 11,12c13,14; блоки выдаляющимися элементами одной из m, где чи произведения множимого на кон ««- 0 1 (2 1-1)> матриц A. = станты в сумматор со сдвигом на 2

Й) 1 р p ° » ° и

Ф

* a>c)/mcoost и одной из .с матрйц" " . д0 Разряда влево 15,16,17,18, регистр

De= (dim)/c.corisyi где строки матриц .. множителя 19, коммутатор сдвига ко(aic)m и (dim)c определейы как да 20, блок управления 21, сумматор

"aic) /c=cons4 =(dim)/m=congt =Ц2Яа+ l), 22, выходы блока управления 23

«&+1ы 2е1(с310,1, . ((;f- .1од (2рш+1)((),,... Устройство работает следующим

jism=10,i, ji— = 1,2,...2 -1), образом. столбцы матрицы (а1c)m определены как - .. В соответствии с приведенными формулами образования строк и столб а(С =.1(2РЩ k) 2 Р " 2 3 ji=kOna<,: ЦОВ: МатРИЦ Am(aiC)/В*СОПЬФ v DC (dim)/С-СОпэ

Вщ= (Ь3с gg Кс (Kjm)/сСд у „уста столбць матРицы (dim)e опРеделены Ройство характеризуют следующие матри(ш)с . цы чйсел, соответствующие б младшим

j(2, 1 Rm e« ., :: .: разрядам регистра множителя

I А 1 9 17 25 33 41 49 57

2 10 18 26 34 42 50 58 соединены: A(m)c - с управляющими вхо- .. . 4 12 20 ° 28 36 44 52 60 дами блоков выдачи пРоизведения мно-35 I1 А (3 11 19 27 35 43 51,.59) жимого на константы в сумматор 5 в

1 (6 14 22 30 38 46 54 62/ Соответствии со значением ш для маФ-: Х11A< (15 13 2 1 29 37 45 5 3 6 1 )

Рицы Am в пРЯмом кбде без сдвига, . IV А (7 15 23 31 39 47 55 63), А(с) - с управляющими входами 0(еД= Если число, образованное б младшими

=(0,1,... E-1) коммутатора сдвига ко-40 разрядами. множителя является членом па в соответствий со значением" с мат- 1 матрицы, то узлом управления воэрицы Dc, вторые выходы блока удрав-:: буждается выход 27 и на коммутатор ленин, B(m) и В(с) соответствующие поступает Множимое в прямом коде без ю определяемым и,д адшими разрядами сдвига. Если число, образованное 6 регистра множителя числам,,являющими- 45 падшими разрядами множителя является элементами одной из В матриц . ся членом II матрицы, то на коммуКс-(Kjm)/cc „sg и одной из m матриц татор подается с выхода 28 блока ynBm= (ЬЗс)/ссо„э, где строки обейх равления 21 утроенное множимое (для матриц определены как (b1c)/c íîàà » . IXI u Iv матриц соответственно упн1К3ш3/Ф СопМ =1(2pm+1) 2 +3 ), где 50 теренное и усемеренное множимое с

133=(0, j3 р (Я=jlк1,...,2 -ij столбцы„.. 24 и 25 управляющих выходов). матрицы ВшфЬ3с,) определены как ) Ь3ф Если при этом это число является (2Pm+1) 2 +3 3/>=сопз i а столбцы членом одной из матриц V,VI или VII матрицы Кс=(К3ш)c=conq опредеЛены V D 1 9 17 25 33 41 49 57

КРк (K3m)=.$(22m+1) 2 +3)/j=gggst 55 3 11 19 27 35 43 51 59 соединены: B(m) — с управляющими вхо- 5 13 21 29 37 45 53 61 дами блоков выдачи в сумматор произ- 7 15 23 31 39 47 55 63 ведения множимого на константы в пря- VI D((2 10 18 26 34 42 50 58) мом коде со сдвигом на Й разрядов 6 14 22 30 38 46 54 62l влево s соответствии со значением m 1, (4 12 20 28 36 44 52 60) матрицы Вш=(Ь3с)/ ы щ,ед, В(с) - с

60 то на коммутатор одновременно с сигуправляющими входами D(c) коммутато- налами с выходов 27-30 подаются с ра сдвига кода в соответствии со эна- выходов 31 (для матриц Ч) 32 (для чением с матрицы К =-(Kjm)/c=cð„s . Ком- матриц VI), 33 (для матрицы VII) упмутатор сдвига кода 1 предназначен равляющие сигналы, производящие сдвиг для сдвига кода поступающего на его 65 входного кода на 0;1 или 2 разряда

6629 влево, в результате чего на сумматор подается одно из чисел 1,2,...,7, Если затем это число является членом одной иэ матриц Bm ЧХХХ,IX,X или

XI, где

VIII Во 8 ° ° ° .15 IX В1 (24,25 ° ° ° ° 31)

16....23 \ 48,49....55)

32... . 39

Х В2 (40,41....47)

XI В (5 6, 5 7.... 6 3), то вйрабатывается соответственно на 10 выходах 23-25, 19,20 или 26 управляющий сигнал и на коммутатор подается множимое, умноженное на 8, 24,40 или

56. Если при этом это число является членом одной из матриц К XII XIII

XIV

Ко 8,9...15

ХХХ 24,25 ...31

40,41...47

56,57...63

К (16,17....231

XII I (48, 49 .. ° . 55/ (32, 33 .. ° . 39), то одновременно. с выходами 23-25 возбуждаются выходы 31, 32,33, производящие сдвиг поданных на входы коммутатора сдвинутых кодов числа на 0;1 или 2 разряда влево, передавая в сумматор промежуточное произведение, равное множимому, умноженному на 30 числа (1,2....7) х 8, в результате чего в. сумматоре релазируется искомое произВедение . Например, пусть 6 младших разрядов множителя составляют чис- ло 28, это число является членом 11, 35

VII,IX u XII матриц, т.е. будут выработаны сигналы (на выходах) 27,33, 24 и 31, в результате чего на коммутатор

„20 сигналом С выхода 27 подается множимой с блока выдачи 11 в прямом коде 40 без сдвига, управляющим сигналом с выхода ЗЗ, оно сдвинется на 2 разряда влево в коммутаторе 20 и на сумматор

22 будет передано число,4. Затем сигналом с выхода 24 с блока управления. 45

21 через блок выдачи 16 на коммутатор 20 поступит утроенное множимое с блока 8 со сдвигом на 3 разряда влево, т.е. множимое, умноженное йа число 24, так как при этом сигнал управления с выхода 31 производит через коммутатор 20 его передачу в сумматор 22 без сдвига, то в сумматоре к числу 4М прибавится число 24М, 40 6 где И вЂ” множимое, образуя искомое произведение 28М. Аналогичным образом .реализуется умножение и на любое другое число от 0 до 2 .

Предлагаемое устройство практически на таком же количестве оборудования, что и прототип, реализует операцию умножения в два раза быстрее.

Формула изобретения

Устройство для умножения, содержащее блок управления, регистр множителя, сумматор, блоки .произведения множимого на константы, блоки выдачи в сумматор произведения множимого на константы со сдвигом влево и беэ сдвига, причем выходы регистра множителя соединены со входами блока управления, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в устройство введены 2 блоков выдачи в сумматор произведения множимого на константы, 2 (Ь>3) блоков произведений множимого на константы 2 pm+1 (pm=0,1,..., (2 -1), коммутатор сдвига кода, (2 -1) выходов первой и второй групП выходов блока управления сое,динены со входами управления блоков выдачи в сумматор произведения множимого на константы со сдвигом на

2 разрядов .влево и без сдвига соответственно, информационные входы которых соединены с выходами блока произведения множимого на константу (2pm+1), выходы блоков выдачи в сумматор произведения множимого на кон» станты со сдвигом на 2 разрядов влево и без сдвига соединены с информационными входами коммутатора сдвига кода, (8-1)-е выходы третьей и четвертой групп выходов блока управления соединены соответственно с (М-1)-ми входами первой и второй группы управляющих входов коммутатора сдвига кода, выходы которого соединены со входами сумматора.

Источники информации, принятые во внимание при экспертизе

1. Субье-Ками А. ° Двоичная техника и обработка информации, М,, Мир, 1964.

2. Авторское свидетельство СССР

Р 255648 кл. G бб. Р 7/54, 1968.