Гибридное устройство для решения систем дифференциальных уравнений

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз CoaeTcNNx

Социалмстмчвскмк

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 01.0277 (21) 2461521/18-24 с присоединением заявки йо (233 Приоритет

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 150579. Бюллетень йо 18

Дата опубликования описания 150579 (72) Авторы изобретения

N.Í.Êóëèê, А.O.Êðûæàíîâñêàÿ, В.Д.БакуменкО, В.В.Дринь и В.й.Белецкий (71) ЗИявитель

Институт. злектродинамики АН Украинской CCP (54) ГИБРИДНОЕ УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ

ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ

Изобретение относится к области гибридной вычислительной техники и может быть использовано в составе цифровых машин, а также автономно для быстрого решения систем диффе ренциальных уравнений с высокой (цифровой) точностью.

Известно цифровое вычислительйое устройство для решения обыкновенных дифференциальных уравнений, содержащее цифровой автомат, блок синхронизации, коммутатор, согласующий регистр (lj .

Наиболее близким техническим реше" нием к изобретению является гибрид-: ное устройство для решения систем дифференциальных уравнений, содержащее цифровой вычислительный блок, интеграторы, блоки памяти, аналого- 2О вый решающий блок и блок управления (2). недостатком известных устройств является их сложность.

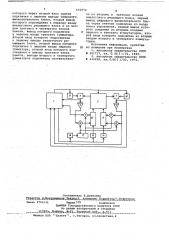

Целью изобретения является упро- 25 щенке устройства. Указанная цель достигается тем, что в устройство введены коммутаторы, счетчик и сумматоры, выход первого сумматора непосредственно подкл-чен к первому уходу цифрового вычислительного блока и через первый интегратор ко второму входу цифрового вычислительного блока и к первым входам первого и второго коммутаторов, выходы которых подключены соответственно к первому и второму входам второго сумматора, третий вход которого через первый блок памяти подключен к первому- выходу цифрового вычислительного блока, третий вход которого подключен к выходу третьего сумматора, соединенного через второй интегратор с четвертым входом цифрового вычислитель ного блока и с первыми входами третьего и четвертого коммутаторов, выходы которых подключены соответственно к первому и второму входам четвертого сумматора, третий вход которого через второй блок памяти подключен к первому выходу цифрового вычислительного блока, второй выход которого подсоединен к первому входу аналогового решающего блока и ко входам третьего и четвертого блоков памяти, выход которого подключен к первому входу третьего сумматора, второй вход которого подсоединен к первому выходу аналогового решающего блока, второй выход которого подключен к первому входу первого сумматора, второй вход которо3 6629 го подсоединен к выходу третьего бло- ка.памяти, выходы второго и четвертого сумматоров подключены соответственно ко второму и третьему, входам налогОвого решающегб блока, первый

ыход цифрового вычислительного блока ереэ счетчик подключен ко входу блока5 управления, первый выход которого соединен со вторыми входами первого и третьего коммутаторов, второй вход которого подключен ко вторым входам второго и четвертого коммутаторов. на чертеже представлена структурная схема гибридного устройства для решения систем дифференциальных уравнений. Устройство содержит цифровой ,вычислительный блок 1, аналоговый 15 решающий блок,2, интеграторы 3, 4, сумматоры 5-8, коимутаторы 9-12, блоки памяти 13-16, блок управления 17 и счетчик 18, Исходная система нелинейных диф- 20 ференциальных уравнений

z = f(z), (О) =Ъ (1) в известном устройстве решается итерационным методом Пикара. йа первой итерации счетчик записывает в триггер единицу, на прямом выходе триггера имеется высокий потенциал, одна группа коммутаторов; подключающих . входы интеграторов к выходам аналогового блока, замыкается. аналоговый решающий блок и интеграторы образуют на первой итерации структуру, которая решает систему уравнения,анало=гичную (1)

У 1(У1) У (о) У о (2) где 1= hhez i

35 (Я- аналоговая (приближенная) реализация нелинейных зависимостей 1(1),У„=М,(Z,, Ь,1; начальные условия, устанавдиваеьйе в интеграторах; ь — погрешность установки начальных условий.

Решение системы (2) и eto производная вводятся в вычислительный цифровой блок, где они демасштабируются: 1= о У1 (3)

-1 о У1 ° (4)

Здесь и далее для простоты мы пред " полагаем, что масштабы по переменным и их производным одинаковы.

Вычислительный цифровой блок с использованием величин (3) > (4) вычисляет невязки (-1 (1) 1 т

50 4 йа второй и последующих итерациях триггер находится в нулевом состоя, нии, входы интеграторов отключены от аналогового решающего блока и подключены через вторую группу коммутаторов к блокам памяти. на второй итерации в блоки памяти записываются функции (7), .в- интеграторах устанавливаются начальные условия (8) и решается таким образом система уравнений ьц,.Ь,=M,(k(z, -zÄ, ьу,(о)=ау, .

1- 1 после чего вычислительный цифровой блок вычисляет новые решения

-" ъ ль (12)

2 (13)

На Н-й итерации решается система

40 где 2 щл (0) = Болите| ) ) . формула (16) описывает метод Пика. ра итерационного решения систем диффаренциальныХ уравнений.

Вычислительный цифровой блок 1

45 осуществляет ввод и вывод информации.

da первой итерации блок управления, выполненный в виде триггера 17, находится в единичном состоянии, на его прямом выходе имеется высокий потенциал, коммутаторы 9 и 11 замкнуты, коммутаторы 10 и 12 разомкнуты. Блоки памяти 13-16 на первой итерации на всем интервале решения выдают на выходах нули. йа первой итерации устройство решает систему (2). Решение системы (2) и его производная вводятся в вычислительный цифровой блок, где они демасштабируются в соответствии с выражениями (3), (4) . Далее вычислительный цифровой блок вычисляет,невязки Я и z,o по формулам (5) и (б) и величины Ь1 и ь $ ю по формулам (7) и (8) . на высших итерациях блок управления 17 находится в нулевом состоянии, коммутаторы 9 и 11 разомкнуты, ком-i (о о Мо Уо „- (6) Далее вычислительный цифровой блок, вычисляет величины

Ъ,-М,E (7) ) Ц,p 1 цР > . (8) где М1- масштаб второй итерации. дУ =И (1(2, I- 1 У„„(0 ) =hA„„(к„-Z, (о)1.

Система (14) может быть решена аналитически, ее решение после демасштабирования имеет вид:

Ь (15) п = о" и о гп т1 1 о где ь z,п,о - погрешность установки на-. чальных условий на итерации.

Ж полняя суммирование типа (12), получаем новое приближение решения:, (16) Ф т * т =,„, Io)+! k(z, 1 "„, 1

662950 (26) 10

25.после чего система (19) приобретает 35 дУ,-Ф, 1д 1, Д (О)-О- (Формула изобретенйя

Гибридное устройство для решения систем дифференциальных уравнений, содержащее цифровой вычислительный .блок, интеграторы, блоки""паМяти, аналоговый решающий блок и блок управления, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, в него введены коммутаторы; счетчик и сумматоры, вйход первого сумматора непосредственно подключен к первому входу цифрового вычислительного блока и через первый интегратор ко второму входу цифрового вычислитель» ного блока и к первым входам первого и второго коммутаторов, выходы кото.Рых подключены соответственно к первому и второму входам второго сумматора, третий вход которого через первый блок Памяти подключен к первому выходу цифрового вычислительного блока, третий вход которого подключен к выходу третьего сумматора соеди.ненного через второй йнтегратор с четвертым входом цифрового вычислительного блока и с первыми входами третьего и четвертого коммутаторов выходы которых подключейы соответственно к первому и второму входам четвертого сумматора, третий вход

Система (21) является линейной, однородной, с нулевыми начальными 40 условиями. Такая система имеет нулевые решения. Таким образом, появле.ние поправок на выходах интеграторов

3 и 4 при решении уравнений (18) вызвано наличием в блоках памяти невя- 45 зок (5), увеличенных масштабом. мутаторы 10 и 12 замкнуты, началь- ные условия в интеграторах 3 и 4 устанавливаются равными

Ч =M1IZо Ч 51(0Я

Величины b1 в соответствии с формулой (7) являются функциями времени, они записываются в блоки памяти 15 и 16.

Кроме того, вычислительный цифровой блок засылает в блоки памяти величины у,**M z

Таким образом, в устройстве решается система уравнений л

ay) y t M)(tin,,1-z )-М ж „ ду =M (-ф- у (0})

Уравнения (18) при йулевых значениях невязок (см.(5)) и начальных условий ду,о (см,(17)) имеют нулевые решения. Действительно, линеаризуя функцию т (у 1 61 ду11, для этого случая получим уравнения ду,-3(g j-М,,pW (5

kgb(OO) = 0 аХ;(ц) . где 1= — матрица Якоби д ч

i функции т (у) .

Учитывая (2), получаем тождество

f(g1 MoZ<=О, (20) i

Поправки щ идц,вводятся в вычислительный цифровой блок, который их демасштабирует в соответствии с формула-. ми (10) и (11) и вычисляет новое при" 50 ближение решения а> и его производную

z2 по формулам (12) и (13) .da атом вторая итерация заканчивается. Последующие итерации проводятся по схеме второй итерации. ° 55 . Hapn -й итерации вычисления ведутся вычислительным цифровым блоком, в блоки памяти 15 и 16 заносятся веляЪ „Мв (1(т щ1-Z ù (22) .в блоки памяти 13 и 14 — величины

У, = Мо Я.m„(23) в интеграторах 3 и 4 устанавливаются. начальные условия о M tzо М у (о)). (24) В устройстве решается система

1 уравнений д у - 1 („, + (Ь,„ду i Ь,„д,„{о) д,„о.(25)

Поправки дн и дн, получаемые на выходах интеграторов 3 и 4 и сумматоров 5 и 7,вводятся в вычислительный цифровой блок, который их де» масштабирует по Формулам

-1 дЬ„, Мв, ду,п

-1 д -М ду (27) и вычисляет (в+1) -ee приближение: решения п,1 =2 т+ Д т (28) и 1 Zpi++Am1 (29)

С увеличением числа итераций ж масштабы М„„ возрастают и поправки (26), (27) уменьшаются по абсолютной величине. Вычисления прекращаются естественным образом, когда невязки п1 то о о 9п(0) превращаются в машинные нули цифрового блока. В этом случае поправки то же будут равны нулю.

Вычисления могут быть прекращены несколько ранее, а именно, при выполнении условия д ) cс(, где са - допустимая погрешность решения.

Использование новых элементов выгодно отличает устройство от известных технических решений..

662950

Составитель И.Дубинина

Редактор Д.Иепуришвили ТехредЛ. АлФерова Корректор О.Ковинская

Заказ 2703/51 Тираж 779 Подписное

ЦдИИПИ Государственного комитета СССР по делам изобретений и открытии

113035 Москва Ж-35 Раушская наб. д.4 5

Филиал ППП Патент, г.ужгород, ул.Проектная,4 которого через второй блок памяти подключен к первому выходу цифровогф вычислительного блока, второй выход которого подсоединен к первому входу аналогового решающего блока и ко входам третьего и четвертого блоков памяти, выход которого подключен 5 к первому входу третьего сумматора, второй вход которого подсоединен к первому выходу аналогового ре шающего блока, второй выход которого подключен к первому входу первого )p сумматора, второй вход которого подсоединен к выходу третьего блока памяти, выходы второго и четвертого сумматоров подключены соответственно ко второму и третьему входам аналогового решающего блока, первый выход цифрового вычислительного блока через счетчик подключен ко входу блока управления, первый выход которого соединен со вторыми входами первого и третьего коммутаторов, второй вход которого подключен ко вторым входам второго и четвертого коммутаторов, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 301717, кл. Cj 06 Ю 1/02, 1969.

2. Авторское свидетельство СССР

9 434428, кл. 5 06 3 1/02, 1972.